Изобретение относится к контрольно-измерительной технике и может быть использовано в производстве полупроводниковых приборов при контроле интегральных логических микросхем, р том числе больших интегральных схем (БИС) преимущественно с отсутствием входного вывода установки микросхем в исходное состояние, содержащих узлы с триггерными элементами, например счетчики, регистры сдвига, делители частоты и др.

Известно устройство для контроля логических микросхем, содержащее клеммы ДЛИ подключения контролируемой и эталонной микросхем, схему сравнения, генератор управляющих синалов и блок индикации l .

Однако известное устройство не позволяет проводить контроль логических микросхем типа счетчиков, делителей частоты, регистров сдвига.

Наиболее близким к предлагаемому является устройство для контроля логических микросхем, содержащее генератор импульсов, триггер результата, соединенный первым и вторым выходами с входами индикатора годности и индикатора брака соответственно, первым входом - с входом устройства, вторым - с выходом блока сравнения, связанного первым и вторым входами через первый и второй преобразователи уровня соответственно с выходами контролируемой и эталонной логических микросхем, соединенных первыми входами с первым и вторым выходами заДатчика входных условий соответственно 2 .

Недостатком такого устройства является ограниченностд области применения, так как оно не позволяет : контролировать микросхемы,, в струк-; туру которых входят узлы. Построенные на триггерных элементах, таких как делители частоты, регистры сдвига и другие, у которых отсутствуют входные выводы установки микросхемы в ноль, что приводит к неопределенности их составления при контроле. Кроме того, в устройстве отсутствует возможность предварительной установки микросхемы в произ- вольно заданное состояние, что необходимо при контроле сквозного переноса функционального узла, состоя щего из нескольких последовательно соединенных счетчиков, например БИС для электронных часов.

Цель изобретения - расширение области применения устройства. :

Поставленная цель достигается .тем, что в устройство для контроля логических микросхем, содержащее генератор импульсов, триггер результата, соединенный первым и вторьш выходами с входами индикатора гоДности и индикатора брака соответственно, первым входом - с входной клеммой устройства, вторым входом 5с выходом блока сравнения, соединенного первым и вторым входами через первый и второй преобразователи уровней соответственно с клеммой для подклк)чения контролируемой

0 логической микросхемы и с выходом эта тонной логической микросхегчы, соединенной первым входом с первым выходом задатчика входных условий, соединенного вторым выходом с первой клеммой для подключения входа I контролируемой логической микросхемы, введены первый и второй анализаторы кода, первый и второй триггеры установки,, первый и второй элементы И-ИЛИ, первый одновибратор и второй одновибратор, соединенный . входом через первый одновибратор с входной клеммой устройства и S-.входами первого и второго триггеров установки, непосредственно - с третьим входом блока сравнения, вы- ходом - с первыми входами первого и второго элементов И-ИЛИ, соединенных вторыми и третьими входами с выходом генератора импульсов, выходами - соответственно с второй клеммой для подключения входа контролируемой логической микросхемы и с вторым.входом эталонной логической микросхемы, четвертыми входами 5 с выходами соответствующих первого и второго триггеров установки, соединенных R-входами с- выходами соответственно первого и второго анализаторов кода,; соединенных входами с выходами соответствующих первого и второго п)реобразователей уровней.

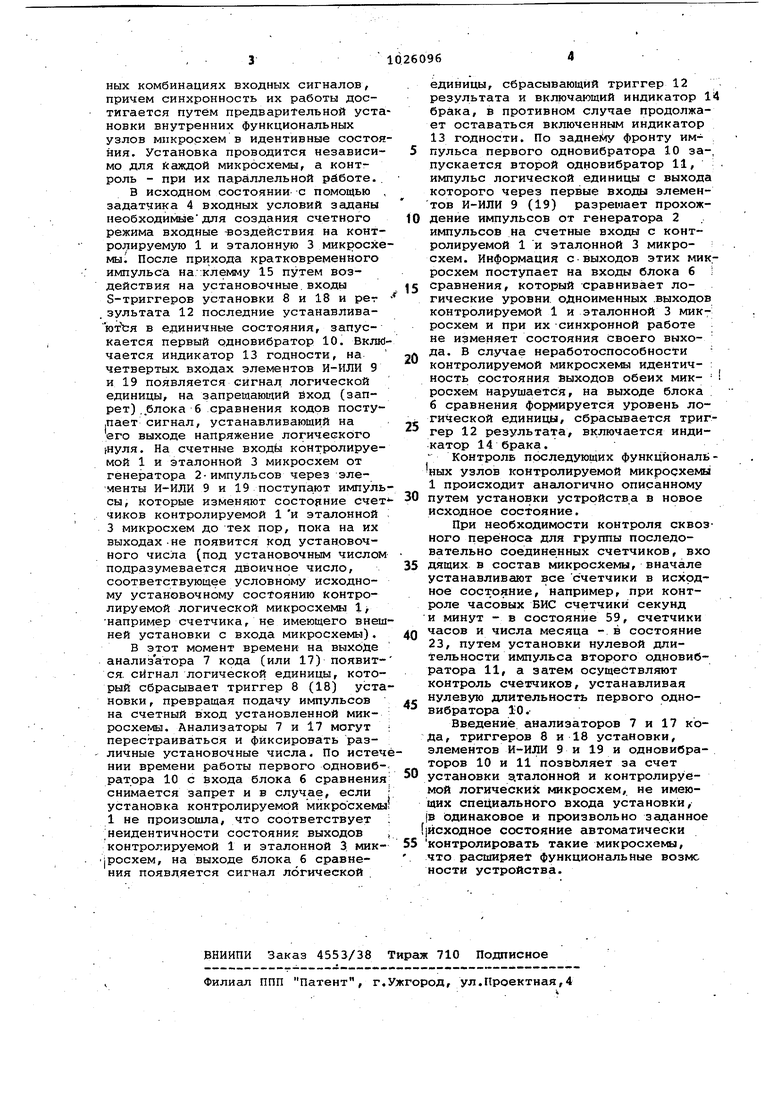

На чертеже показана блок-схема устройства. .

Устройство для контроля логической микросхемы 1 сЬдержит генератор 2 импульсов, эталонную микросхему 3, задатчик 4 входных усло.вий, первый преобразователь 5 уровней, блок б сравнения, первый ана|ЛИзатор 7 кода, первый триггер 8

iустановки, первый элемент 9 It-ИЛИ, первый и в.торой однрвибраторы 10 и 11, триггер 12 результата, индикатор 13 годности, индикатор 14 брака, входную клемму 15, второй преобразователь 16 уровней, второй анализатор 17 кода, второй триггер 18 установки, второй элемент И-ИЛИ 19.

Устройство работает следующим образом.

В устройстве используется принцип сравнения раббты контролируемой логической и эталонной микросхем 1 и 3 соответственно при всех возможных комбинациях входных сигналов, причем синхронность их работы достигается путем предварительной уста новки внутренних функциональных узлов мпкрорхем в идентивные состоя ния. Установка проводится независимо для йаждой микросхемы, а контроль - при их параллельной рйботе. В исходном состоянии с помощью задатчика 4 входных условий заданы необходимыедля создания счетного режима входные -воздействия на контролируемую 1 и эталонную 3 микросхе мы . После прихода кратковременного импульса на :клемму 15 путем воздействия на установочные.входы S-триггеров установки 8 и 18 и per .зультата 12 последние устанавливаютЪя в единичные состояния, запускается первый рдновибратор 10. Вклк чается индикатор 13 годности, на четвертых входах элементов И-ИЛИ 9 и 19 появляется сигнал логической единицы, на запрещающий йход (запрет) ..блока 6 сравнения кодов постулает сигнал, устанавливающий на его выходе напряжение логического нyля. На счетные входы контролируемой 1 и эталонной 3 микросхем от генератора 2-импульсов через элементы И-ИЛИ 9 и 19 поступают импуль сы, которые изменяют состояние счет чиков контролируемой 1 и эталонной 3 микросхем до тех пор, пока на их выходах -не появится код установочного числа (под установочным числом подразумевается двоичное число, соответствующее условному исходному установочному состоянию контролируемой логической микросхемы 1 например счетчика, не имеющего внеш ней установки с входа микросхемы). В этот момент времени на выхйДе анализатора 7 кода (или 17) появится. сигнал логической единицы, который сбрасывает триггер 8 (18) уста новки , превращая подачу импульсов на счетный вход установленной микросхемы. Анализаторы 7 и 17 могут перестраиваться и фиксировать различные установочные числа. По истеч НИИ времени работы первого одновибратрра 10 с Ёхода блока 6 сравнения снимается запрет и в случае, если установка контролируемой микросхемы 1 не произошла, что соответствует неидентичности состояния выходов контролируемой 1 и эталонной 3. мик jpocxeM, на выходе блока 6 сравнения появляется сигнал логической единицы, сбрасывающий триггер 12 результата и включающий индикатор 14 брака, в противном случае продолжает оставаться включенным индикатор 13 годности. По задне111у фронту импульса первого одновибратора 10 за-, пускается второй одновибратор 11, импульс логической единицы с выхода которого через первые входы элементов И-ИЛИ 9 (19) разрешает прохождение импульсов от генератора 2 импульсов на счетные входы с контролируемой 1 и эталонной 3 микросхем. Информация с выходов этих микросхем поступает на входы блока 6 i сравнения, который сравнивает логические уровни одноименных .выходов контролируемой 1 и эталонной 3 микросхем и при их синхронной работе не изменяет состояния своего выхода. В случае неработоспособности контролируемой микросхемы идентич- : ность состояния выходов обеих мик- росхем нарушается, на выходе блока б сравнения фор)иируется уровень логической единицы, сбрасывается триггер 12 результата, включается индикатор 14 брака. Контроль последующих функциональных узлов контролируемой микросхемы 1 происходит аналогично описанному путем установки устройства в новое исходное состояние. При необходимости контроля сквозного переноса для группы последовательно соединенных счетчиков, вхо дящих в состав микросхемы, вначале устанавливают все счетчики в исходное состояние, например, при контроле часовых БИС счетчики секунд и минут - в состояние 59, счетчики часов и числа месяца - в состояние 23, путем установки нулевой длительности импульса второго одновибратора 11, а затем осуществляют контроль счетчиков, устанавливая нулевую длительность первого одновибратора 1-0. Введение анализаторов 7 и 17 кода, триггеров 8 и 18 установки, элементов И-ИЛИ 9 и 19 и одновибраторов 10 и 11 позвЬляет за счет установки эталонной и контролируемой логических микросхем, не имеющих специального входа установки, IB одинаковое и произвольно заданное |йсходное состояние автоматически контролировать такие микросхемы, что расширяет функциональные возмс ности устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1067453A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для контроля КМОП-логических схем | 1987 |

|

SU1552137A1 |

| Устройство для контроля цифровых интегральных микросхем | 1987 |

|

SU1501062A2 |

| Устройство для контроля логических блоков | 1984 |

|

SU1256032A1 |

| Логический пробник | 1983 |

|

SU1112327A1 |

| Устройство для определения нагрузочной способности микросхем | 2017 |

|

RU2649244C9 |

| Устройство для определения нагрузочной способности микросхем | 2019 |

|

RU2723968C1 |

| Устройство сигнатурного контроля проводных соединений | 1986 |

|

SU1385105A1 |

УСТРОЙСТВО ДЛЯКОНТРОЛЯ ЛОГИЧЕСКИХ МИКРОСХЕМ, содержащее генератор импульсов, триггер результата/ соединенный первым и вторым выходами с Входами индикатора годности и индикатора брака соответственно, первым входом - с входной клеммой устройства, вторым входом с выходом блока сравнения, соединенноро первым и вторым входами через первый И второй преобразователи уровней соответственно с клеммой для подключения .контролируемой логической микросхемы и с выходом эталонной логической микросхемы, соединенной первым входе с первым выходрм задатчика входных условий, соединённого вторым выходом с первой клеммой для подключения входа ..: контролируемой логической микросхемы, отличающееся тем,. что, с целью расширения области применения устройства, в него введены первый и второй анализаторы кода, первый и второй триггеры уста новкй, первый и второй элементы И-ИЛИ, первый одновибратор и второй одновибратор, соединенный входом через первый одновибратор с входной клеммой устройства и S-вхрдами первого и второго триггеров установки, непосредственно - с третьим входом блока сравнения, выходом - с первыми входами.первого и второго элементов И- ИЛИ, соединенных вторыми Щ и третьими входами с выходом генератора И1утульсов, выходами - соответственно с второй клеммой для подключения входа контролируемой логической микросхемы и с вторь м входом эталонной логической микросхемы, четвертыми входа1 и - с выходами соответств уюпих первого и второго триггеров установки, соединенных R-входами с выходами соответстIsD венно первого и второго анализаторов кода, соединенных входами с выа ходами соответствующих первого и BTopofo преобразователей уровней. со о:

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для обнаружения неисправностей в логических схемах | 1971 |

|

SU441532A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1983-06-30—Публикация

1982-03-26—Подача