1

Изобретение относится к электроизмерительной технике и может использоваться в устройствах контроля и диагностики неисправностей элементов радиоэлектронной аппаратуры.

Известны устройства, содержащие эталонную интегральную схему, многоконтактный зонд, элементы сравнения, элементы свертки, индикаторы несравнения, блок запуска, блок индикации запуска и блоки установки 1.

Однако такие устройства не выдают информацию о том, произошли ли в процессе контроля переключения на входах и выходах эталонной интегральной схемы.

Наиболее близким по технической сущности к предлагаемому является устройство для автоматического контроля интегральных схем, содержащее многоконтактный зонд, эталонную интегральную схему, блоки сравнения, элемент И, триггер, кнопку сброса и индикатор наличия неисправности 2.

Недостаток этого устройства -, . также низкая достоверность контроля.

Цель изобретения - повышение достоверности контроля.

Это достигается тем, что в устройство, содержащее многоконтактный зонд, соответствующие входные контакты которого соединены с входами эталонной интегральной схемы, а его соответствующие выходные контакты соединены с входами контролируемой интегральной схемы, выходы которой соединены с другими выходными контактами

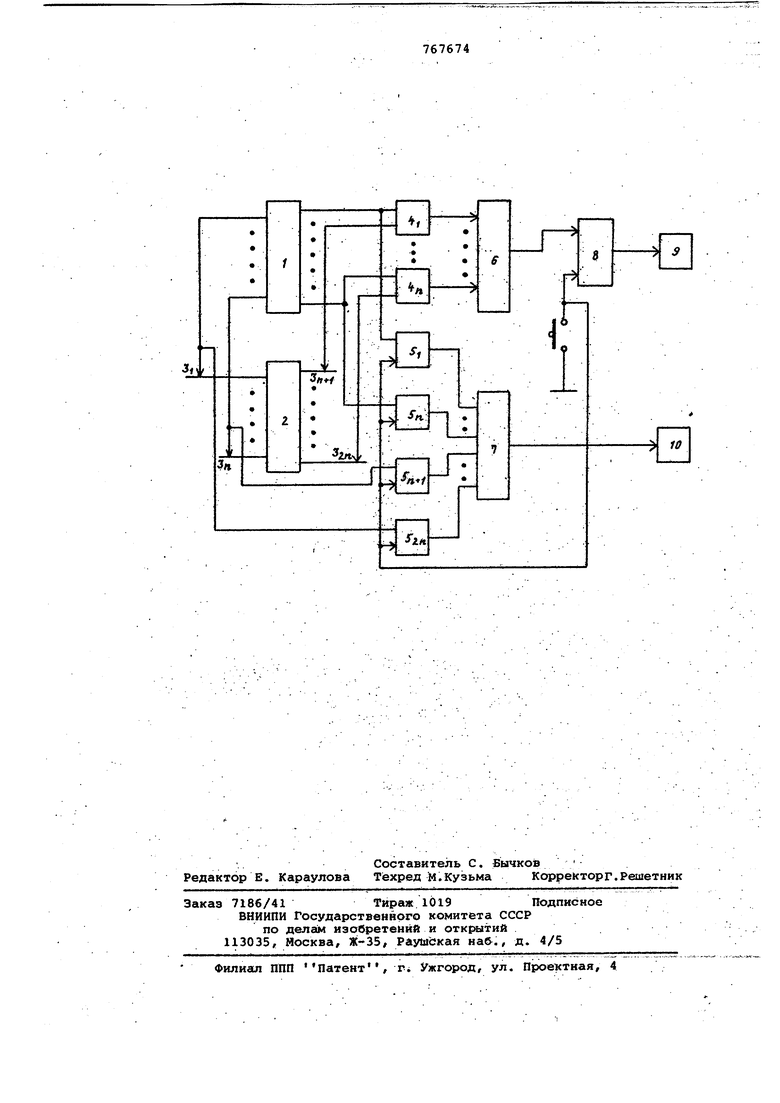

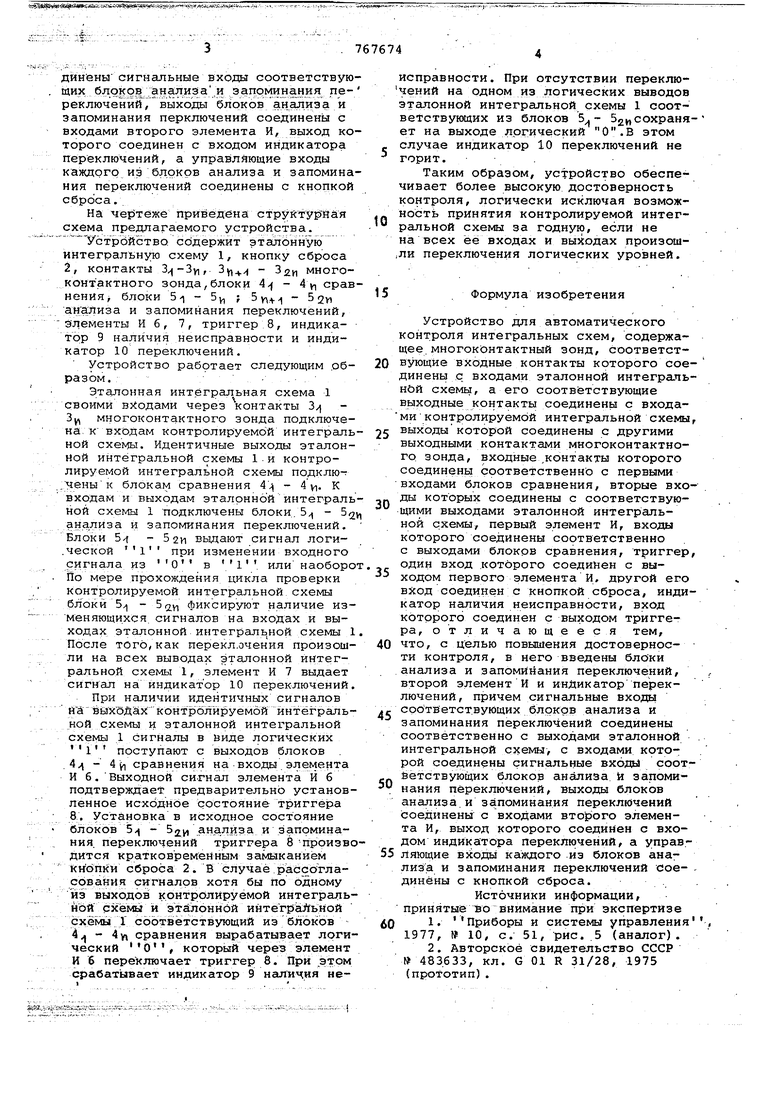

10 многоконтактного зонда, входные контакты которого соединены соответственно с первыми входами блоков сравнения, вторые входы которых соединены с соответствующими выходами эталонной интегральной схемы, первый элемент И, входы которого соединены соответственно с выходами блоков сравнения, триггер, один вход которого соединен с выходом первого элеменiZO та и, другой его вход соединен с кнопкой сброса, индикатор наличия неисправности, вход которого соединен с выходом триггера, введены блоки анализа и запоминания переключений, второй элемент И и индикатор переключений, причем сигнальные входы соответствующих блоков анализа и запоми. нания переключений соединены соответственно с выходами эталонной интегральной схемы, с входами которой соединены сигнальные входы соответствую щих блоков анализаи запоминания переключений, выходы Олоков адализа и запоминания перключений соединены с входами второго элемента И, выход ко торого соединен с входом индикатора переключений, а управляющие входы каждого из блоков анализа и запомина ния переключений соединены с кнопкой сброса. На чегЗтёже приведена структу Ная схема предлагаемого устройства. Устрбйство содержит эталонную интегральную схему 1, кнопку сброса 2, контакты , 3 - Зги многоконтактного зонда,блоки 4 - срав нения j блоки 5i - 5 У - 52м анализа и запоминания переключений, элементы И б, 7, триггер 8, индикатор 9 наличия неисправности и индикатор 10 переключений. Устройство работает следующим образом. . . Эталонная интегральная схема 1 своими входами через контакты З/i ЗУ, многоконтактного зонда подключена, к входам Контролируемой интеграль ной схемы. Идентичные выходы эталон ной интегральной схемы 1.и контролируемой интегральной схемы подклю.;ченык блокам сравнения 4 - 4у|. К входам и выходам эталонной интеграл ной схемы 1 подключены блоки/Б - З анализа и запоминания переключений. Блоки Sf - 52И выдают сигнал логи.ческой 1 при изменении входного или наобор сигнала из Йо мере прохождения цикла проверки контролируемой интегральной.схемы блоки 5.( - фиксируют наличие из меняющихся сигналов на входах и выходах эталонной интеграль ной схемы После того, как перекл.очения произош ли на всех выводах эталонной интегральной схемы 1, элемент И 7 выдает сигнал на индикатор 10 переключений При наличии идентичных сигналов йЖ йЫхоДах контролируемой интеграль ной схемы и эталонной интегральной схемы 1 сигналы в виде логических поступают с выходов блоков 4 - 4 ( сравнения на входы элемента И 6.Выходной сигнал элемента И 6 подтверждает предварительно установ ленное исходное состояние триггера 8. Установка в исходное состояние блоков 5 - анализа запоминания, переключений триггера 8 Произв дится кратковременным замыканием Кнопки сброса 2. В случае рассотласования сигналов хотя бы по одному из выходов контролируемой интеграль ной схемы и эталонной интегральной схемы Г соответствующий из блоков 4 - 4у( сравнения вырабатывает логи ческий О, который через элемент И б переключает триггер 8. При .этом срабатывает индикатор 9 наличия не767674исправности. При отсутствии переключений на одном из логических выводов эталонной интегральной схемы 1 соответствующих из блоков 52исохраняет на выходе логический О.В этом случае индикатор 10 переключений не горит. . Таким образом, устройство обеспечивает более высокую достоверность контроля, логически исключая возможность принятия контролируемой интегральной схемы за годную, если не на всех её входах и выходах произошли переключения логических уровней. Формула изобретения Устройство для автоматического контроля интегральных схем, содержащее многоконтактный зонд, соответствующие входные контакты которого соединены q входами эталонной интегральн&й схемы, а его соответствующие выходные контакты соединены с входами контролируемой интегральной схемы, выходы которой соединены с другими выходными контактами многоконтактного зонда, входные .контакты которого соединень соответственно с первыми входами блоков сравнения, вторые входы которых соединены с соответствующими выходами эталонной интегральной схемы, первый элемент И, входы которого соединены соответственно с выходами блоков сравнения, триггер, один вход которого соединен с выходом первого элемента И. другой его вход соединен с кнопкой сброса, индикатор наличия неисправности, вход которого соединен с выходом триггера, отличающееся тем, что, с целью повышения достоверное- ти контроля, в него введены блоки анализа и запоминания переключений, ,. второй элемент И и инДикатор переключений, причем сигнальные входьз соответст.вующих блоков анализа и запоминания переключений соединены соответственно с выходами эталонной интегральной схемы, с входами которой соединены сигнальные входы соотВетствую1цих блоков анализа и запоминания переключений, выходы блоков анализа.и запоминания переключений соединены с входсции второго элемента И, выход которого соединен с входом индикатора переключений, а управ.ляющие каждого из блоков анализа и запоминания переключений соединены с кнопкой сброса. . Источники информации, принятые во внимание при экспертизе Приборы и системы управления , 1977, 10, с. 51, рис. 5 (аналог). 2. Авторское свидетельство СССР №483.633, кл. G 01 R 31/28, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля неисправностей интегральных схем | 1980 |

|

SU1083138A1 |

| Устройство для контроля цифровых интегральных микросхем | 1985 |

|

SU1265663A1 |

| Устройство для контроля интегральных микросхем | 1982 |

|

SU1056089A1 |

| Устройство для диагностики неисправностей логических блоков | 1987 |

|

SU1520548A1 |

| Устройство для диагностики цифровых узлов | 1982 |

|

SU1071979A1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для контроля блоков постоянной памяти | 1983 |

|

SU1104590A1 |

| Устройство для контроля интегральных микросхем | 1978 |

|

SU708269A1 |

| Устройство для проверки исправности сигнальных ламп | 1983 |

|

SU1164762A1 |

Авторы

Даты

1980-09-30—Публикация

1978-05-31—Подача