00

о

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик импульсов в р-кодах Фибоначчи | 1987 |

|

SU1443168A1 |

| Счетчик импульсов в минимальных Р-кодах Фибоначчи | 1991 |

|

SU1786657A1 |

| Модуль пересчетной схемы в минимальном Р-коде Фибоначчи | 1988 |

|

SU1511862A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1988 |

|

SU1531215A1 |

| Кольцевой счетчик | 1985 |

|

SU1298905A1 |

| Кольцевой счетчик | 1987 |

|

SU1437995A2 |

| Кольцевой счетчик | 1988 |

|

SU1538250A1 |

| Счетчик импульсов | 1985 |

|

SU1298904A1 |

| Кольцевой счетчик | 1981 |

|

SU1005319A1 |

| Реверсивный кольцевой счетчик | 1980 |

|

SU919092A1 |

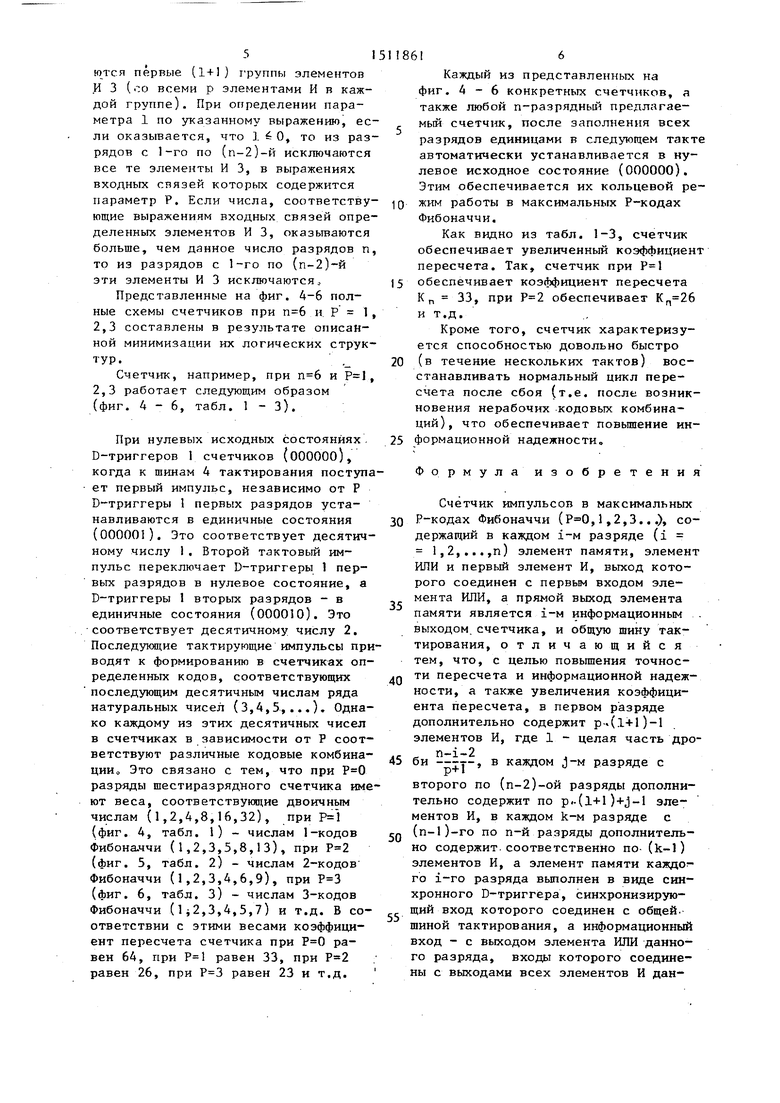

Изобретение относится к вычислительной технике и может быть использовано для кольцевого пересчета импульсов в максимальных Р-кодах Фибоначчи. Цель изобретения - повышение точности пересчета в максимальных Р-кодах Фибоначчи, увеличение коэффициента пересчета и повышение информационной надежности путем обеспечения кольцевого режима пересчета в этих кодах. Устройство содержит в каждом I - м разряде (I=1,2,...,N) элемент памяти, элемент ИЛИ, первый элемент И и общую шину тактирования. Для достижения цели в первом разряде дополнительно содержит P(L+1)-1 элементов И, где L - целая часть дроби N-I-2/P+1, в каждом J - м разряде со 2-го по (N-2)- й - P(L+1)+J-1 элементов И, в каждом к-м разряде с (N-1) - го по N - й-(K-1) элементов И, а элемент памяти каждого I - го разряда выполнен в виде синхронного Д-триггера, синхронизирующий вход которого соединен с общей шиной тактирования, а информационный вход - с выходом элемента ИЛИ данного разряда, подключенного своими входами к выходам всех элементов И данного разряда, а в первом разряде - также к инверсному выходу Д-триггера первого разряда. 6 ил., 3 табл.

Изобретение относится к вычислительной технике и может быть использовано для кольцевого пересчета импульсов в максимальных Р-кодах Фибоначчи при любых значениях Р 0,1,

/,J,Q...

Цель изобретения - повышение точности пересчета в максимальных Р-кодах Фибоначчи и увеличение коэффициента пересчета а также повышение информационной надежности за счет

обеспечения кольцевого режима пересчета в этих кодах.

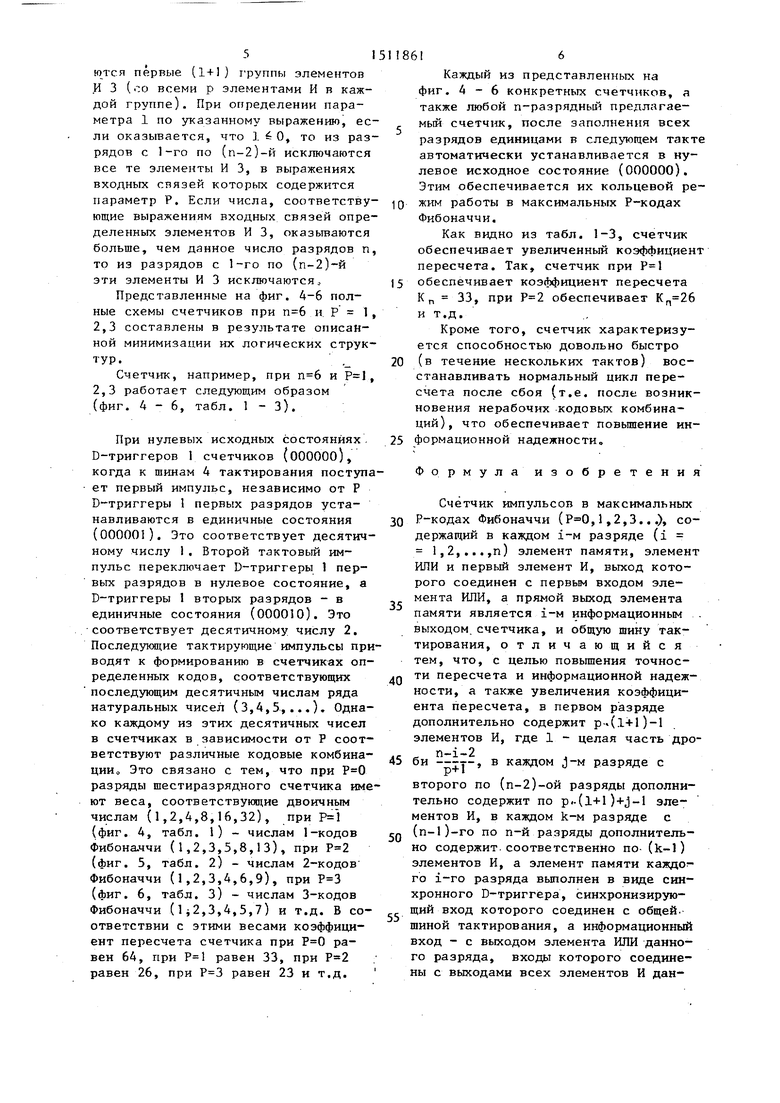

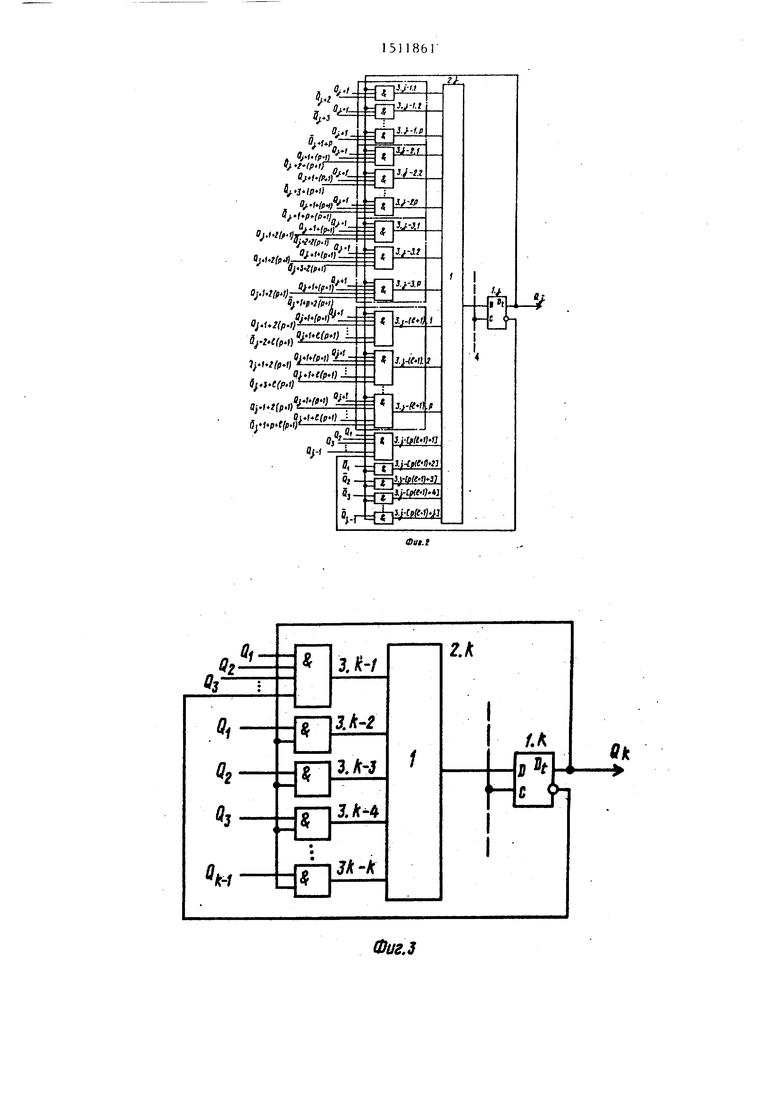

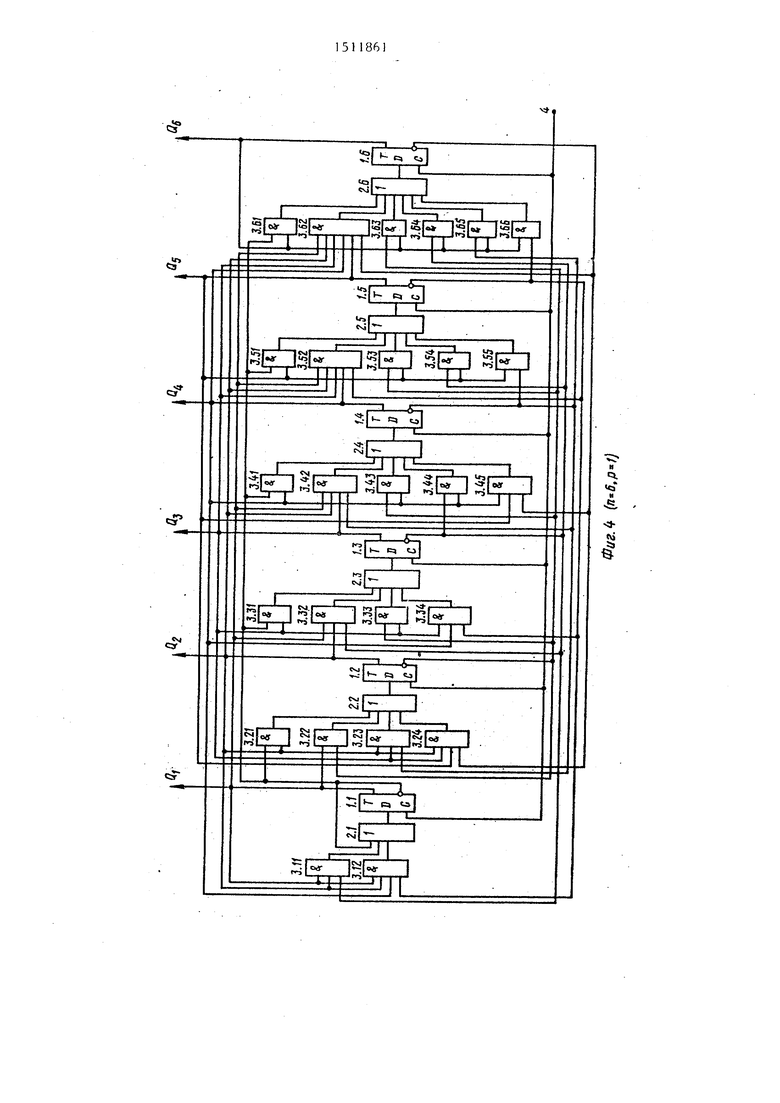

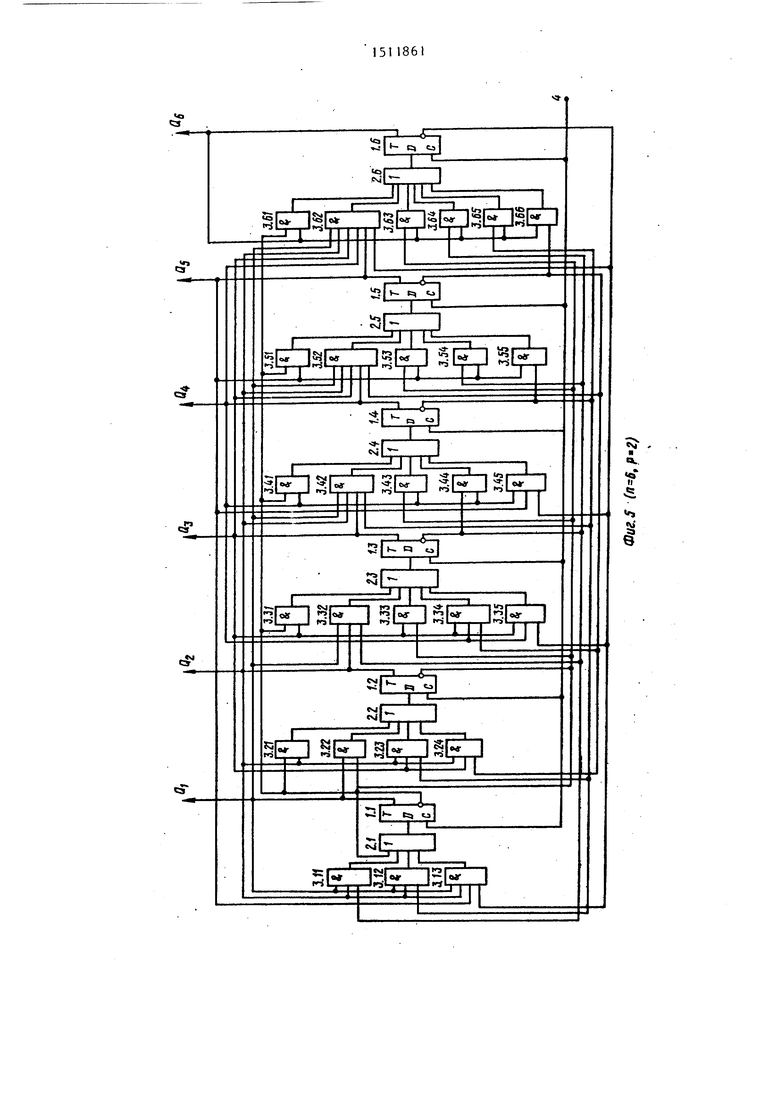

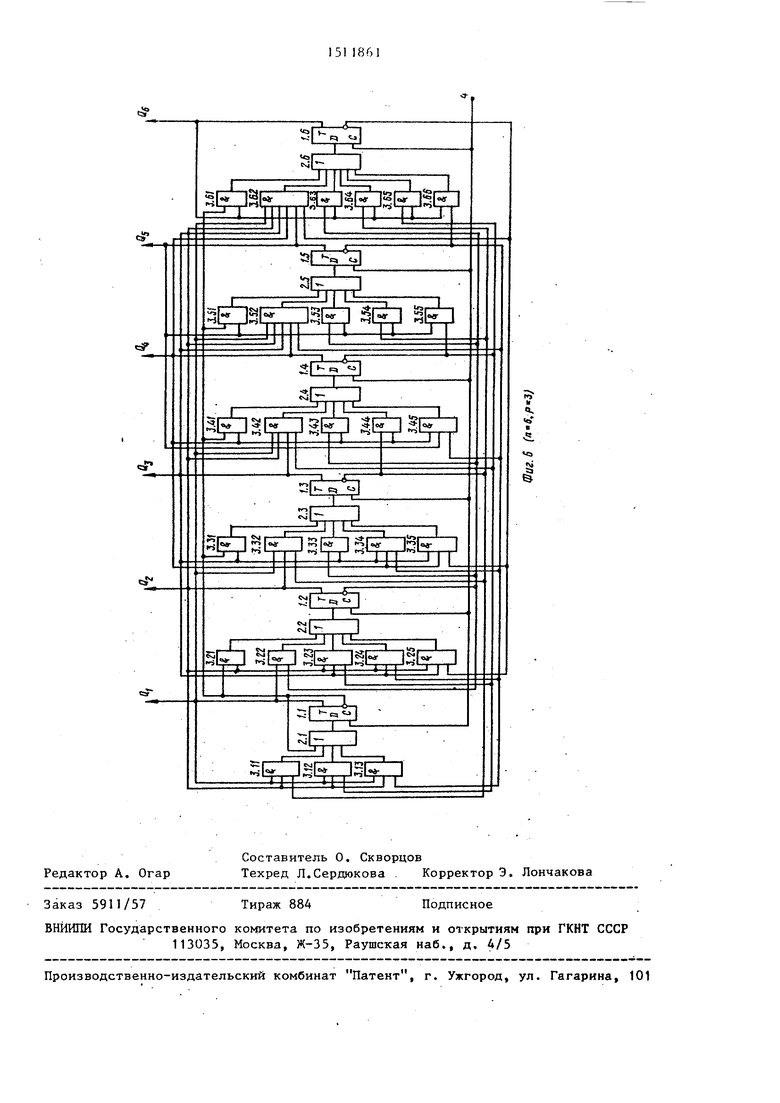

На фиг..1-3 представлены функциональные схемы соответственно первого разряда, с второго по (п-2)-й разрядов и с (n-l)-ro по п-й разря- дов предлагаемого п-разрядного коль цевого счетчика импульсов в максимальных Р-кодах Фибоначчи; на фиг. 4- 6 - функциональные схемы шестиразряд5

31511861

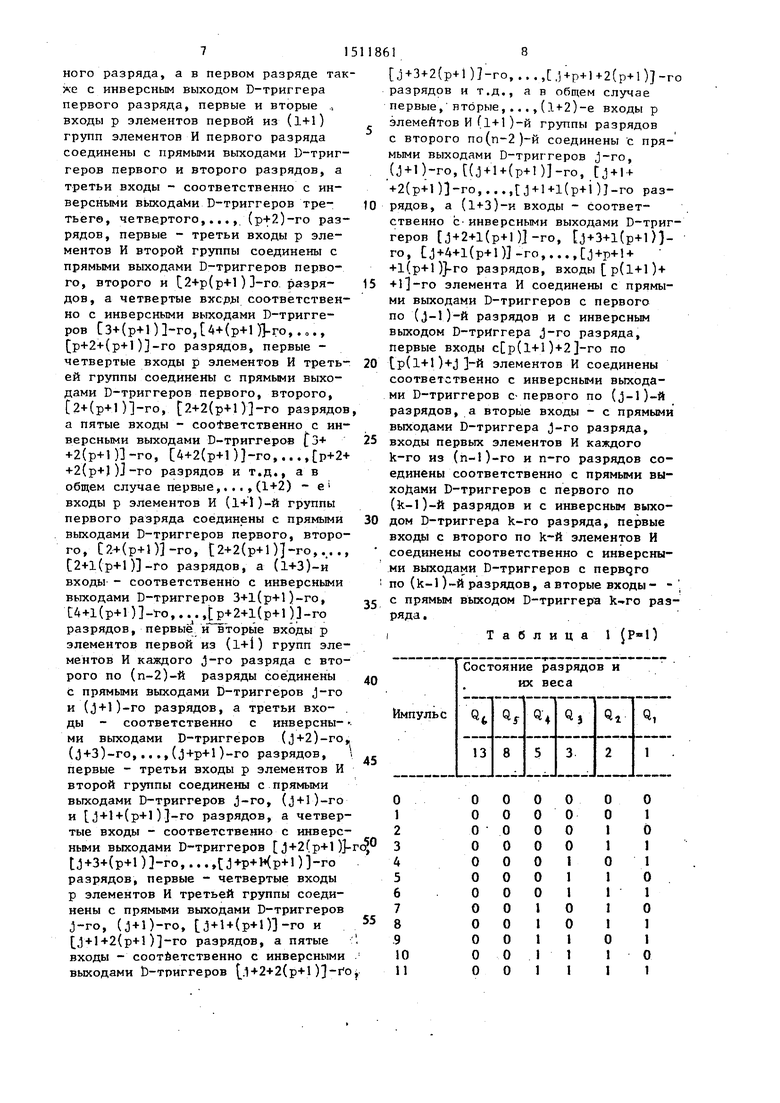

ых счетчиков соответственно при 1, Р 2, Р Зо

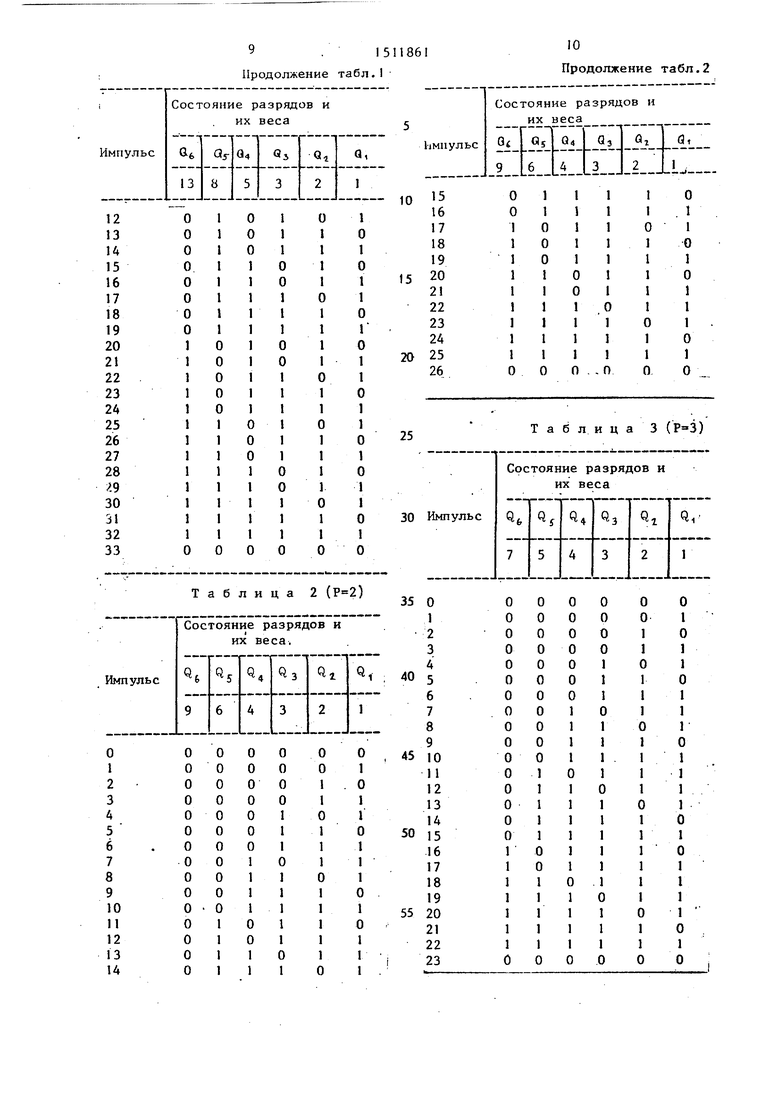

Коды пересчета шестиразрядных четчиков сведены в соответствующие абл, 1-3.

Предлагаемый счетчик импульсов максимальных г -кодах Фибоначчи соержит в каждом i-M разряде (фиг. 1- ) D-триггер l,.i, элемент ИЛИ 2Л, ю ыход которого подключен к информаионному входу D-триггера 1.i, элеенты И 3оi, выходы которых соединены с входами элемента ИЛИ 2.1. Синронизирующие входы всех D-тригге- 15 ров 1 подключены к шине 4 тактирования.

В первом разряде (фиг. I) общее число элементов И 3 равно p(l+l). Первый вход элемента ИЛИ 2.1 соеди- 20 нен с инверсным выходом D-триггера 1.1, 1-е и 2-е входы р элементов первой из (l+l) групп элементов И 3 первого разряда соединены .с прямыми выходами триггеров D1.1 и D1.2, а . 25 3-й входы - соответственно с инверсными выходами триггеров DI.3, Dl,4, ...,Dl.(p+2), 1-е, 2-е и 3-й . входы р элементов И 3 второй группы соединены с прямыми выходами тригге- 30 ров D1.1, Dl,2 и Dl,t2-fp (р+1)1, а 4-е входы - соответственно с инверсными выходами триггеров D1. t 3+

+ (р-и), D1. (р+ОЬ..., D1. .

(;p+2+(p+l)i 1-е, 2-е, 3-й и 4-е вхо- 35 ды р элементов И 3 третьей группы соединены с прямыми выходами триггеров D1.1, D1.2, D1. 2+(p+l)j. и D1. t2+2(p4-l)J, а 5г-е входы - соответственно с инверсными выходами .40 триггеров D1. С 3+2 (р+1), D1.4+ (р+1),..., D1.Ср+2+2(р+1) и т.д. А в общем случае 1-е, 2-е, 3-й,..,, (l+2)-e входы р элементов И 3 (l+l)-и группы первого разряда соединены с прямыми выходами триггеров D1.1, Dlo2, D1. Г 2+(р+1), D1. 2+2(р+1)Т, ..., D1. 2+l(p+l)j, а (1+3)-и вх8- ды - соответственно с инверсными выходами триггеров D1. С3+1(р+1)3, - D1. 4+1(р+1),... ,D1 .Ср+2+1(р+1).

В разрядах с второго по (п-2)-й (фиг. 2) 1-е и 2-е входы р элементов первой из (1+1) групп элементов И 3 каждого J-ro разряда соединены с пря-, мыми выходами триггеров D1.J и Dl.(j-H), а 3-й входе.1 - соответственно с инверсными выходами триггеров Dl.(j+2), Dl.(j+3)Dlc(j+

5

0 5 0

5 0

+Р+1), 1-е, 2-е и 3-й входы р элементов И 3 второй группы соединены с прямыми выходами триггеров Dl.j, Dl.(j + l) и + l + (p+l) , а 4-е входы - соответственно с инверсными выходами триггеров Dl.J+2(p+l),

Dl.j+3(p+l)Dl.j+p+l+(p+l)j,

1-е, 2-е, 3-е и 4-е входы р элементов И 3 третьей группы соединены с прямыми .выходами триггеров DloJ, D1.(J+1), DI.J + l + (p+l) H.D1.J + +l+2(p+l), a 5-e входы - соответственно с инверсными выходами триггеров Dl.Cj+2+2(p+l) , Dl.tj+3+ +2(р+1) ,...,Dl.j+p+r+2(p+l )1ит.д. А в общем случае 1-е, 2-е, 3-й,..., (l+25-e входы р элементов И (1+1)-й группы соединены с прямыми выходами триггеров D1.J, Dl.(j + l), Dl.p + l + + (р+1) , Dl,tj + l+2(p+l),...,bLCj + +l+l(p+l), a (1+3)-и входы - соответственно с инверсными выходами триггеров D1. У+2+1(р+1) , Dr.i;j+3+ +1(р+1) , D1 .tJ+A+l(p+l)i,... ,bl. J+ +p+I+l(p+l).

Входы p(l+l) элемента И 3 соединены с прямыми выходами триггеров D1.1-D1о 1(j-1) и с инверсным выходом триггера Первые входы с р(1+1) по p( элементов И 3 соединены соответственно с инверсными выходами триггеров Di.1-D1.(j-1), а вторые входы - с прямым выходом триггера Dl.j.

Входы первых элементов И 3 каждого к-го разряда из (n-l)-ro и п-го разрядов (фиг, 3) соединены соответственно с прямыми вь(ходами D-тригге-. ров 1 с первого по (К-1)-й разрядов и с инверсным выходом D-триггера 1 k-ro разряда. Первые входы с второго по k-й элементов И 3 соединены соответственно с инверсными выходами D-триггеров I с первого по (k-l)-ro разрядов, а вторые входы - с прямым выходом D-триггера k-ro разряда.

В процессе составления логической структуры предлагаемого счетчика при некоторых конкретных случаях, с определенными значениями параметров Р, 1 и п, возможна минимизация чис. ла логических элементов.

Так, например, при Р О из первого ряда счетчика (фиг. 1) с любым числом разрядов п исключаются все элементы И 3 и элемент ИЛИ 2, а из. разрядов с 2-го по (п-2)-й нсключа.51

ютсл первые (1+1) группы элементов И 3 (оо всеми р элементами И в каждой группе). При определении параметра 1 по указанному выражению, если оказывается, что , то из разрядов с 1-го по (п-2)-н исключаются все те элементы И 3, в выражениях входных связей которых содержится параметр Р. Если числа, соответствующие выражениям входных связей определенных элементов ИЗ, оказьгоаются больше, чем данное число разрядов п, то из разрядов с 1-го по (п-2)-й эти элементы И 3 исключаются,

Представленные на фиг. 4-6 полные схемы счетчиков при и Р 1, 2,3 составлены в результате описанной минимизации их логических структур.

Счетчик, например, при и , 2,3 работает следующим образом (фиг. 4-6, табл. 1-3).

При нулевых исходных состояниях . D-триггеров 1 счетчиков (ОООООО), когда к шинам 4 тактирования поступает первый импульс, независимо от Р D-триггеры 1 первых разрядов устанавливаются в единичные состояния (000001). Это соответствует десятичному числу 1. Второй тактовый импульс переключает D-триггеры 1 первых разрядов в нулевое состояние, а D-триггеры 1 вторых разрядов - в единичные состояния (ООООЮ). Это соответствует десятичному числу 2. Последукицие тактирующие импульсы приводят к формированию в счетчиках определенных кодов, соответствующих последующим десятичным числам ряда натуральных чисел (3,4,5,...). Однако каждому из этих десятичных чисел в счетчиках в зависимости от Р соответствуют различные кодовые комбина- циИо Это связано с тем, что при разряды шестиразрядного счетчика имеют веса, соответствующие двоичньгм числам (1,2,4,8,16,32), при (фиг. 4, табл. О - числам 1-кодов Фибоначчи (1,2,3,5,8,13), при (фиг. 5, табл. 2) - числам 2-кодов Фибоначчи (1,2,3,4,6,9), при (фиг. 6, табл. 3) - числам 3-кодов Фибоначчи (1i2,3,4,5,7) и т.д. В соответствии с этими весами коэффициент пересчета счетчика при равен 64, при равен 33, при равен 26, при равен 23 и т.д.

118616

Каждый из представленных на фиг. 4-6 конкретных счетчиков, а также любой п-разрядньй предлагаемый счетчик, после заполнения всех разрядов единицами в следующем такте автоматически устанавливается в нулевое исходное состояние (ОООООО). Этим обеспечивается их кольцевой ре10 жим работы в максимальных Р-кодах Фибоначчи.

Как видно из табл. 1-3, счетчик обеспечивает увеличенный коэффициент пересчета. Так, счетчик при

15 обеспечивает коэффициент пересчета К г, 33, при обеспечивает К 26 и т.д.

Кроме того, счетчик характеризуется способностью довольно быстро

20 (в течение нескольких тактов) восстанавливать нормальный цикл пересчета после сбоя (т.е. после возникновения нерабочих кодовых комбинаций), что обеспечивает повьшение ин25 формационной надежности.

Формула изобретения

Счётчик импульсов в максимальных 30 Р-кодах Фибоначчи (,1,2,3...), содержащий в каждом i-M разряде (i 1,2,...,п) элемент памяти, элемент ИЛИ и первый элемент И, выход которого соединен с первым входом элемента ИЛИ, а прямой выход элемента памяти является i-н информационным выходом, счетчика, и общую шину тактирования, отличающийся тем, что, с целью повышения точнос- ,Q ти пересчета и информационной надежности, а также увеличения коэффициента пересчета, в первом разряде дополнительно содержит р-.(.1+1)-1 элементов И, где 1 - целая часть дро.- , n-i-2 .

45 би -7Т- в каждом J-M разряде с

второго по (п-2)-ой разряды дополнительно содержит по p.-(l+l)+j-l элементов И, в каждом k-M разряде с CQ (n-l)-ro по п-й разряды дополнительно содержит.соответственно по- (k-1) элементов И, а элемент памяти каждо го i-ro разряда выполнен в виде синхронного D-триггера, синхронизирующий вход которого соединен с общей.- шиной тактирования, а информационный вход - с выходом элемента ИЛИ данного разряда, входы которого соединены с выходами всех элементов И дан

ного разряда, а в первом разряде также с инверсным выходом D-триггера первого разряда, первые и вторые . входы р элементов первой из (l+l) групп элементов И первого разряда соединены с прямыми выходами D-триг- геров первого и второго разрядов, а третьи входы - соответственно с инверсными выходами D-триггеров тре- тьеге, четвертого,.,., ()-го разрядов, первые - третьи входы р элементов И второй группы соединены с прямыми выходами D-триггеров первого, второго и 2+р(р+1)3-го разрядов, а четвертые вхсря соответственно с инверсными выходами D-триггеров 3+(р+1)-гоД4+(р+1)-го,.,., р+2+(р+1)}-го разрядов, первые - четвертые входы р элементов И третьей группы соединены с прямыми выходами D-триггеров первого, второго, 2+(р+1)1-го, 2+2(р-1-1)-го разрядов а пятые входы - cootBeTCTseHHo с инверсными выходами D-триггеров 3+ +2(р+1)-го, 4+2(р+1)-го,...,р+2+ +2(р+))-го разрядов и т.д., а в общем случае первые,...,(1+2) - е входы р элементов И (1+1)-й группы первого разряда соединены с прямыми выходами D-триггеров первого, второго, C.+ (p+l)j-ro, t2+2(p+l)-ro,... ., C2+l(p+l)-го разрядов, а (1+3)-и входы - соответственно с инверсными выходами D-триггеров 3+1(р+1)-го, С4+1(р+1 )-То,. .. ,+2+1(р+1 )-го разрядов, первые йТторые входы р элементов первой из (1+1) групп элементов И каждого j-ro разряда с второго по (п-2)-й разряды соединены с прямыми выходами D-триггеров J-ro и (j+l)-ro разрядов, а третьи вхо- ды - соответственно с инверсны- ми выходами D-триггеров (j+2)-ro (j+3)-ro,...,(j+p+l)-ro разрядов, первые - третьи входы р элементов И второй группы соединены с прямыми выходами D-триггеров J-ro, (j+l)-ro и J+l+(p+l)-го разрядов, а четвертые входы - соответственно с инверсными выходами D-триггеров J+2(p+l )} tJ+3+(p+l) 1-го,...,tJ+p+Kp+1) 1-го разрядов, первые - четвертые входы р элементов И третьей группы соединены с прямыми выходами D-триггеров j-ro, (j + l)-ro, j + l + (p+01-ro и j+l+2(p+l )-го разрядов, а пятые входы - соответственно с инверсными выходами D-триггеров .1+2+2(р+1 )-г

0

5

0

5

0

5

j + 3+2(p+l)-ro,...,,5+p+l+2(p+l)-ro разрядов и т.д., а в общем случае первые, вторые, ..., (l+-2)-e входы р элемеАтов И(l+l)-й группы разрядов с второго по(п-2)-й соединены с прямыми выходами D-триггеров J-ro, (j + O-ro, (j + l+(p+l )-го, CJ + 1 + +2(p+l)-ro,...,J+l+l(p+i)-ro разрядов, а (1+3)-и входы - соответственно с- инверсными выходами D-триггеров j + 2+l(p+l)j-ro, tj+3+l(p+l)}- го, Cj+4+l(p+l)-ro,...,J+p+l + +l(p+l)J-ro разрядов, входы p(l+l) + +11-ГО элемента И соединены с прямыми выходами D-триггеров с первого по (-1)-й разрядов и с инверсным выходом D-трИггера J-ro разряда, первые входы сСр(1+1) по tp(l+l) элементов И соединены соответственно с инверсными выходами D-триггеров с- первого по (J-l)-й разрядов, а вторые входы - с прямыми выходами D-триггера J-ro разряда, входы первых элементов И каждого k-ro из (п-)-го и п-го разрядов соединены соответственно с прямыми выходами D-триггеров с первого по (k-l)-й разрядов и с инверсным выходом D-триггера k-ro разряда, первые входы с второго по k-й элементов И соединены соответственно с инверсными выходами D-триггеров с первдго по (k-1 )-й разрядов, а вторые входы- - . с прямым выходом D-триггера k-гго разряда.

IТаблица 1(

О

1

2

3

4

5

6

7

8

.9

10

11

Продолжение табл. I

10 Продолжение табл.2

4+2/p f;

( )

2+3fp /;

Оз

+2

2+3fP+f

«

2+21 ()

Фиг.З

и с.

«Г

н

5 СЗ|

I I I I I o -T-i- .ri -i-r o-Ц-г- ЧРедактор А. Огар

Составитель О, Скворцов

Техред Л.Сердюкова . Корректор Э, Лончакова

Заказ 5911/57

Тираж 884

ВНЙИПИ Государственного кокштета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

|« ч.

«о

и

«S

Подписное

| СПОСОБ ОПРЕДЕЛЕНИЯ НЕЗАВИСИМЫХ СОСТАВЛЯЮЩИХ МАТРИЦЫ ЖЕСТКОСТИ ОРТОТРОПНОГО МАТЕРИАЛА | 0 |

|

SU377682A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-30—Публикация

1988-02-29—Подача