Изобретение относится к импульсной технике и может быть использовано для многоразрядного пересчета импульсов в минимальном коде 1мбоначчи при любом значении Р 1,2,3,..., с возможностью наращивания разрядности по Р-1-2.

Цель изобретения - расширение функциональных возможностей и области применения путем обеспечения пересчета в Р-кодах Фибоначчи, где Р 1,2, 3,4,....

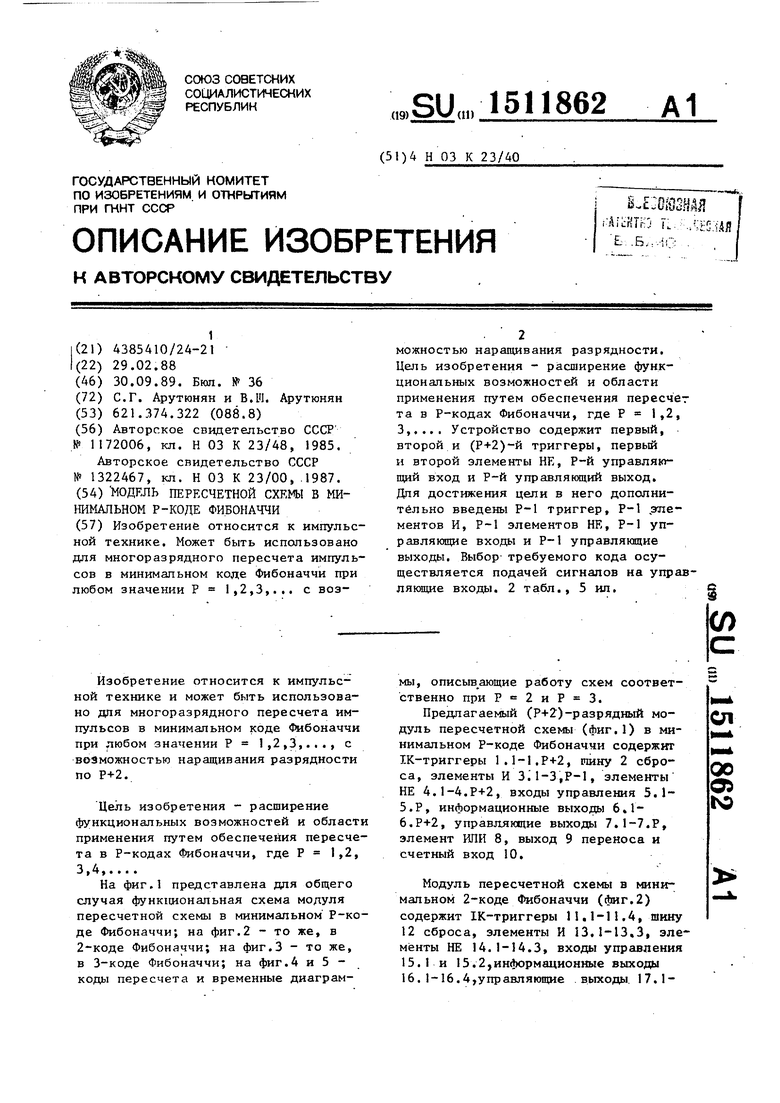

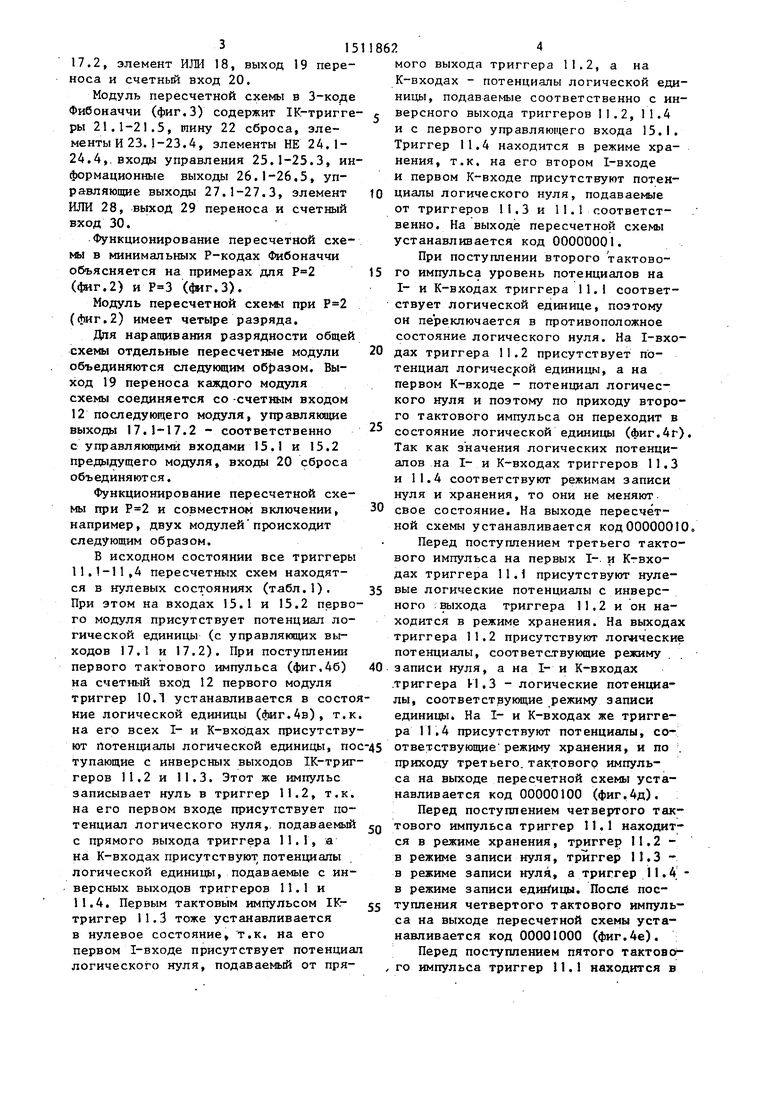

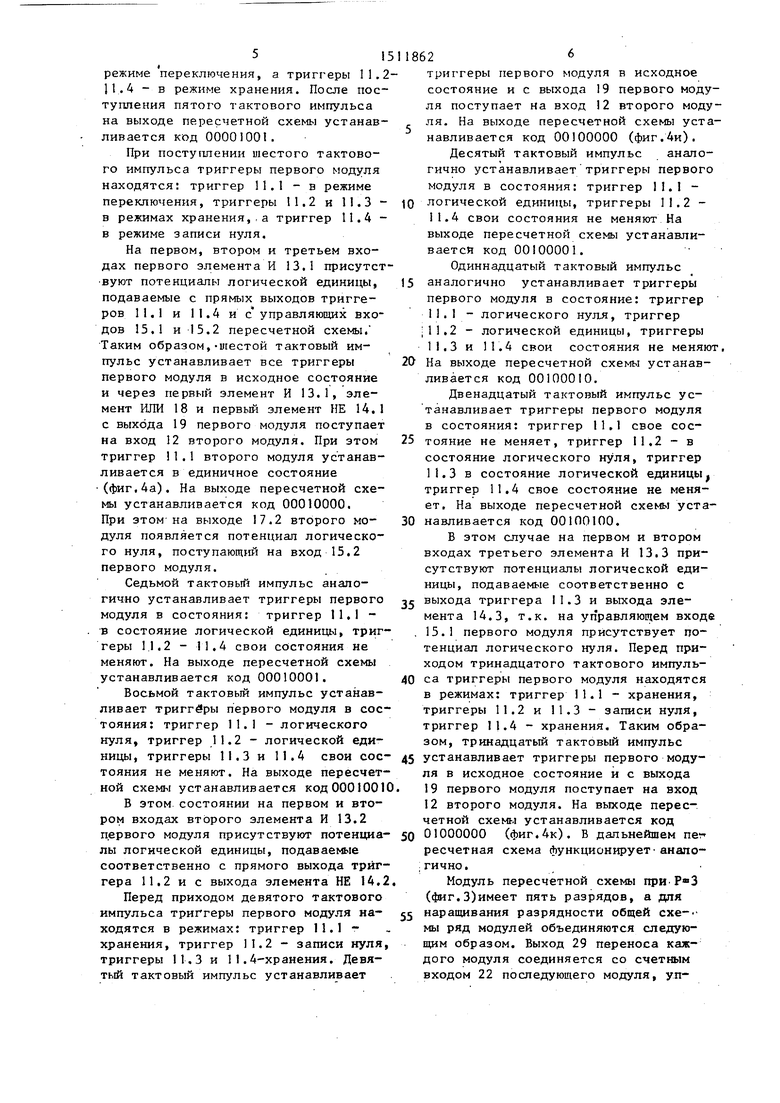

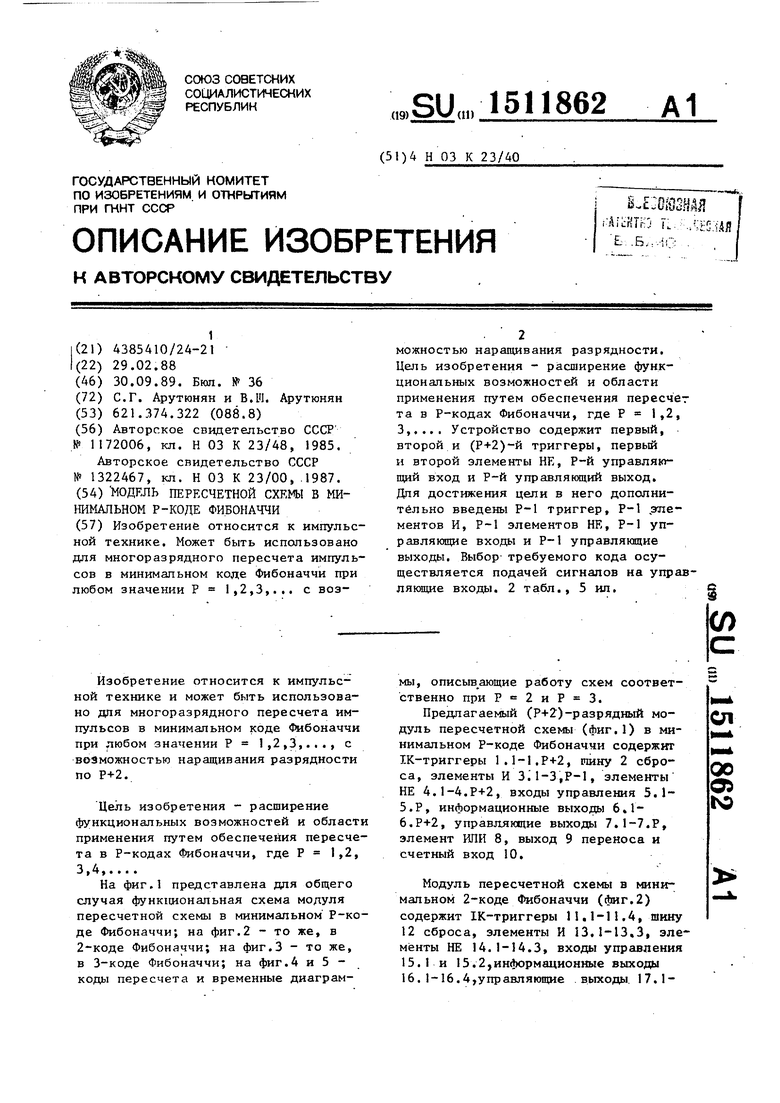

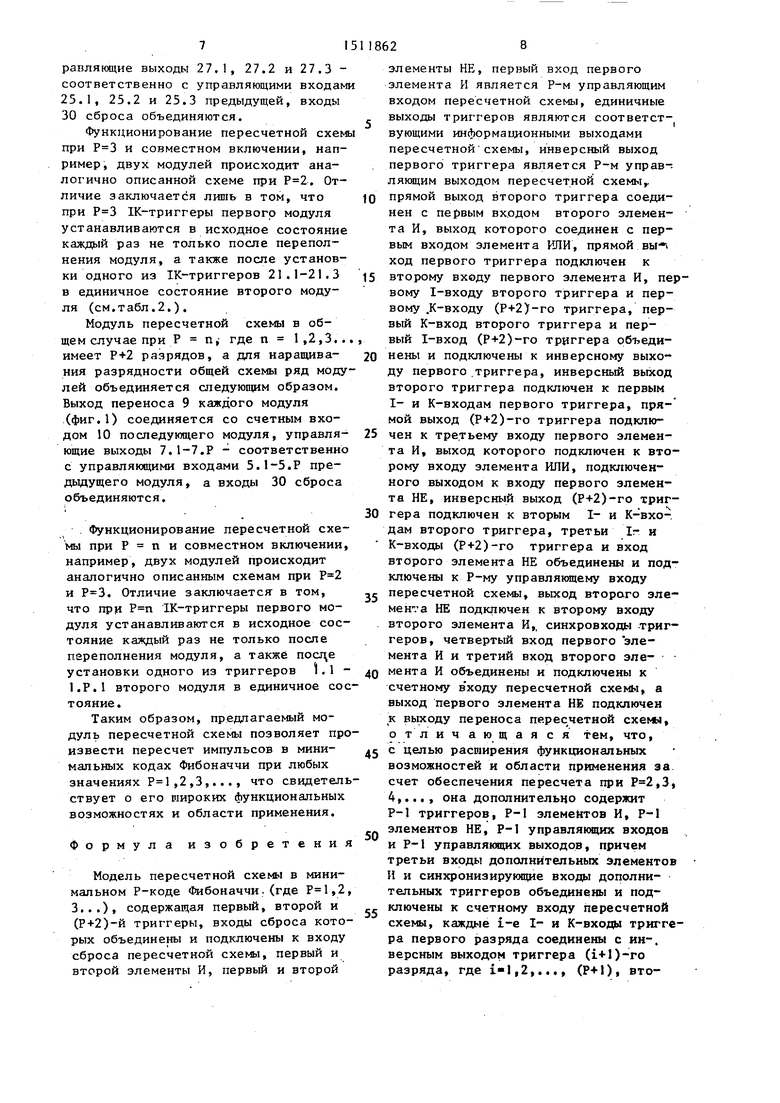

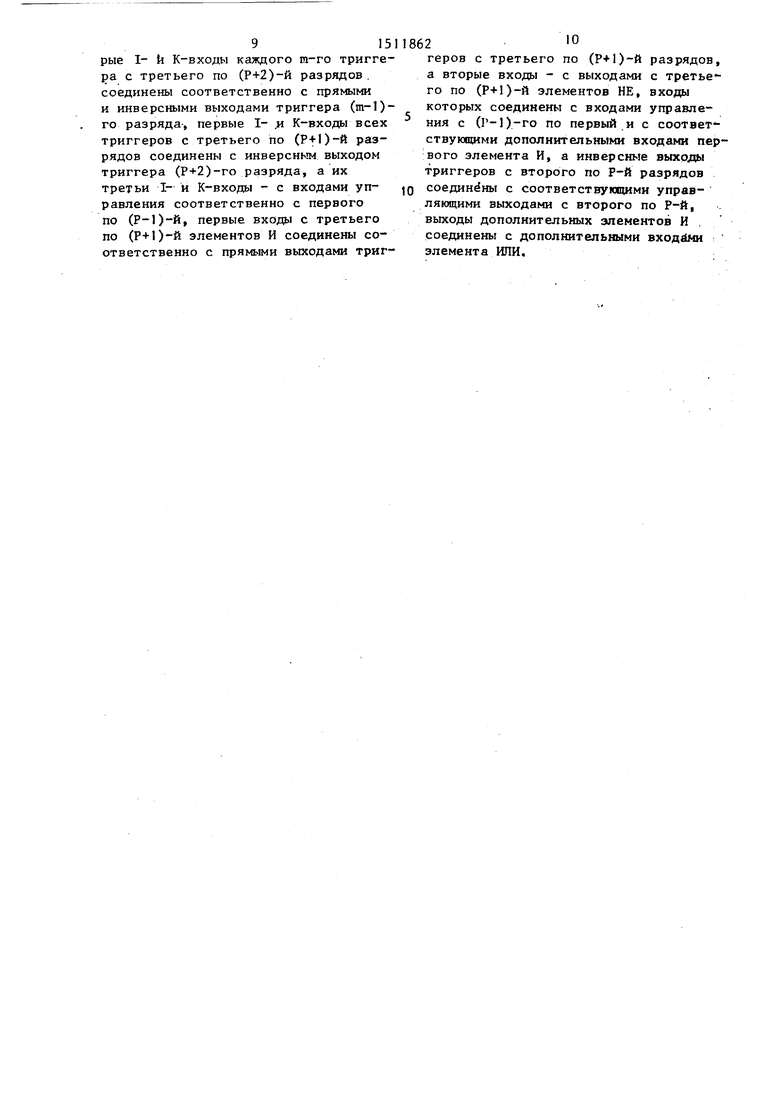

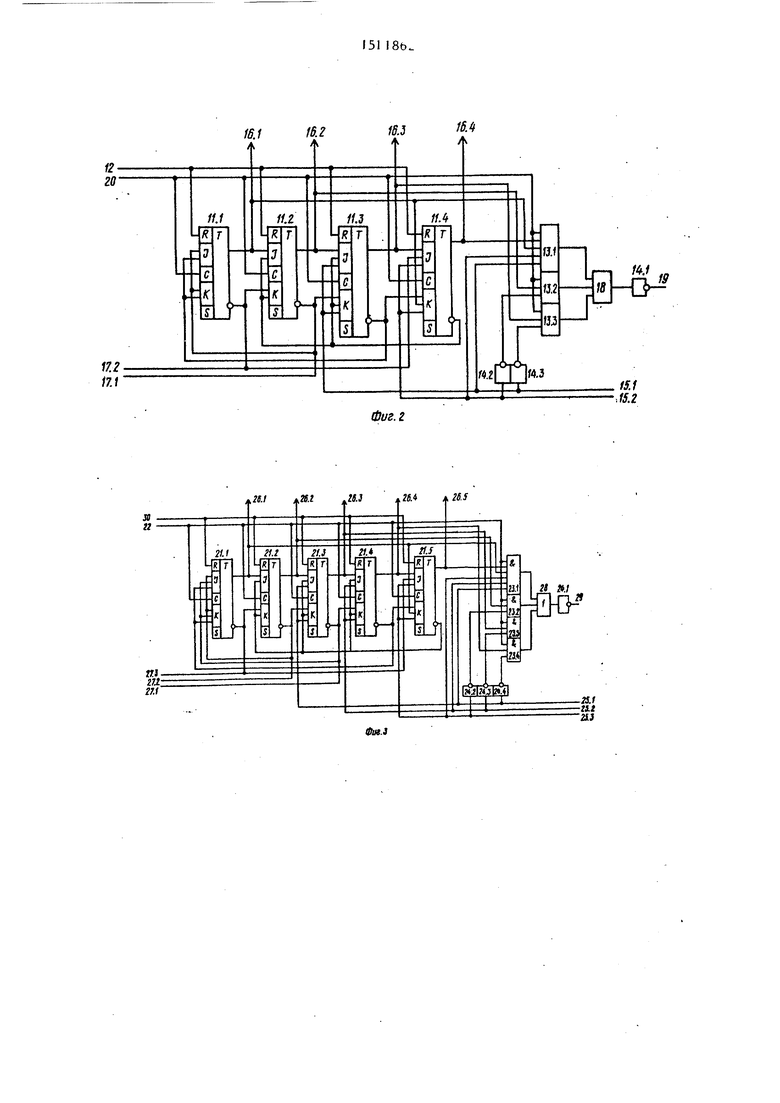

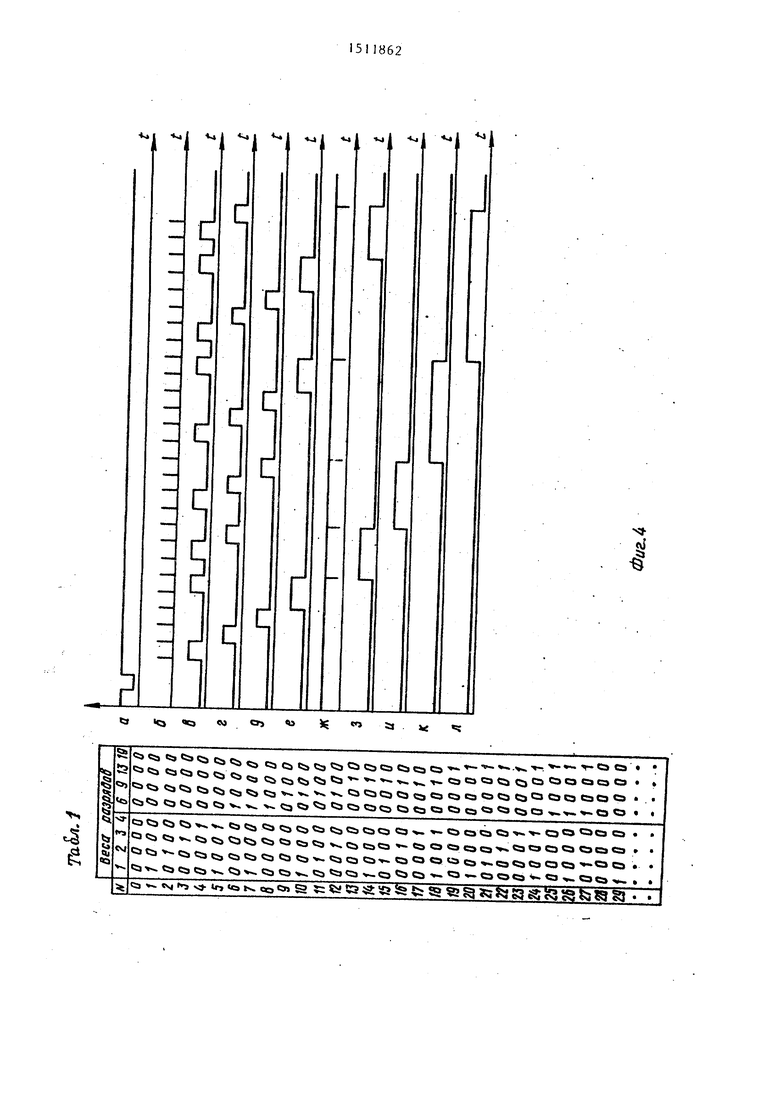

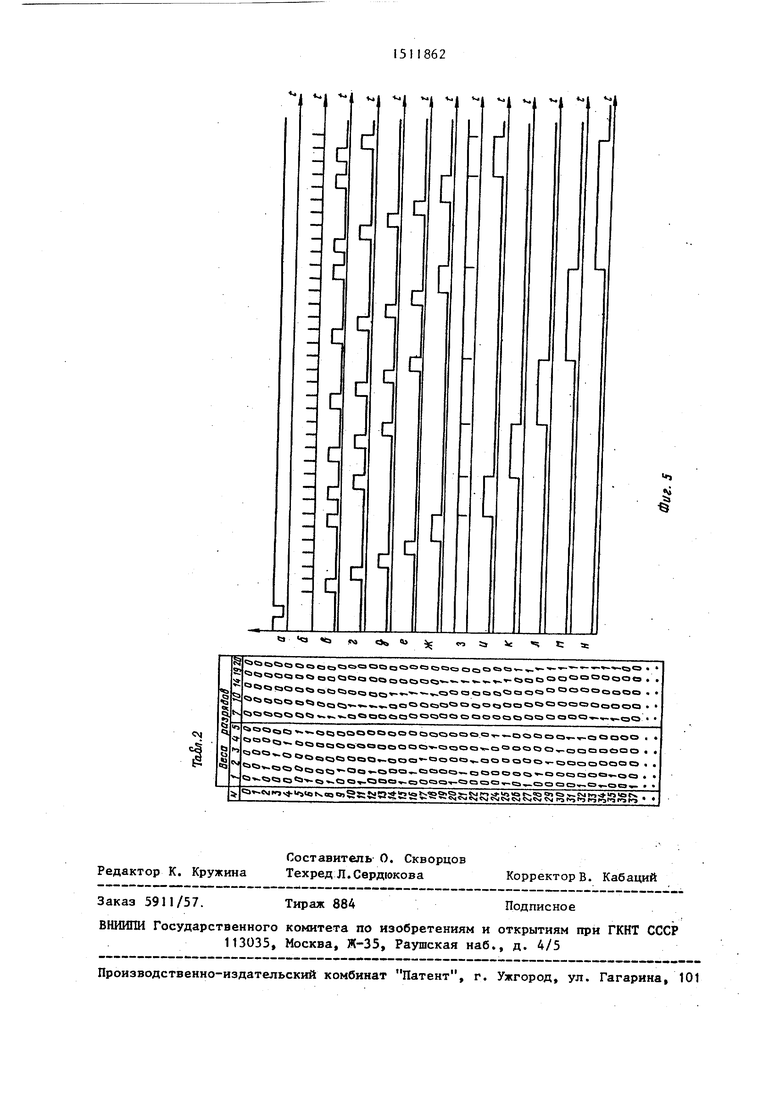

На фиг.1 представлена для общего случая функциональная схема модуля пересчетной схемы в минимальном Р-ко- де Фибоначчи; на фиг.2 - то же, в 2-коде Фибоначчи; на фиг.З - то же, в 3-коде Фибоначчи; на фиг.4 и 5 - коды пересчета и временные диаграммы, описыв ающие работу схем соответственно при Р 2 и Р 3.

Предлагаемый (Р-4-2)-разрядный модуль пересчетной схемы (фиг.1) в минимальном Р-коде Фибоначчи содержит 1К-триггеры 1.1-1.Р+2, шину 2 сброса, элементы И 3;1-3,Р-1, элементы НЕ 4.1-4.Р+2, входы управления 5.1- 5.Р, информационные выходы 6.1- 6.Р+2, управляющие выходы 7.1-7.Р, элемент ИПИ 8, выход 9 переноса и счетный вход 10.

Модуль пересчетной схемы в минимальном 2-коде Фибоначчи (Лиг.2) содержит 1К-триггеры П.1-11.4, шину 12 сброса, элементы И 13,1-13,3, элементы НЕ 14.1-14.3, входы управления 15.1 и 15.2)информационные выходы 16.1-16.4,управляющие выходы 17.1СП

00 Од Ю

315

17.2, элемент ИЛИ 18, выход 19 переноса и счетный вход 20.

Модуль пересчетной схемы в 3-коде Фибоначчи (фиг.З) содержит 1К-тригге- ры 21.1-21.5, шину 22 сброса, элементы И 23. 1-23.4, элементы НЕ 24.1- 24.4,. входы управления 25.1-25.3, информационные выходы 26.1-26.5, управляющие выходы 27.1-27.3, элемент ИЛИ 28, выход 29 переноса и счетный вход 30.

Функционирование пересчетной схемы в минимальных Р-кодах Фибоначчи объясняется на примерах для (фиг.2) и (4ИГ.З).

Модуль пересчетной схемы при (фиг,2) имеет четыре разряда.

ДгЕЯ наращивания разрядности общей схемы отдельные пересчетные модули объединяются следукмцим образом. Выход 19 переноса каждого модуля схемы соединяется со -счетным входом 12 последующего модуля, управляющие выходы 17.1-17.2 - соответственно с управляющими входами 15.1 и 15.2 предыдущего модуля, входы 20 сброса объединяются.

Функционирование пересчетной схемы при и совместном включении, например, двух модулей происходит следующим обраэом.

В исходном состоянии все триггеры 11.1-11,4 пересчетных схем находятся в нулевых состояниях (табл.1). При этом на входах 15.1 и 15.2 первого модуля присутствует потенциал логической единицы (с управляющих выходов 17.1 и 17.2). При поступпении первого тактового импульса (фиг.4б) на счетный вход 12 первого модуля триггер 10.1 устанавливается в состо ние логической единицы (фиг.4в), т.к на его всех 1- и К-входах присутствуют Потенциалы логической единицы, по тупающие с инверсных выходов 1К-триг геров 11.2 и 11.3. Этот же импульс записывает нуль в триггер 11.2, т.к. на его первом входе присутствует потенциал логического нуля,, подаваемый с прямого выхода триггера 11.1, :а на К-входах присутствуют потенциалы логической единицы, подаваемые с ин- версных выходов триггеров 11.1 и 11.4. Первым тактовым импульсом IK- триггер 11.3 тоже устанавливается в нулевое состояние т.к. на его первом 1-входе присутствует потенциа логического куля, подаваемый от пря4

мого выхода триггера 11.2, а на К-входах - потенциалы логической единицы, подаваемые соответственно с инверсного выхода триггеров 11.2, 11.4 и с первого управляющего входа 15.1. Триггер 11.4 находится в режиме хранения, т.к. на его втором 1-входе и первом К-входе присутствуют потенциалы логического нуля, подаваемые от триггеров И.З и 1 1. 1 соответственно. На выходе пересчетной схемы устанавливается код 00000001.

При поступлении второго тактового импульса уровень потенциалов на I- и К-входах триггера 11.1 соответствует логической единице, поэтому он переключается в противоположное состояние логического нуля. На 1-входах триггера 11.2 присутствует потенциал логичес сой единицы, а на первом К-входе - потенциал логического нуля и поэтому по приходу второго тактового импульса он переходит в

состояние логической единицы (фиг.4г). Так как значения логических потенциалов на 1-й К-входах триггеров 11.3 и 11.4 соответствуют режимам записи нуля и хранения, то они не меняют

свое состояние. На выходе пересчетной схемы устанавливается код 00000010.

Перед поступлением третьего тактового импульса на первых I- и Кгвхо- дах триггера 11.1 присутствуют нулевые логические потенциалы с инверсного выхода триггера 11.2 и он находится в режиме хранения. На выходах триггера 11.2 присутствуют логические потенциалы, соответствующие режиму

записи нуля, а на I- и К-входах

.триггера И.З - логические потенциалы, соответствующие режиму записи единицы. На I- и К-входах же триггера 11,4 присутствуют потенциалы, соответствующие режиму хранения, и по . приходу третьего, тактового импульса на выходе пересчетной схемы устанавливается код 00000100 (фиг,4д). Перед поступлением четвертого тактового импульса триггер 11.1 находится в режиме хранения, триггер П . 2 - в режиме записи нуля, триггер 11.3 - в режиме записи нуля, а триггер 11.4 - в режиме записи . После поступления четвертого тактового импульса на выходе пересчетной схемы устанавливается код 00001000 (фиг.4е).

Перед поступлением пятого тактово- го импульса триггер 11.1 находится в

51

режиме переключения, а триггеры 11.2 11.4 - в режиме хранения. После поступления пятого тактового импульса на выходе пересчетной схемы устанавливается код OOOOIOOt.

При поступпении шестого тактового импульса триггеры первого модуля находятся: триггер 11.1 - в режиме переключения, триггеры 11.2 и 11.3 - в режимах хранения,,а триггер 11.4 - в режиме записи нуля.

На первом, втором и третьем входах первого элемента И 13.1 присутст вуют потенциалы логической единицы, подаваемые с прямых выходов триггеров 11.1 и 11.4 и с управляющих входов 15.1 и 15.2 пересчетной схемы. Таким образом,-шестой тактовый импульс устанавливает все триггеры первого модуля в исходное состояние и через первый элемент И 13.1, элемент ИЛИ 18 и первый элемент НЕ 14.1 с выхода 19 первого модуля поступает на вход 12 второго модуля. При этом триггер 11.1 второго модуля устанавливается в единичное состояние (фиг,4а). На выходе пересчетной схемы устанавливается код 00010000. При этом на выходе 17.2 второго модуля появляется потенциал логического нуля, поступающий на вход 15.2 первого модуля.

Седьмой тактовьй импульс аналогично устанавливает триггеры первого модуля в состояния: триггер 11.1 - в состояние логической единицы, триггеры 1.1.2 - 11.4 свои состояния не меняют. На выходе пересчетной схемы устанавливается код 00010001.

Восьмой тактовый импульс устанавливает триггеры первого модуля в состояния: триггер 11.1 - логического нуля, триггер .11.2 - логической единицы, триггеры 11.3 и 11.4 свои состояния не меняют. На выходе пересчетной схемы устанавливается код 0001001

В этом состоянии на первом и втором входах второго элемента И 13.2 первого модуля присутствуют потенциалы логической единицы, подаваемые соответственно с прямого выхода триггера 11.2 и с выхода элемента НЕ 14.2

Перед приходом девятого тактового импульса триггеры первого модуля находятся в режимах: триггер 11.1 - хранения, триггер 11.2 - записи нуля, триггеры 11.3 и 11.4-хранения. Девятый тактовый импульс устанавливает

26

триггеры первого модуля в исходное состояние и с выхода 19 первого модуля поступает на вход 12 второго модуля. На выходе пересчетной схемы устанавливается код 00100000 (фиг.4и).

Десятый тактовый импульс аналогично устанавливает триггеры первого модуля в состояния: триггер 11.1 логической единицы, триггеры 11.2 - 11.4 свои состояния не меняют На выходе пересчетной схемы устанавливается код 00100001.

Одиннадцатый тактовый импульс

аналогично устанавливает триггеры первого модуля в состояние: триггер 11.1 - логического нуля, триггер 11.2 - логической единицы, триггеры 11.3 и П.4 свои состояния не меняют.

На выходе пересчетной схемы устанавливается код 00100010.

Двенадцатый тактовый импульс ус- танавливает триггеры первого модуля в состояния: триггер 11.1 свое состояние не меняет, триггер 11.2 - в состояние логического нуля, триггер 11.3 в состояние логической единицы триггер 11.4 свое состояние не меняет. На выходе пересчетной схемы устанавливается код 00100100.

В этом случае на первом и втором входах третьего элемента И 13.3 присутствуют потенциалы логической единицы, подаваемые соответственно с

выхода триггера 11.3 и выхода элемента 14.3, т.к. на уп равляющем входе 15.1 первого модуля присутствует потенциал логического нуля. Перед приходом тринадцатого тактового импульса триггеры первого модуля находятся в режимах: триггер 11.1 - хранения, триггеры 11.2 и 11.3 - записи нуля, триггер 11.4 - хранения. Таким образом, тринадцатый тактовый импульс

устанавливает триггеры первого модуля в исходное состояние и с выхода 19 первого модуля поступает на вход 12 второго модуля. На выходе пересчетной cxeMtJ устанавливается код

01000000 (фиг.4к). В дальнейшем пет ресчетная схема функционирует-анапоГИЧНО.

Модуль пересчетной схемы прИ Р 3 (фиг.З)имеет пять разрядов, а для наращивания разрядности общей схе- мы ряд модулей объединяются следующим образом. Выход 29 переноса каждого модуля соединяется со счетным входом 22 последующего модуля, управляющие выходы 27.1, 27.2 и 27.3 - соответственно с управляющими входам 25.1, 25.2 и 25.3 предыдущей, входы 30 сброса объединяются.

Функционирование пересчетной схем при и совместном включении, например, двух модулей происходит аналогично описанной схеме при . Отличие заключается лить в том, что при 1К-триггеры первого модуля устанавливаются в исходное состояние каждый раз не только после переполнения модуля, а также после установки одного из 1К-триггеров 21.1-21.3 в единичное состояние второго модуля (см.табл.2.).

Модуль пересчетной схемы в общем случае при Р п, где п 1,2,3.. имеет Р+2 разрядов, а для наращива- ния разрядности общей схемы ряд модулей объединяется с 1едуюп им образом. Выход переноса 9 каждого модуля (фиг.1) соединяется со счетным входом 10 последующего модуля, управля- ющие выходы 7.1-7.Р - соответственно с управляющими входами 5.1-5.Р пре- дьщущего модуля, а входы 30 сброса объединяются. .

Функционирование пересчетной схе- Ш при Р п и совместном включении, например, двух модулей происходит аналогично описанным схемам при и . Отличие заключается в том,что при 1К-триггеры первого модуля устанавливаются в исходное состояние каждый раз не только после переполнения модуля, а также постое установки одного из триггеров 1.1 - 1.Р.1 второго модуля в единичное состояние.

Таким образом, предлагаемый модуль пересчетной схемы позволяет произвести пересчет импульсов в мини- мальных кодах Фибоначчи при любых значениях ,2,3,..., что свидетелствует о его В1ироких функциональных возможностях и области применения.

формула изобретения

Модель пересчетной схемы в минимальном Р-коде Фибоначчи:(где ,2, 3...), содержащая первый, второй и (Р+2)-й триггеры, входы сброса которых объединены и подключены к входу сброса пересчетной схемы, первый и второй элементы И, первый и второй

5

0 5 0

о

0

элементы НЕ, первый вход первого элемента И является Р-м управляющим входом пересчетной схемы, единичные выходы триггеров являются соответствующими информаияонными выходами пересчетной схемы, инверсный выход первого триггера является Р-м управ-- ляющим выходом пересчетной схемы,, прямой выход второго триггера соединен с первым входом второго элемента И, выход которого соединен с первым входом элемента ИЛИ, прямой ход первого триггера подключен к второму входу первого элемента И, первому 1-входу второго триггера и первому .К-входу (Р+2)-го триггера, первый К-вход второго триггера и первый 1-вход (Р+2)-го триггера объединены и подключены к инверсному выходу первого.триггера, инверсный выход второго триггера подключен к первым I- и К-входам первого триггера, прямой выход (Р+2)-го триггера подключен к третьему входу первого элемента И, выход которого подключен к второму входу элемента ИЛИ, подключенного выходом к входу первого элемента НЕ, инверсный выход (Р+2)-го триггера подключен к вторым I- и К-входам второго триггера, третьи 1г и К-входы (Р+2)-го триггера и вход второго элемента НЕ объединены и подключены к Р-му управляющему входу пересчетной схемы, выход второго элемента НЕ подключен к второму входу второго элемента И,, синхровходы триггеров, четвертый вход первого элемента И и третий вход второго элемента И объединены и подключены к счетному в ходу пересчетной схемы, а выход первого элемента НЕ подключен к вьпсоду переноса переучетной схемы, отличающаяся тем, что, с целью расширения функциональных возможностей и области применения за счет обеспечения пересчета при ,3, 4,..., она дополнительно содержит Р-1 триггеров, Р-1 элемейтов И, P-I элементов НЕ, Р-1 управляющих входов и Р-1 управляющих выходов, причем третьи входы дополнительных элементов И и синхронизирующие входы дополнительных триггеров объединены и подключены к счетному входу пересчетной схемы, каждые i-e 1- и К-входы триггера первого разряда соединены с ин-. версным выходом триггера (i+l)-ro разряда, где ,2,..., (Р-И), вто9151

рые I- k К-входы каждого m-го триггера с третьего по (Р+2)-й разрядов. соединены соответственно с прямыми и инверсными выходами триггера (т-1)- го разряда, первые I- .и К-входы всех триггеров с третьего по (Р+1)-й разрядов соединены с инверсным выходом триггера (Р+2)-го разряда, а их третьи I- и К входы - с входами управления соответственно с первого по (Р-)-й, первые входы с третьего по (Р+1)-й элементов И соединены соответственно с прямыми выходами триг1862

10

геров с третьего по (Р+1)-й разрядов, а вторые входы - с выходами с третье го по (Р+1)-й элементов НЕ, входы которых соединены с входами управления с (Г-1)-го по первый и с соответ - ствующими дополнительными входами первого элемента И, а инверсные выходы триггеров с второго по Р-й разрядов

соединены с соответствующими управляющими выходами с второго по Р-й, выходы дополнительных элементов И . соединены с дополнительными элемента ИЛИ.

--- 22

1B.1

16.2

Ш

Ш

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик импульсов в максимальных кодах Фибоначчи | 1988 |

|

SU1531215A1 |

| Пересчетная схема в коде Фибоначчи | 1991 |

|

SU1780188A1 |

| Пересчетное устройство в коде Фибоначчи | 1990 |

|

SU1725389A1 |

| Пересчетная схема в коде Фибоначчи | 1990 |

|

SU1757098A1 |

| Пересчетное устройство в коде Фибоначчи | 1989 |

|

SU1651375A1 |

| Пересчетная схема в коде Фибоначчи | 1991 |

|

SU1800612A1 |

| Счетчик импульсов в кодах Фибоначчи | 1990 |

|

SU1762408A1 |

| Счетчик импульсов в максимальных кодах Фибоначчи | 1990 |

|

SU1720157A1 |

| Реверсивный кольцевой счетчик | 1980 |

|

SU919092A1 |

| Устройство для отображения информации на экране электронно-лучевой трубки | 1989 |

|

SU1626251A1 |

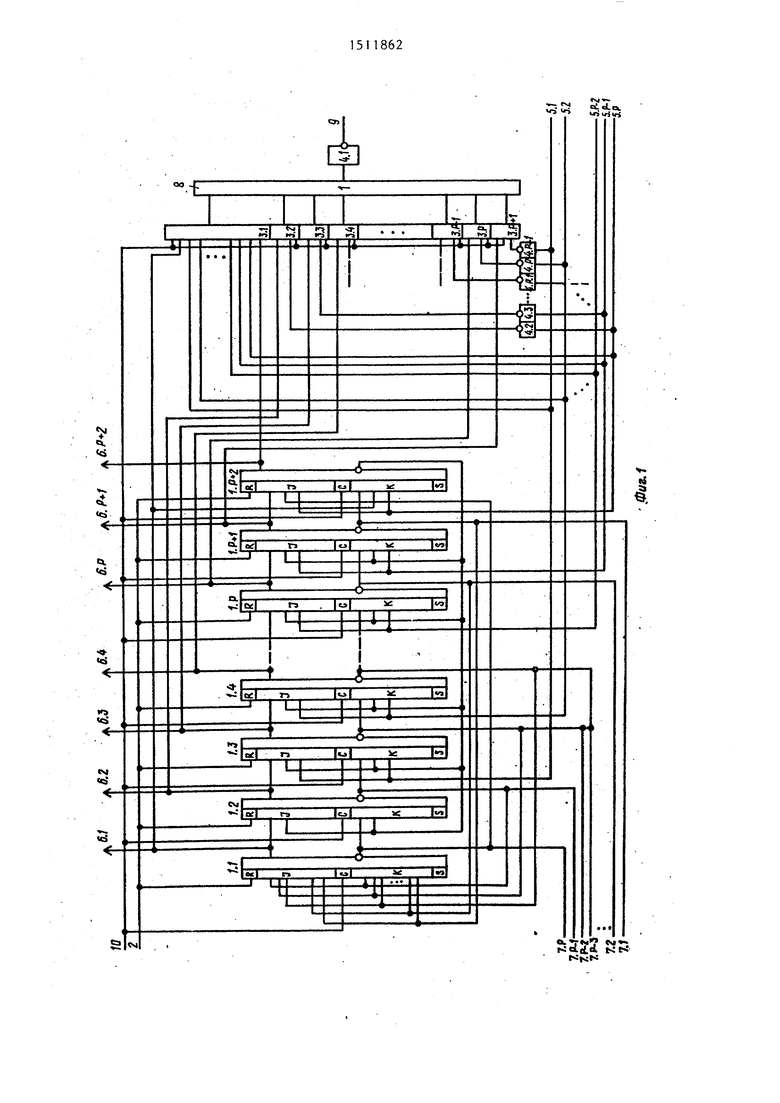

Изобретение относится к импульсной технике. Может быть использовано для многоразрядного пересчета импульсов в минимальном коде Фибоначчи при любом значении Р=1,2,3,..., с возможностью наращивания разрядности. Цель изобретения - расширение функциональных возможностей и области применения путем обеспечения пересчета в Р-кодах Фибоначчи, где Р=1,2,3,.... Устройство содержит первый, второй и (Р+2)-й триггеры, первый и второй элементы НЕ, Р - й управляющий вход и Р-й управляющий выход. Для достижения цели в него дополнительно введены Р-1 триггер, Р-1 элементов И, Р-1 элементов НЕ, Р-1 управляющие ввходы и Р-1 управляющие выходы. Выбор требуемого кода осуществляется подачей сигналов на управляющие входы. 5 ил.

«3 Чз «Ь

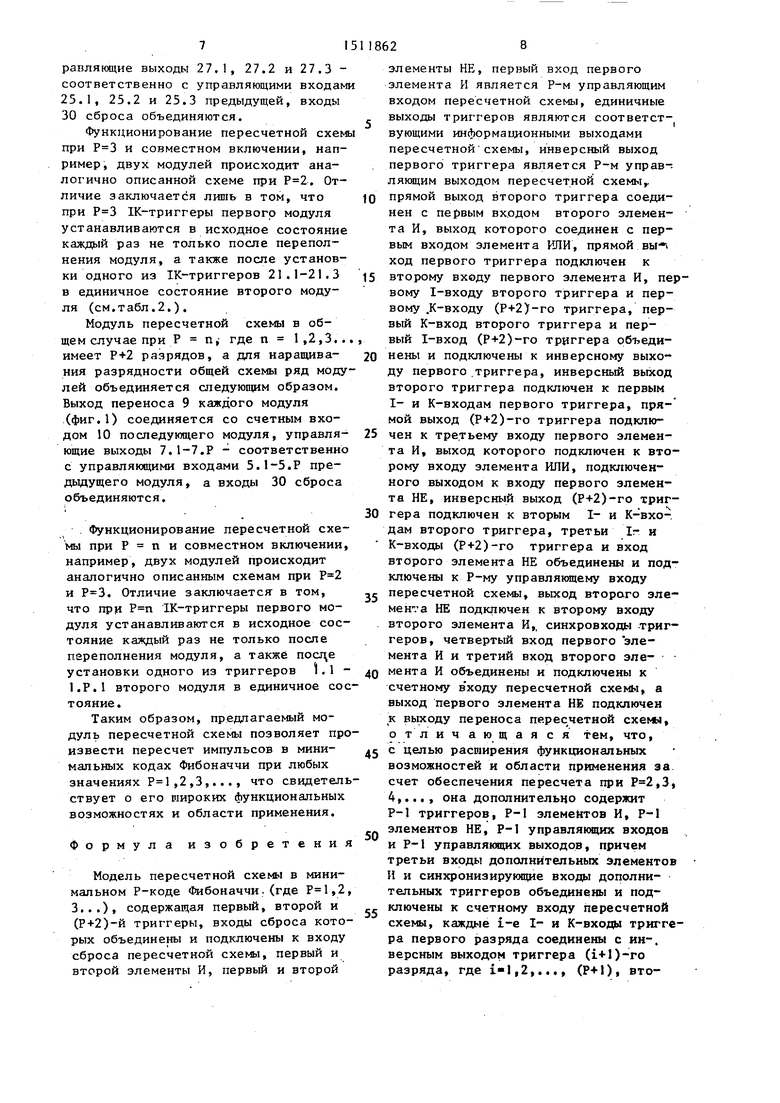

lla IQ Qo о о ca СЭ cs

sc eje30ca« ot3Cjc3oc cj -

«assotaootacseaca-r..,

cjcacacacacici «.c

-оеэ эоо

-сэс сзоое Оосэсэсасэсэезсзсэ.сэ,--оосэеэсэ оеэооо сэеэс овооеэаС1еэ сэсзос|-«-еэОоос5о сэасзсэОС10

- «Эе Сз«эос о -саоо - о э ао о о -сэсэсзооооса -«э Са сцэ 53 о о -«а OQ ,-сэсзоеэ -еэ еэо е -о сэсэ сэ сэс.сэ сэ

- С5 -«а «Сэоч-Овв -еэС «г еэч-сэсэсз«а -еэ -сэоеасэ -еэ,,,,,o ;;aaa вs :1gS: гз&ig;aSS SgiSg; Йй gigй

Редактор К. Кружина

Составитель О. Скворцов Техред Л.Сердюкова

Заказ 5911/57.

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

CJu V

-оеэ эоо

Корректор В. Кабаций

Подписное

| Счетчик импульсов в @ -кодах Фибоначчи | 1983 |

|

SU1172006A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Пересчетная схема в коде Фибоначчи | 1985 |

|

SU1322467A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1989-09-30—Публикация

1988-02-29—Подача