Изобретение относится к автоматике и информационно-измерительной технике и предназначено для коммутации и преобразования аналоговых сиг-, налов.

Целью изобретения является повышение быстродействия устройства.

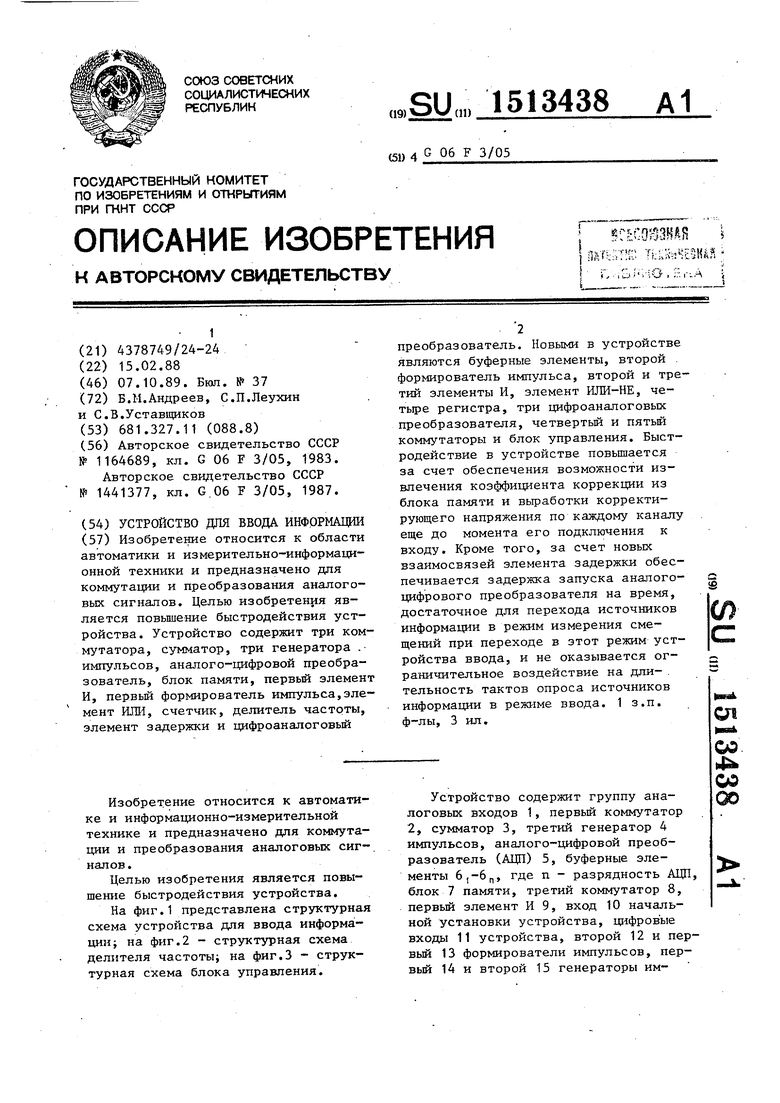

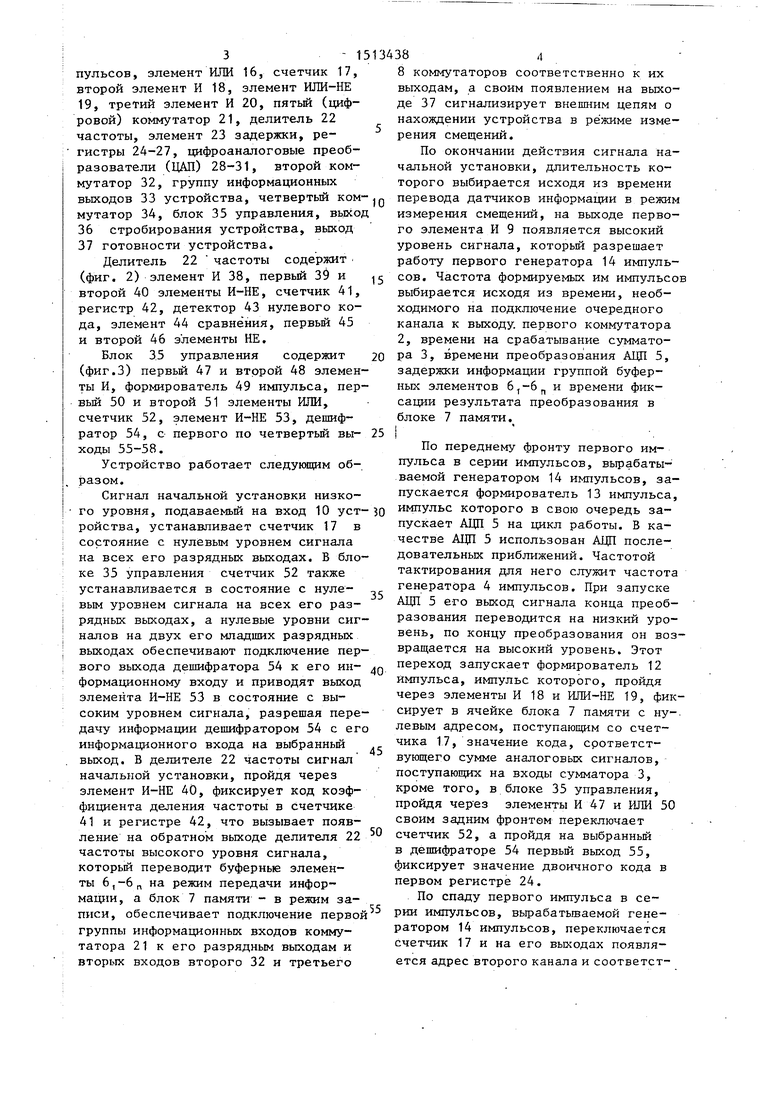

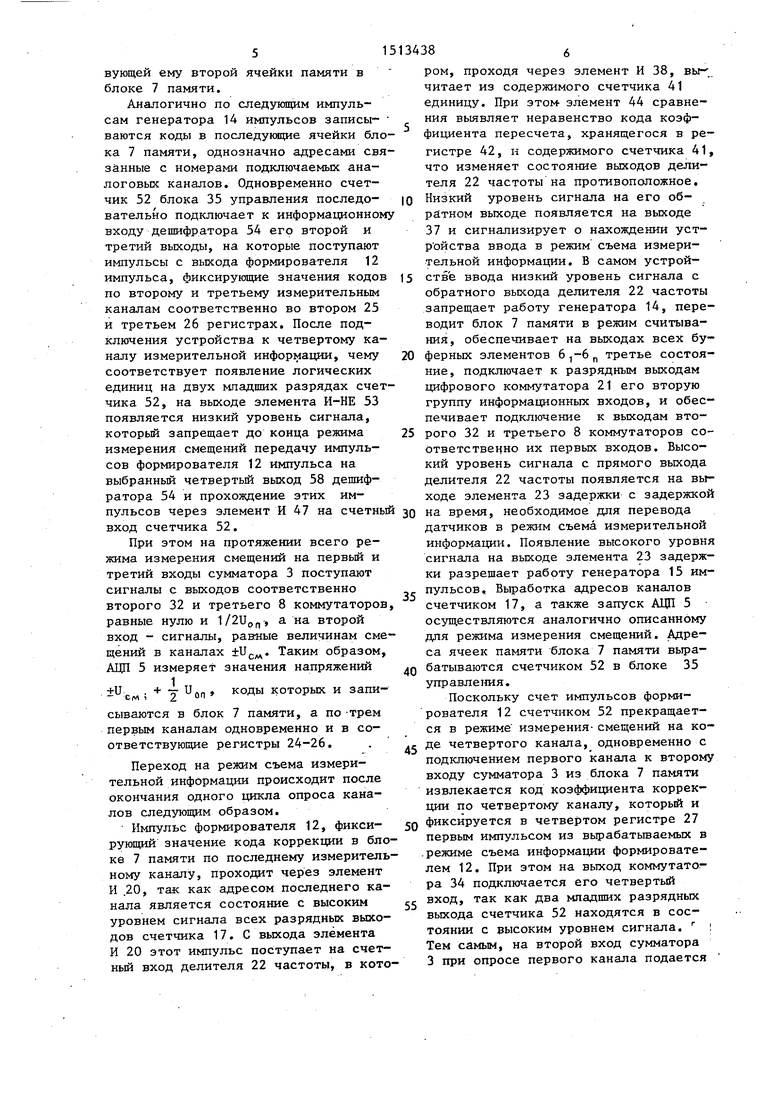

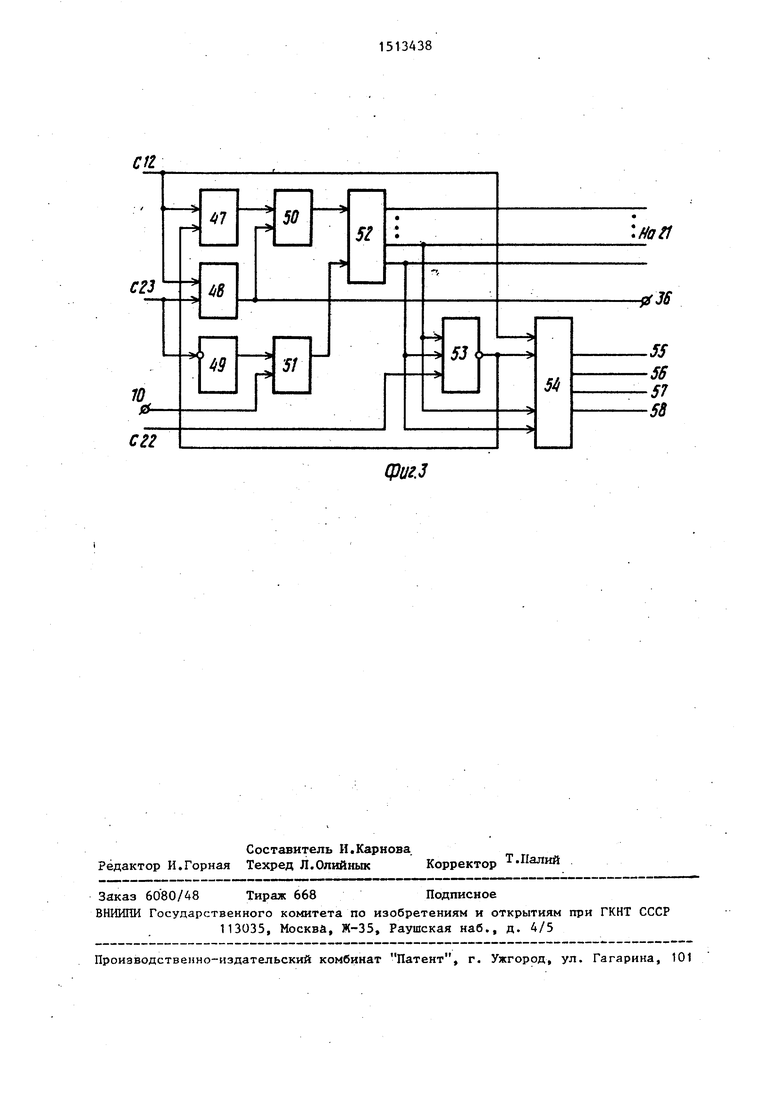

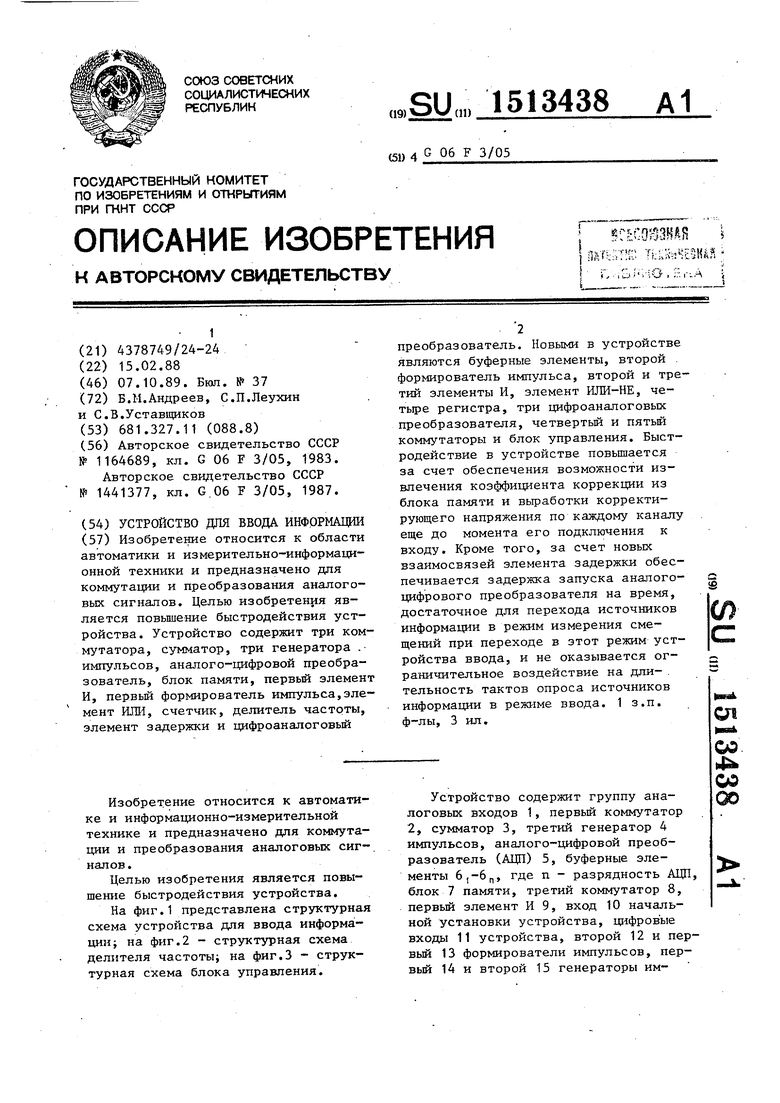

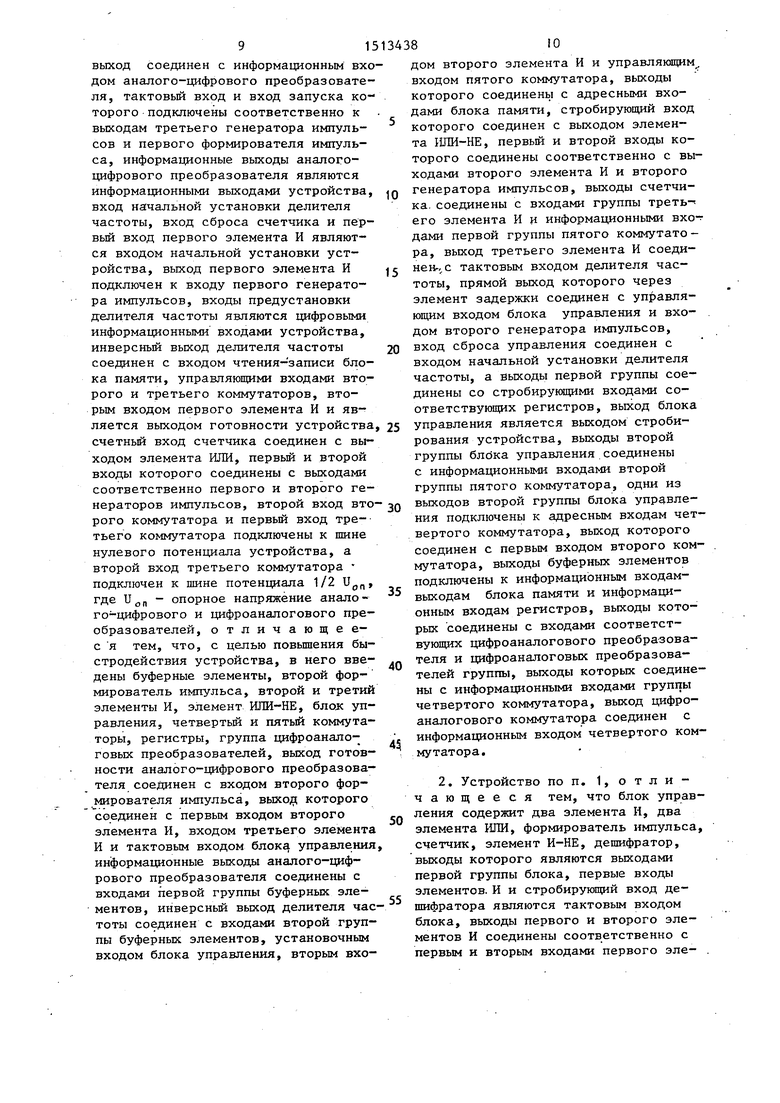

На фиг.1 представлена структурная схема устройства для ввода информа - цин; на фиг.2 - структурная схема делителя частоты; на фиг.З - структурная схема блока управления.

Устройство содержит группу аналоговых входов 1, первьй коммутатор 2, сумматор 3, третий генератор 4 импульсов, аналого-цифровой преобразователь (АЦП) 5, буферные элементы 6,-6, где п - разрядность АЦП, блок 7 памяти, третий коммутатор 8, первьй элемент И 9, вход 10 начальной установки устройства, цифров ые входы 11 устройства, второй 12 и первый 13 формирователи импульсов, пер- вьй 14 и второй 15 генераторы имоэ

00

пульсов, элемент или 16, счетчик 17, второй элемент И 18, элемент ИЛИ-НЕ 19, третий элемент И 20, пятьй (цифровой) коммутатор 21, делитель 22 частоты, элемент 23 задержки, ре- гистры 24-27, цифроаналоговые преобразователи (ЦАП) 28-31, второй коммутатор 32, группу информационных выходов 33 устройства, четвертый KOM-JQ мутатор 34, блок 35 управления, вькод

36стробирования устройства, выход

37готовности устройства. Делитель 22 частоты содержит

(фиг. 2) элемент И 38, первый 39 и 5 второй 40 элементы И-НЕ, счетчик 41, регистр 42, детектор 43 нулевого кода, элемент 44 сравнения, первьй 45 и второй 46 элементы НЕ.

Блок 35 управления содержит 20 (фиг.З) первьй 47 и второй 48 элементы И, формирователь 49 импульса, первьй 50 и второй 51 элементы ИЛИ, счетчик 52, элемент И-НЕ 53, дешифратор 54, с первого по четвертьй вы- 25 ходы 55-58.

Устройство работает следующим образом.

Сигнал начальной установки низко- го уровня, подаваемьй на вход 10 уст-JO ройства, устанавливает счетчик 17 в состояние с нулевым уровнем сигнала на всех его разрядных выходах. В блоке 35 управления счетчик 52 также устанавливается в состояние с нуле- .,5 вым уровнем сигнала на всех его разрядных выходах, а нулевые уровни сигналов на двух его младших разрядных выходах обеспечивают подключение первого выхода дешифратора 54 к его ин- д формационному входу и приводят выход элемента И-НЕ 53 в состояние с высоким уровнем сигнала, разрешая передачу информации дешифратором 54 с его информационного входа на выбранньй ., выход. В делителе 22 частоты сигнал начальной установки, пройдя через элемент И-НЕ 40, фиксирует код коэффициента деления частоты в счетчике 41 и регистре 42, что вызывает появление на обратном выходе делителя 22 частоты высокого уровня сигнала, которьй переводит буферные элементы 6,-6 п на режим передачи информации, а блок 7 памяти - в режим записи, обеспечивает подключение первой группы информационных входов коммутатора 21 к его разрядным выходам и вторых входов второго 32 и третьего

50

55

Q

0 5

O 5 д ,

0

8 коммутаторов соответственно к их выходам, а своим появлением на выходе 37 сигнализирует внешним цепям о нахождении устройства в режиме измерения смещений.

По окончании действия сигнала начальной установки, длительность которого выбирается исходя из времени перевода датчиков информации в режим измерения смещений, на выходе первого элемента И 9 появляется высокий уровень сигнала, которьй разрешает работу первого генератора 14 импульсов. Частота формируемых им импульсов выбирается исходя из времени, необходимого на подключение очередного канала к выходу, первого коммутатора 2, времени на срабатывание сумматора 3, времени преобразования АЦП 5, задержки информации группой буферных элементов и времени фиксации результата преобразования в блоке 7 памяти.

По переднему фронту первого импульса в серии импульсов, вырабатываемой генератором 14 импульсов, запускается формирователь 13 импульса, И1 тульс которого в свою очередь запускает АЦП 5 на цикл работы. В качестве АЦП 5 использован АЦП последовательных приближений. Частотой тактирования для него служит частота генератора 4 импульсов. При запуске АЦП 5 его выход сигнала конца преобразования переводится на низкий уровень, по концу преобразования он возвращается на высокий уровень. Этот переход запускает формирователь 12 Импульса, импульс которого, пройдя через элементы И 18 и ИЛИ-НЕ 19, фиксирует в ячейке блока 7 памяти с ну-, левым адресом, поступающим со счетчика 17, значение кода, срответст- вующего сумме аналоговых сигналов, поступающих на входы сумматора 3, кроме того, в блоке 35 управления, пройдя через элементы И 47 и ИЖ 50 своим задним фронтом переключает счетчик 52, а пройдя на выбранньй в дешифраторе 54 первьй выход 55, фиксирует значение двоичного кода в первом регистре 24.

По спаду первого импульса в серии импульсов, вырабатьшаемой генератором 14 импульсов, переключается счетчик 17 и на его выходах появляется адрес второго канала и соответствующей ему второй ячейки памяти в блоке 7 памяти.

Аналогично по следунлцим импульсам генератора 14 импульсов запись:- ваются коды в последующие ячейки блока 7 памяти, однозначно адресами связанные с номерами подключаемых аналоговых каналов. Одновременно счетчик 52 блока 35 управления последо- вательно подключает к информационном входу дешифратора 54 его второй и третий выходы, на которые поступают иютульсы с выхода формирователя 12 импульса, фиксирующие значения кодов по второму и третьему измерительным каналам соответственно во втором 25 и третьем 26 регистрах. После подключения устройства к четвертому каналу измерительной информации, чему соответствует появление логических единиц на двух младших разрядах счетчика 52, на выходе элемента И-НЕ 53 появляется низкий уровень сигнала, которьй запрещает до конца режима измерения смещений передачу импульсов формирователя 12 импульса на выбранный четвертый выход 58 дешифратора 54 и прохождение этих импульсов через элемент И 47 на счетный зо на время, необходимое для перевода вход счетчика 52.

При этом на протяжении всего режима измерения смещений на первый и третий входы сумматора 3 поступают сигналы с выходов соответственно второго 32 и третьего 8 коммутаторов, равные нулю и 1/2Uof,, а на второй вход - сигналы, равные величинам смещений в каналах ±U. Таким образом, АЦП 5 измеряет значения напряжений

35

40

датчиков в режим съема измерительно информации. Появление высокого уров сигнала на выходе элемента 23 задер ки разрешает работу генератора 15 и пульсов. Выработка адресов каналов счетчиком 17, а также запуск АЦП 5 осуществляются аналогично описанном для режима измерения смещений. Адре са ячеек памяти блока 7 памяти выра батываются счетчиком 52 в блоке 35 управления.

±и.

2 й

коды которых и запиСгл 1

сываются в блок 7 памяти, а по -трем первым каналам одновременно и в соответствующие регистры 24-26.

Переход на режим съема измерительной информации происходит после окончания одного цикла опроса каналов следующим образом.

Импульс формирователя 12, фиксирующий значение кода коррекции в блоке 7 памяти по последнему измерительному каналу, проходит через элемент И .20, так как адресом последнего канала является состояние с высоким уровнем сигнала всех разрядных выходов счетчика 17. С выхода элемента И 20 этот импульс поступает на счетный вход делителя 22 частоты, в котором, проходя через элемент И 38, вы- читает из содержимого счетчика 41 единицу. При этом- элемент 44 сравнения выявляет неравенство кода коэффициента пересчета, хранящегося в регистре 42, и содержимого счетчика 41 что изменяет состояние выходов делителя 22 частоты на противоположное. Низкий уровень сигнала на его обратном выходе появляется на выходе 37 и сигнализирует о нахождении уст- р ойства ввода в режим съема измерительной информации. В самом устройстве ввода низкий уровень сигнала с обратного выхода делителя 22 частоты запрещает работу генератора 14, переводит блок 7 памяти в режим считывания, обеспечивает на выходах всех буферных элементов 6,-6 третье состояние, подключает к разрядным выходам цифрового коммутатора 21 его вторую группу информационных входов, и обеспечивает подключение к выходам второго 32 и третьего 8 коммутаторов соответственно их первых входов. Высокий уровень сигнала с прямого выхода делителя 22 частоты появляется на выходе элемента 23 задержки с задержкой

на время, необходимое для перевода

датчиков в режим съема измерительной информации. Появление высокого уровня сигнала на выходе элемента 23 задержки разрешает работу генератора 15 импульсов. Выработка адресов каналов счетчиком 17, а также запуск АЦП 5 осуществляются аналогично описанному для режима измерения смещений. Адреса ячеек памяти блока 7 памяти вырабатываются счетчиком 52 в блоке 35 управления.

Поскольку счет импульсов формирователя 12 счетчиком 52 прекращается в режиме измерения- смещений на коде четвертого канала, одновременно с подключением первого канала к второму входу сумматора 3 из блока 7 памяти извлекается код коэффициента коррекции по четвертому каналу, который и фиксируется в четвертом регистре 27 первым импульсом из вырабатьгоаемых в режиме съема информации формирователем 12. При этом на выход коммутато.- ра 34 подключается его четвертый вход, так как два младших разрядных выхода счетчика 52 находятся в состоянии с высоким уровнем сигнала. I Тем самым, на второй вход сумматора 3 при опросе первого канала подается

напряжение с выхода ЦАП 28, соответствующее коду коррекции первого канала. В дальнейшем счетчики 17 и 52 переключают синхронно, и опережение содержимого счетчика 52 по отношению к счетчику 17 всегда равно четырем. Это обеспечивает при условии, что число каналов измерительной информации кратно четырем, постоянное извлечение коэффициентов коррекции с опережением подключения соответствующих им каналов на три такта опроса каналов, что дает возможность ЦАП 28-3 вырабатывать напряжения коррекции смещений к моменту подключения соответствующего канала. По кодам, считываемым из блока 7 памяти четырех- квадратные ЦАП 28-31 вырабатывают напряжения, равные (±11). Таким образом, на выходе сумматора 3 при переборе каналов датчиков образуются напряжения, равные

(и,.±и,,.)+(+и.)и,.,

которые представляют из себя информативную частьЕ (без начальных сме- |лцений) сигналов с датчиков. Эти напряжения измеряются АЦП 5 и поступают в виде цифрового кода на информационные выходы 33 устройства. Моменты истинного значения цифровых данных стробируются импульсами формирователя 12, которые, проходя через элемент И 48, появляются на выходе 36 стробирования данных устройства.

I Нахождение устройства ввода в ре- I жиме съема измерительной информации I продолжается столько циклов опроса I датчиков, сколько необходимо для iуменьшения до нулевого кода содержимого счетчика 41 в делителе 22 час тоты.

При нулевом содержимом счетчика 41, что фиксируется детектором 43 нулевого кода, очередное окончание цикла опроса каналов, выражаемое прохождением импульса формирователя 12 через элементы И 20, И-НЕ 39 и 40, вызывает фиксацию этим импульсом кода коэффициента пересчета в счетчике ;41-и буферном регистре 42. При этом элемент 44 сравнения выявляет равенство содержимого счетчика 41 и ре- ;гистра 42, что проявляется в появ- ;лении на прямом и обратном выходах :делителя 22 частоты соответственно низкого и высокого уровней сигнала.

0

5

0

5

0

5

0

45

50

5

которые переводят устройство ввода ) в режим измерения смещений на один цикл опроса измерительных каналов.

Появление высокого уровня сигнала на обратном выходе делителя 22 частоты приводит к тем же переключениям в устройстве, что и при начальной установке. Появление низкого - уровня сигнала на его прямом выходе приводит к появлению низкого уровня сигнала на выходе элемента 23 задержки (без задержки, так как в качестве элемента задержки выбрана схема, реализующая задержку перепада сигнала из низкого в высокий уровень), который запрещает работу генератора 15 и .запускает формирователь 49 в блоке 35 управления, импульс которого,пройдя через элемент ИЛИ 51, обнуляет счетчик 52.

Изменение коэффициента пересчета на цифровых входах 11 в любой момент при работе устройства ввода автоматически фиксируется делителем 22 частоты, что позволяет менять периодичность измерения смещений без останова работы устройства.

Таким образом, устройство ввода имеет большее быстродействие за счет формирования корректирующих напряже-- НИИ с опережением по отн ошению к мо - ментам подключения устройства к со - ответствующим измерительным каналам, а также за счет новых связей элемента задержки, обеспечивающих задержку запуска аналого-цифрового преобразования лишь при переходе в.режим измерения смещений.

Формула изобретения

i

1. Устройство для ввода информации, содержащее три коммутатора, сумматор,- три генератора импульсов, аналого-цифровой преобразователь, блок памяти, первьй элемент И, первьй формирователь импульса, элемерт ИЛИ, счетчик, делитель частоты, элемент задержки и цифроаналоговьй преобразователь, выходы счетчика соединены с адресными входами первого коммутатора, информационные входы Которого являются аналоговыми информационными входами устройства, а выход подключен к второму входу сумматора, первьй и третий входы которого сое- динены с выходами соответственно второго и третьего коммутаторов, а

выход соединен с информационным входом аналого-цифрового преобразователя, тактовьй вход и вход запуска которого подключены соответственно к выходам третьего генератора импульсов и первого формирователя импульса, информационные выходы аналого- цифрового преобразователя являются информационными выходами устройства, вход начальной установки делителя частоты, вход сброса счетчика и первый вход первого элемента И являются входом начальной установки устройства, выход первого элемента И подключен к входу первого генератора импульсов, входы предустановки делителя частоты являются цифровыми информационными входами устройства, инверсный выход делителя частоты соединен с входом чтения- записи блока памяти, управляющими входами второго и третьего коммутаторов, вторым входом первого элемента И и является выходом готовности устройства счетньй вход счетчика соединен с выходом элемента ИЛИ, первьй и второй входы которого соединены с вькодами соответственно первого и второго генераторов импульсов, второй вход второго коммутатора и первый вход тре- тьего коммутатора подключены к шине нулевого потенциала устройства, а второй вход третьего коммутатора подключен к шине потенциала 1/2 и,, где - опорное напряжение анало- го-и;ифрового и цифроаналогового преобразователей, отличающее- с я тем, что, с целью повьшения быстродействия устройства, в него введены буферные элементы, второй формирователь импульса, второй и третий элементы И, элемент ИЛИ-НЕ, блок управления, четвертьй и пятьй коммутаторы, регистры, группа цифроанало- говых преобразователей, выход готовности аналого-цифрового преобразователя соединен с входом второго формирователя импульса, BbKOfi, которого соединен с первым входом второго элемента И, входом третьего элемента И и тактовьм входом блока управления информационные выходы аналого-цифрового преобразователя соединены с входами первой группы буферных элементов, инверсньй выход делителя частоты соединен с входами второй группы буферных элементов, установочным входом блока управления, вторым вхо-

0

5

0

5

0

5

0

5

0

5

дом второго элемента И и управляющим входом пятого коммутатора, выходы которого соединены с адресными входами блока памяти, стробирующий вход которого соединен с выходом элемента 1ШИ-НЕ, первьй и второй входы которого соединены соответственно с выходами второго элемента И и второго генератора импульсов, выходы счетчика, соединены с входами группы треть- его элемента И и информационными вхот дами первой группы пятого коммутато - ра, выход третьего элемента И соединен-,, с тактовым входом делителя частоты, прямой выход которого через элемент задержки соединен с управляющим входом блока управления и входом второго генератора импульсов, вход сброса управления соединен с входом начальной установки делителя частоты, а выходы первой группы соединены со стробирующими входами соответствующих регистров, выход блока управления является выходом строби- рования устройства, выходы второй группы блока управления соединены с информационными входами второй группы пятого коммутатора, одни из выходов второй группы блока управления подключены к адресным входам четвертого коммутатора, выход которого соединен с первым входом второго коммутатора, выходы буферных элементов подключены к информационным входам- выходам блока памяти и информационным входам регистров, выходы кото- рык соединены с входами соответствующих цифроаналогового преобразователя и цифроаналоговых преобразователей группы, выходы которых соединены с информационными входами группы четвертого коммутатора, выход цифро- аналогового коммутатора соединен с информационным входом четвертого коммутатора.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит два элемента И, два элемента ИЛИ, формирователь импульса, счетчик, элемент И-НЕ, дешифратор, выходы которого являются выходами первой группы блока, первые входы элементов. И и стробирующий вход дешифратора являются тактовым входом блока, выходы первого и второго элементов И соединены соответственно с первым и вторым входами первого эле- .

X

яЗГ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации | 1987 |

|

SU1441377A1 |

| Устройство для считывания изображений | 1988 |

|

SU1645979A1 |

| Устройство для контроля работы транспортных средств | 1986 |

|

SU1446638A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПАРАМЕТРОВ УДАРНОГО ИМПУЛЬСА | 2006 |

|

RU2325661C1 |

| Преобразователь угла поворота вала в код | 1991 |

|

SU1833966A1 |

| Устройство для определения временного положения сигнала | 1985 |

|

SU1307442A1 |

| УСТРОЙСТВО ДЛЯ СЕЙСМИЧЕСКОГО ЗОНДИРОВАНИЯ ДНА ВОДОЕМОВ | 2002 |

|

RU2212692C1 |

| Устройство для отображения информации на экране телевизионного приемника | 1987 |

|

SU1494778A1 |

| Устройство для кодирования сигналов частотных датчиков | 1987 |

|

SU1564728A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

Устройство для ввода информации относится к области автоматики и измерительно-информационной техники и предназначено для коммутации и преобразования аналоговых сигналов. Целью изобретения является повышение быстродействия устройства. Устройство содержит три коммутатора, сумматор, три генератора импульсов, аналого-цифровой преобразователь, блок памяти, первый элемент И, первый формирователь импульса, элемент ИЛИ, счетчик, делитель частоты, элемент задержки и цифроаналоговый преобразователь. Новыми в устройстве являются буферные элементы, второй формирователь импульса, второй и третий элементы И, элемент ИЛИ-НЕ, четыре регистра, три цифроаналоговых преобразователя, четвертый и пятый коммутаторы и блок управления. Быстродействие в устройстве повышается за счет обеспечения возможности извлечения коэффициента коррекции из блока памяти и выработки корректирующего напряжения по каждому каналу еще до момента его подключения к входу. Кроме того, за счет новых взаимосвязей элемента задержки обеспечивается задержка запуска аналого-цифрового преобразователя на время, достаточное для перехода источников информации в режим измерения смещений при переходе в этот режим устройства ввода, и не оказывается ограничительное воздействие на длительность тактов опроса источников информации в режиме ввода. 1 з.п.ф-лы, 3 ил.

На23

izs37

Сриг.З

| Устройство для ввода информации | 1983 |

|

SU1164689A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для ввода информации | 1987 |

|

SU1441377A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-10-07—Публикация

1988-02-15—Подача