Изобретение, относится к импульсной технике и может нснользоваться в автоматических контрольно-измерительных системах.

Цель изобретения - повышение на- , и увеличение быстродействия устройства.

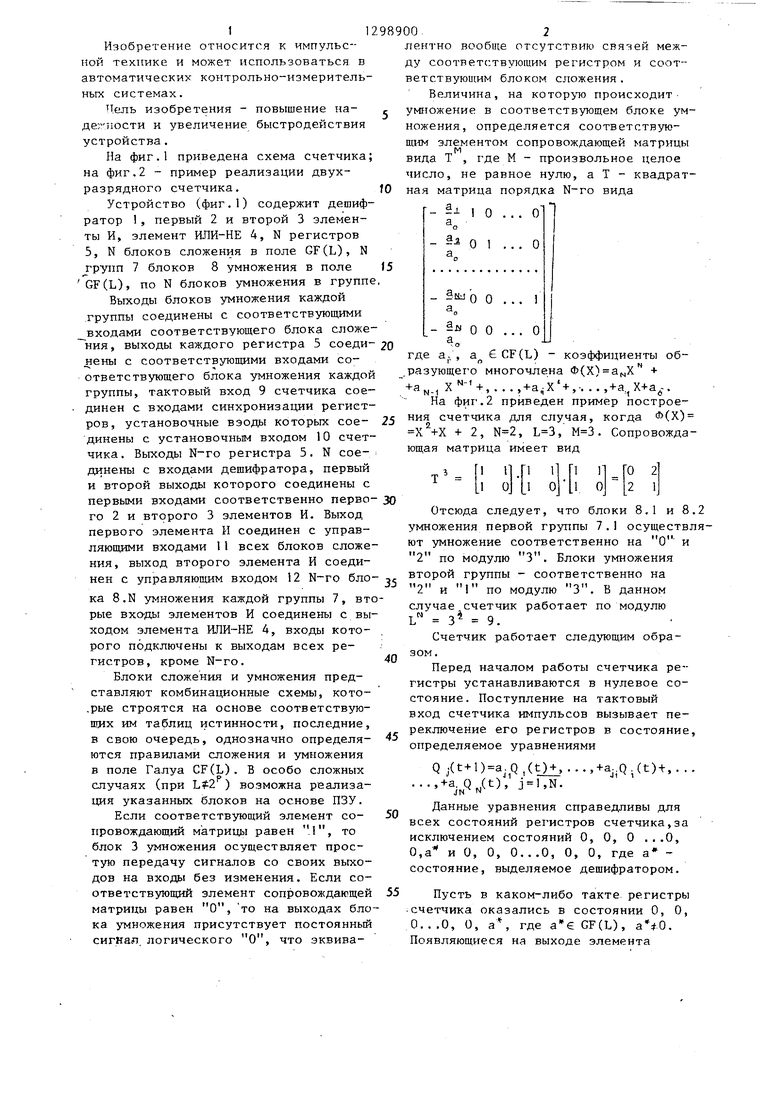

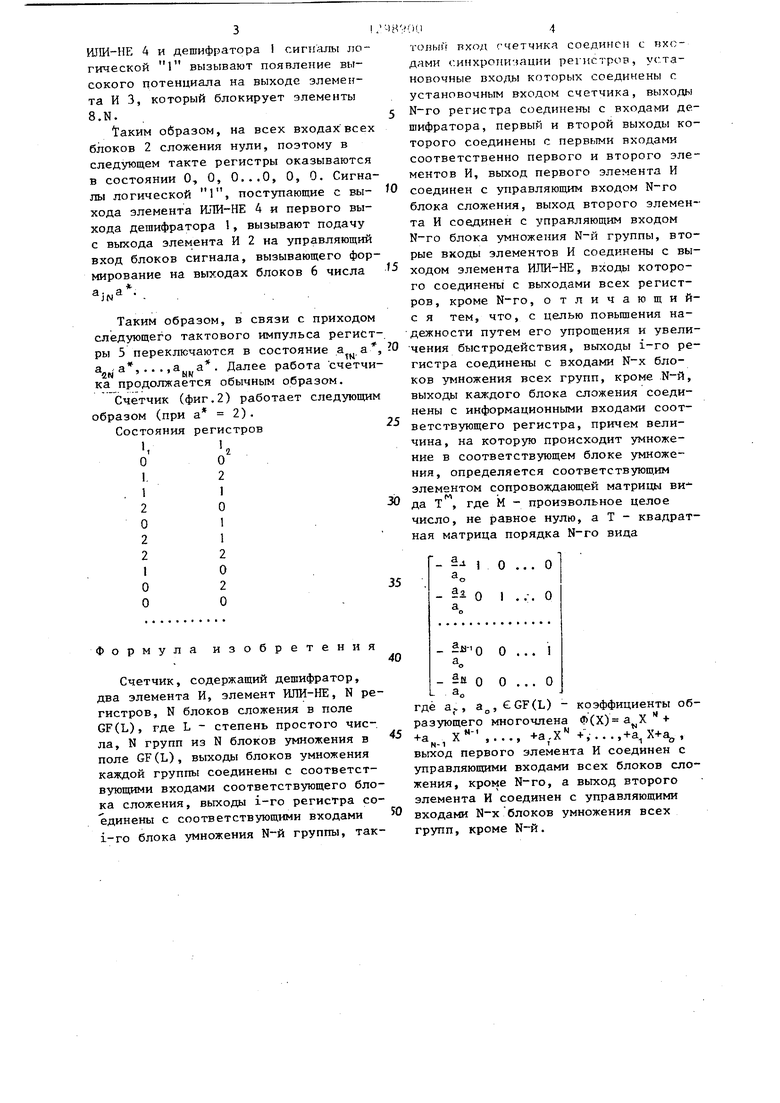

На фиг.1 приведена схема счетчика; на фиг.2 - пример реализации двухразрядного счетчика.}0

Устройство (фиг.1) содержит дешифратор 1, первый 2 и второй 3 элементы И, элемент ИЛИ-НЕ 4, N регистров 5, N блоков сложения в поле GF(L), N групп 7 блоков 8 умножения в поле 5 Ър(Ь), по N блоков умножения в группе,

Выходы блоков умножения каждой группы соединены с соответствующими входами соответствующего блока сложе- ния, выходы каждого регистра 5 соеди- 20 нены с соответствующими входами со- ответетвующего блока умножения каждой группы, тактовый вход 9 счетчика сое- динен с входами синхронизации регистров, установочные вэоды которых сое- 25 динены с установочным входом 10 счетчика. Выходы N-ro регистра 5. N соединены с входами дешифратора, первый и второй выходы которого соединены с первыми входами соответственно перво- 30 го 2 и второго 3 элементов И. Выход первого элемента И соединен с управляющими входами I1 всех блоков сложения, выход второго элемента И соедилентно вообще отсутствию связей м ду соответствующим регистром и со ветствующим блоком сложения.

Величина, на которую происходи ум 1ожение в соответствующем блоке ножения, определяется соответствую

щим элементом сопровождающей матр вида Т , где М - произвольное цел число, не равное нулю, а Т - квад ная матрица порядка N-ro вида

+я,., X

разующего многочлена Ф(Х) +

- +,...,,...., фи1 . 2 приведен пример постр ния счетчика для случая, когда ( xVx + 2, , , . Сопровож ющая матрица имеет вид

т

Р 1-Р 4

и о LI oj

Отсюда следует, что блоки 8.1 умножения первой группы 7.1 осуще ют умножение соответственно на 2 по модулю 3,

О Блоки умножени

иен с управляющим входом 12 N-ro бло- ,, второй группы - соответственно на

. . 2 и 1 по модулю 3. В данном

ка 8.N умножения каждой группы 7, вторые вхо-ды элементов И соединены с выходом элемента ИЛИ-НЕ 4, входы которого подключены к выходам всех регистров, кроме N-ro.

Блоки сложения и умножения представляют комбинационные схемы, кото- ,рые строятся на основе соответствующих им таблиц истинности, последние, в свою очередь, однозначно определяются правилами сложения и умножения в поле Галуа CF(L). В особо сложных случаях (при Lit2 ) возможна реализация указанных блоков на основе ПЗУ.

Если соответствующий элемент сопровождающий матрицы равен Л, то блок 3 умножения осуществляет простую передачу сигналов со своих выходов на входь без изменения. Если соответствующий элемент сопровождающей матрицы равен О, то на выходах блока умножения присутствует постоянный сигнал логического О, что эквива40

по модулю 3. В данном случае счетчик работает по модулю L 3 9.

Счетчик работает следующим обр зом.

Перед началом работы счетчика гистры устанавливаются в нулевое стояние. Поступление на тактовый вход счетчика импульсов вызывает п ., реключение его регистров в состоян определяемое уравнениями

Q j(t+l)a.Q,(t);S...,-ba..Q.(t)t .Q,(t), J 1,N.

Данные уравнения справедливы дл всех состояний рет истров счетчика исключением состояний О, О, О ...О 0,а и О, О, 0...0, О, О, где а - состояние, выделяемое дешифратором

50

55 Пусть в каком-либо такте регис счетчика оказались в состоянии О,

0...0, О, а

где GF(L),

Появляющиеся на выходе элемента

,

2989002

лентно вообще отсутствию связей между соответствующим регистром и соответствующим блоком сложения.

Величина, на которую происходит- ум 1ожение в соответствующем блоке умножения, определяется соответствующим элементом сопровождающей матрицы вида Т , где М - произвольное целое число, не равное нулю, а Т - квадратная матрица порядка N-ro вида

+я,., X

разующего многочлена Ф(Х) +

- +,...,,....,. На фи1 . 2 приведен пример построения счетчика для случая, когда (Х) xVx + 2, , , . Сопровождающая матрица имеет вид

т

Р 1-Р 4

и о LI oj

Отсюда следует, что блоки 8.1 и 8.2 умножения первой группы 7.1 осуществляют умножение соответственно на 2 по модулю 3,

О - и Блоки умножения

второй группы - соответственно на

2 и 1 по модулю 3. В данном

по модулю 3. В данном случае счетчик работает по модулю L 3 9.

Счетчик работает следующим образом.

Перед началом работы счетчика регистры устанавливаются в нулевое состояние. Поступление на тактовый вход счетчика импульсов вызывает пе- реключение его регистров в состояние, определяемое уравнениями

Q j(t+l)a.Q,(t);S...,-ba..Q.(t)t,... .Q,(t), J 1,N.

Данные уравнения справедливы для всех состояний рет истров счетчика,за исключением состояний О, О, О ...О, 0,а и О, О, 0...0, О, О, где а - состояние, выделяемое дешифратором.

55 Пусть в каком-либо такте регистры счетчика оказались в состоянии О, О,

0...0, О, а

где GF(L), .

Появляющиеся на выходе элемента

3

ИЛИ-НЕ А и дешифратора 1 сигналы логической 1 вызывают появление высокого потенциала на выходе элемента И 3, который блокирует элементы 8.N.

Таким образом, на всех входах всех блоков 2 сложения нули, поэтому в следующем такте регистры оказываются в состоянии О, О, 0...0, О, 0. Сигналы логической 1, поступающие с выхода элемента ИЛИ-НЕ 4 и первого выхода дешифратора 1, вызывают подачу с выхода элемента И 2 на управляющий вход блоков сигнала, вызывающего формирование на выходах блоков 6 числа

. . . .

Таким образом, в связи с приходом следующего тактового импульса региСтры 5 переключаются в состояние а а

2N

Ы«

ш,..,,а а . Далее работа счетчика продолжается обычным образом.

Счетчик (фиг.2) работает следующим образом (при а 2). Состояния регистров

Формула изобретения

Счетчик, содержащий дешифратор, два элемента И, элемент ИПИ-НЕ, N регистров, N блоков сложения в поле GF(L), где L - степень простого числа, N групп из N блоков умножения в поле GF(L), выходы блоков умножения каждой группы соединены с соответствующими входами соответствующего блока сложения, выходы i-ro регистра со- единены с соответствующими входами i-ro блока умножения N-Й группы, так

10

15

0

5

0

V(iO4

тоный вход гчетчика соединен с (- дями синхрони-.ишии регистров, ус.та- новочные входы которых соединены с установочным входом счетчика, выходы N-ГО регистра соединены с входами дешифратора, первый и второй выходы которого соединены с первыми входами соответственно первого и второго элементов И, выход первого элемента И соединен с управляющим входом N-ro блока сложения, выход второго элемента И соединен с управляющим входом N-ro блока умножения N-Й группы, вторые входы элементов И соединены с выходом элемента ИЛИ-НЕ, входы которого соединены с выходами всех регистров, кроме N-ro, о тличающий- с я тем, что, с целью повьш1ения надежности путем его упрощения и увели- чения быстродействия, выходы i-ro регистра соединены с входами N-X блоков умножения всех групп, кроме N-Й, выходы каждого блока сложения соединены с информационными входами соответствующего регистра, причем величина, на которую происходит умножение в соответствующем блоке умножения, определяется соответствуюш.им элементом сопровождающей матрицы вида Т , где М - произвольное целое число, не равное нулю, а Т - квадратная матрица порядка N-ro вида

40

разующего многочлена Ф(Х)а X +

N-1

N

+а, ,..., +а. +,-...,, выход первого элемента И соединен с управляющими входами всех блоков сложения, кроме N-ro, а выход второго элемента И соединен с управляющими входами N-X блоков умножения всех групп, кроме N-Й.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор псевдослучайных последовательностей | 1986 |

|

SU1465885A1 |

| Генератор цифровых последовательностей | 1987 |

|

SU1513449A1 |

| Генератор тестовых последовательностей | 1986 |

|

SU1388999A1 |

| Счетчик | 1986 |

|

SU1422403A1 |

| Запоминающее устройство с контролем информации | 1984 |

|

SU1288758A1 |

| Устройство для вычисления синдромов кода Рида-Соломона | 1990 |

|

SU1751860A1 |

| Устройство для формирования контрольного кода | 1986 |

|

SU1352489A1 |

| Генератор L-ичных последовательностей | 1986 |

|

SU1406586A1 |

| Многовходовой сигнатурный анализатор | 1987 |

|

SU1478219A1 |

| УСТРОЙСТВО КОДИРОВАНИЯ-ДЕКОДИРОВАНИЯ ИНФОРМАЦИИ | 1994 |

|

RU2115231C1 |

Изобретение относится к импульсной технике и может быть использоваг но в автоматических контрольно-измерительных системах. Цель изобретения - повышение надежности и увеличение быстродействия устройства. Устройство содержит дешифратор I, элементы И 2 и 3, элемент ИЛИ-НЕ 4, N регистров 5, N блокв 6 сложения, N групп 7 блоков 8 умножения по N бло- ков умножения в группе. Для достижения поставленной цели в устройство введены новые связи. 2 ил. to со 00 со

| Устройство для контроля двоичных последовательностей | 1983 |

|

SU1116431A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Генератор М-последовательности | 1985 |

|

SU1256162A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-03-23—Публикация

1985-11-26—Подача