--Н

(Л

И зобретенис относится к радиотех- 1шке и может быть использовано для синхронизации приемников сложных НгЗЛОЕ с псевдослучайной перестройкой рабочей 4iiCTOTbi, расположенных на движущихся объектах,

Цель изобретения - сокращение времени поиска после срыва захвата за счет сокращения анализируемой зоны неопределенности сложного сигнала.

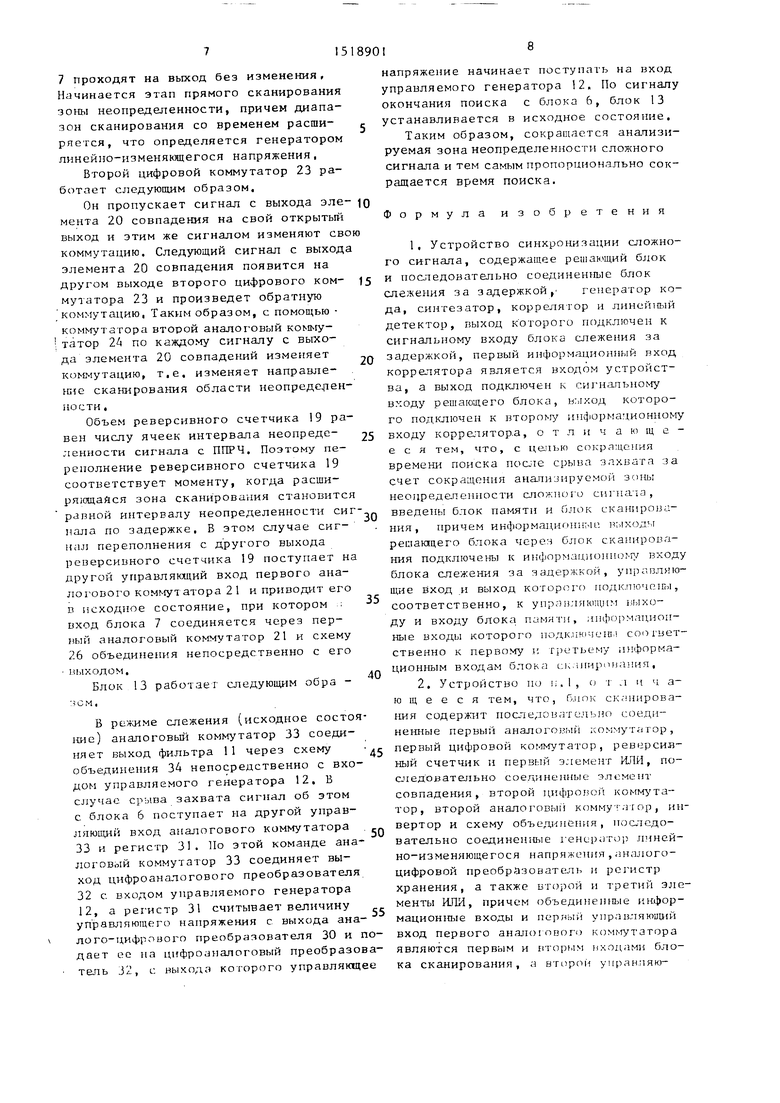

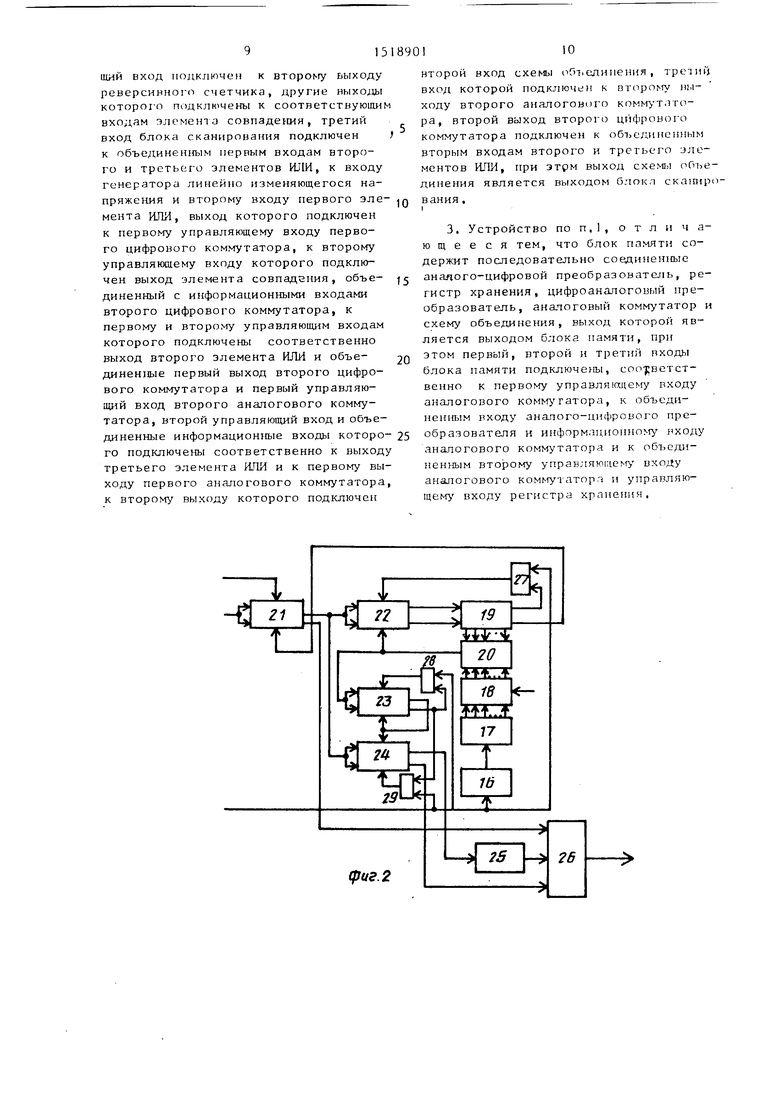

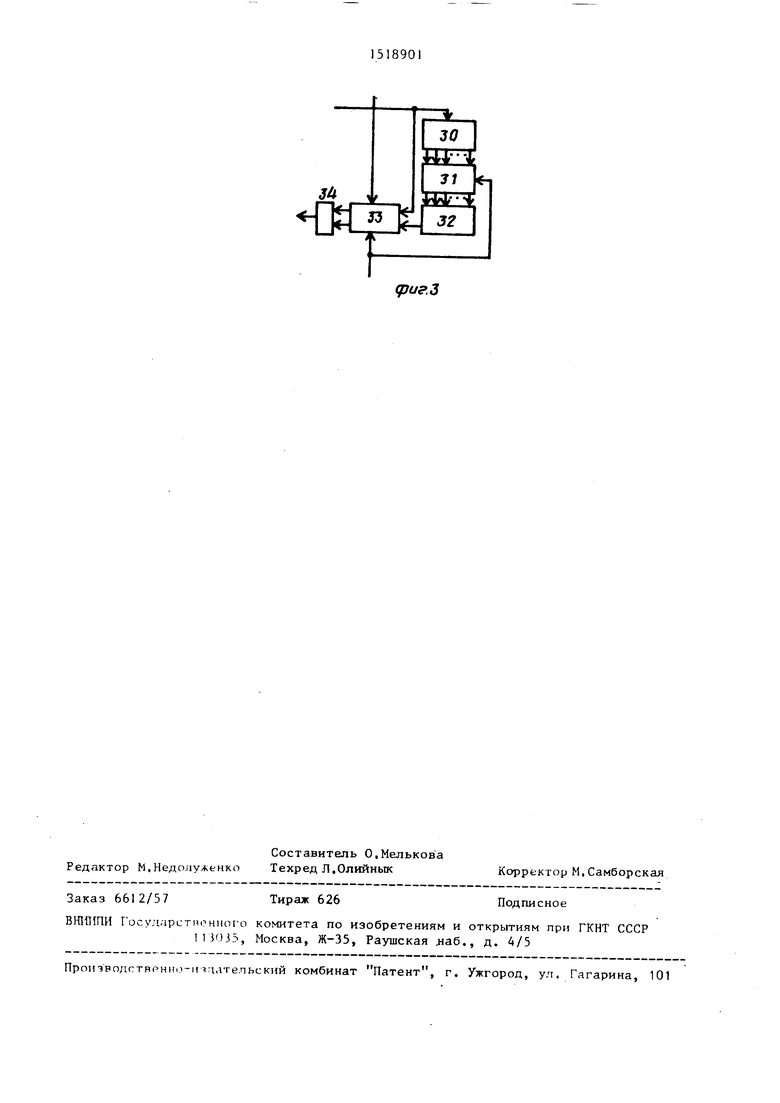

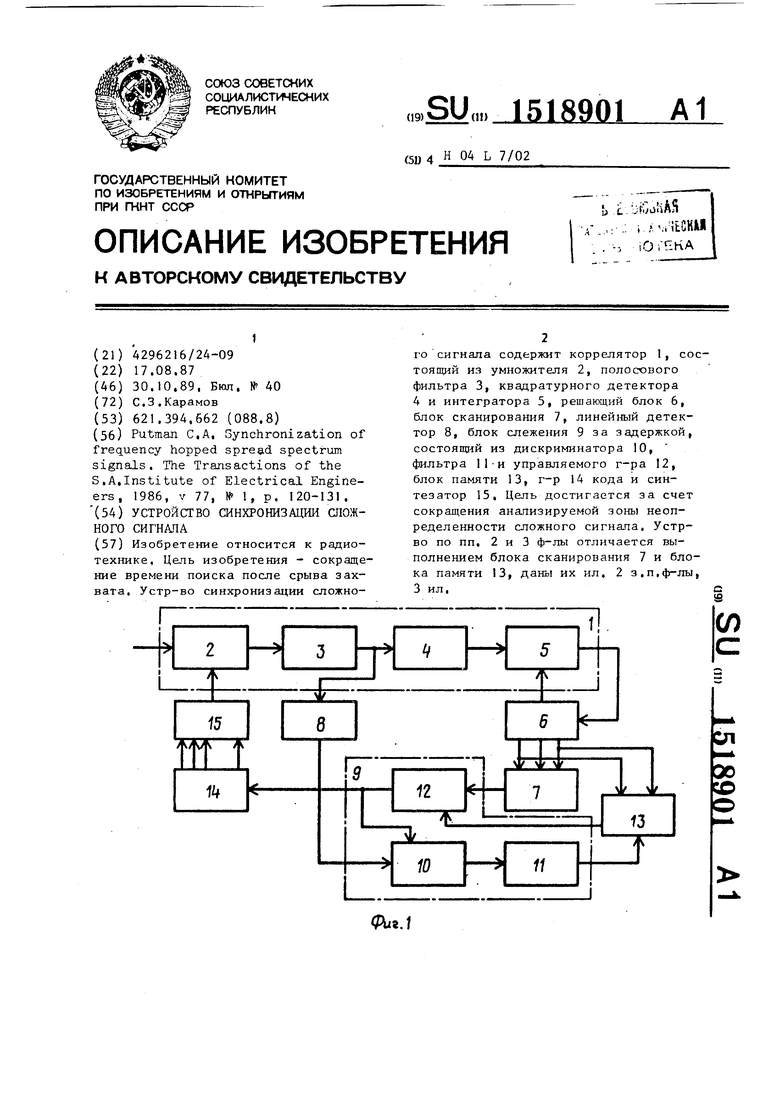

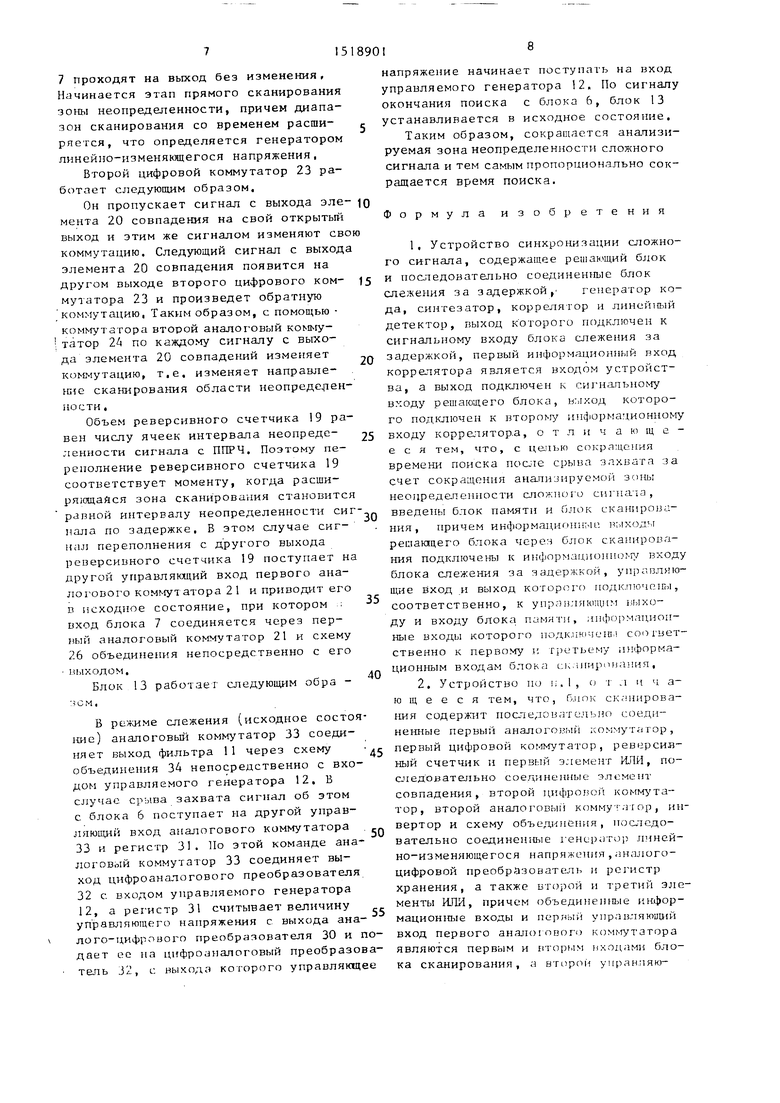

На фиг. 1 представлена схема yci- ройства синхронизации сложного сигнала; на фиг, 2 - структурно-электрическая схема блока сканирования; на фиг. 3 - структурно-электрическая схема блока памяти.

Устройство синхронизации сложного сигнала содержит коррелятор 1, состоящий из умножителя 2, полосового фильтра 3, КБа; ;ратурного детектора 4 и интегратора 5, решающий блок &, блок 7 сканирования, линейный детектор 8, блок 9 слежения за задержкой, состоящий из дискрими}1атора 10, фильтра 11 и yr:paвляe oгo генератора 12, блок 13 памяти, генератор 14 кода и синтезатор 15.

Блок 7 сканирования содержит генератор 16 линейно-изменяющегося напряжения , аналого-цифровой преобразователь 17, регистр 18 хранения, реверсивный счетчик 19, элемент 20 совпадения, первый аналот овый коммутатор 21 первый цифровой KOMNfyTaTOp 22 , второй цифровой KOMNryTaiop 23, второй аналоговый кoм fyтaтop 24, инвертор 25, схему 26 объединения, первы элемент ИЛИ 27, второй элемент 1ПИ 28 и третий элемент ШШ 29.

Блок 13 памяти содержит аналоге- , цифровой преобразователь 30, регистр 31 хранения, нифроаналог овый преобразователь 32, ана,-1оговый коммутатор 33 и схему обьодинения 34.

YcTpoiicTBo (Л1нхронизации сложного сигнала работает следующим образом,

В процессе нх(1ждения в связь уст- poi icTBo сиихр(1низации начинает работать гз режиме поиска. После начала приема входного сиг нала через период интегрирования, д:и1тельность которого задается блоком 6, с выхода коррелятора 1 снимается сигнал и поступает на вход iiopornHiM o устройства блока 6, Кслн урсчиень сиг ншш не превышает порог, уст.ии н.ченшлй п уюрогопом устройстве, то бпик 6 ч(рез блок 7 выдаст комлиду на у прл нлг емы| генератор

12 для cjiBura опорного с;и Г нап.ч , (fiop- ьгируемого синтезатором 15, на ллите-Л1 - ность элементарного символа опорного сигнала анализа очередной яче1г1ки интервала неопределенности.

Если уровень выходного сигнгик коррелятора 1 превышает пороговый уровень, установленный в нороговом устройстве,

Q то опорный сигнал не сдвигается , а

продолжается анализ той же ячейки интервала неопределенности, так как в зависимости от стратегии анализа ячейки интервала неопределенности, заложен5 ной в блоке 6, требуется несколько следуюодтх друг за другом превышений порога в пороговом устройстве для перехода в режим слежения.

Если число превышений порога еще

Q не достаточно для объявления об окончании поиска и перехода в режим слеже-- ния, а после очередного периода интегрирования выходной сигнал коррелятора 1 не превышает порог, то блок 6 через

5 блок 7 выдает команду на yпpaвляe ый генератор 12 для сдвига опорного сигнала .

Если выходной сигнал коррелятора превысит порог, з щанный в блоке 6

Q число раз, то блок 6 принимает решение об окончании поиска и прекращает выдачу управляющих сигналов через блок 7 на управляекый re)iepaTOp 12. Устройство синхронизации переходит в

режим слежения. Блок 9 входит в синхронизм и начинает слежение за задержкой входного .сигнала, чем заканчивается вхождение в связь.

В условиях действия помех или в случае кратковременных перерывов связи возможны срывы захвата блока 9,

Обнаружение факта срыва захвата осуществляется блоком 6, который в режиме слежения работает как индикатор захвата, В режиме слежения выходной -сигнал коррелятора 1, формируемый каждый период интегрирования, превышает установлеиш 1Й в пороговом устройстве порог. Для объявления срыва захвата наобходимо несколько следующих друг за другом непревьшений порога, причем число этих непревыше- ний порога выходным cnr-na,:iOM коррелятора установлено в б-пже 6,

После обнаружения cpi.iHa захвата блок 6 переходит в режим псиска и начинает работать так же, как и при первоначальном pxo)tuieiiiin и .вязь. Однако теперь команды HV.IX: да блока 6,

0

0

5

поступая на вход блока 7, либо проходят через него без изменения, либо инвертируются, т.е. меняют знак. При положительном знаке управляющего напряжения задержка опорного сигнала сдвигается на длительность элементарного символа в одну сторону, а при отрицательном - в другую сторону относительно задержки входного сигнала, причем зак:он изменения расширяющейся зоны сканирования установлен в блоке 7 с учетом нелинейности скорости изменения задержки,

Реверсивный счетчик 19 начинает счет числа управляющих сигналов. На каждом шаге через период интегрирова ния записанная в реверсивном счетчике 19 величина сравнивается в схеме сравнения блока 6 с амплитудой сигна ла генератора 16, сигнал которого пр образуется в цифровую форму аналогоцифровом преобразователе t 7 и периодически на каждом шаге записывается в .регистр 18, Если величина, записанПри этом, блок 13 продолжает выда- 15 ная- 3 реверсивном счетчике 19 совпа- вать на вход управляемого генерато- дает с амплитудой сигнала генератора ра 12 управляющее напряжение, соответствующее скорости изменения задер16, то на выходе элемента 20 сравнения появляется сигнал, по которому первый цифровой коммутатор 22 соединяет вход первого аналогового коммутатора 21 с обратным входо }} реверсивного счетчика 19, а второй цифровой коммутатор 23 управляет вторым аналоговым коммутатором 24, который соединяет выход первого аналогового коммутатора 21 с входом инвертора 25 В этом случае все управляющие сигнал с входа блока 7 проходят на его выхо сменив свою полярность, С момента п явления сигнала на выходе элемента 20 сравне11ия начинается этап обратног сканирования зоны неопределенности, В реверсивном счетчике 19 происходив счи тывание импульсов, После полного считы вания, когда реверсивный счетчик 19 обн лен, на выхода реверсивного счетчика по является сигнал, который через первый элемент ИЛИ,27 проходит на управляющи вход первого цифрового кoм ryтaтopa 2 который по этому сигналу соединяет выход первого аналогового коммутатора 21 с прямым входом реверсивного счетчика 19, В реверсивном счетчике 19 начинается прямой счет управляющи сигналов до очередного совпадения с амплитудой сигнала, формируемого генератором 16, При совпадении выходной сигнал с элемента 20 совпадения поступает на другой управляю1ций вход первого цифрового коммутатора 22, который по этой команде соединяет вы ход первого аналогового KONn-гутатора 2 I с прямым входом реверсивного счетчика 19, Выходной сигнал с элемента 20 поступает также на вход второго цифрового коммутатора 23, ко-горый по этой команде изменяет коммутацию второго аналового коммутатора 24 так, что управляющие сигналы с входа блока

жки входного сигнала на момент срыва захвата, что позволяет сдвигать опорный сигнал с постоянной скоростью, равной скорости изменения задержки на момент срыва захвата,

В режиме поиска после срыва захвата обнаружение сигнала осуществляется так же, как и при первоначальном поиске, однако диапазон сканирования, т.е, зона неопределенности, просматриваемая устройством синхронизации, значительно меньше, чем при первоначальном вхождении в связь, когда последовательно просматривается весь диапазон неопределенности по задержке, как правило, равный периоду входного сигнала,

Блок 7 работает следуюшлм образом. При первоначальном вхождении в связь первый аналоговый коммутатор 21 соединяет вход блока 7 через схему 26 непосредственно с его выходом. По сигналу окончания поиска с выхода счетчика поиска блока 6 первый аналоговый комьгутатор 21 соединяет вход блока 7 с входом первого цифрового комутатора 22,

В случае срыва захвата на вход первого цифрового коммутатора 22 через первый аналоговый коммутатор 21 начинают поступать управляющие сигналы с выхода блока 6, По сигналу срыва захвата с выхода счетчика слежения бло- ка 6 генератор 16 устанавливается в исходное.состояние, первый цифровой коммута1-6р 22 соединяет выход первого ан алоговог о коммутатора 21 с прямым входом реверсивного счетчика 19, а второй аналоговый коммутатор 24 соединяет выход первого аналогового коммутатора

с выходом блока 7

21 непосредственно через схему 26,

Реверсивный счетчик 19 начинает счет числа управляющих сигналов. На каждом шаге через период интегрирования записанная в реверсивном счетчике 19 величина сравнивается в схеме сравнения блока 6 с амплитудой сигнала генератора 16, сигнал которого преобразуется в цифровую форму аналогоцифровом преобразователе t 7 и периодически на каждом шаге записывается в .регистр 18, Если величина, записан ная- 3 реверсивном счетчике 19 совпа- дает с амплитудой сигнала генератора

5 ная- 3 реверсивном счетчике 19 совпа- дает с амплитудой сигнала генератора

0

5

0

5

0

5

0

5

16, то на выходе элемента 20 сравнения появляется сигнал, по которому первый цифровой коммутатор 22 соединяет вход первого аналогового коммутатора 21 с обратным входо }} реверсивного счетчика 19, а второй цифро вой коммутатор 23 управляет вторым аналоговым коммутатором 24, который соединяет выход первого аналогового коммутатора 21 с входом инвертора 25, В этом случае все управляющие сигналы с входа блока 7 проходят на его выход, сменив свою полярность, С момента появления сигнала на выходе элемента 20 сравне11ия начинается этап обратного сканирования зоны неопределенности, В реверсивном счетчике 19 происходив считывание импульсов, После полного считывания, когда реверсивный счетчик 19 обнулен, на выхода реверсивного счетчика появляется сигнал, который через первый элемент ИЛИ,27 проходит на управляющий вход первого цифрового кoм ryтaтopa 22, который по этому сигналу соединяет выход первого аналогового коммутатора 21 с прямым входом реверсивного счетчика 19, В реверсивном счетчике 19 начинается прямой счет управляющих сигналов до очередного совпадения с амплитудой сигнала, формируемого генератором 16, При совпадении выходной сигнал с элемента 20 совпадения поступает на другой управляю1ций вход первого цифрового коммутатора 22, который по этой команде соединяет выход первого аналогового KONn-гутатора 2 I с прямым входом реверсивного счетчика 19, Выходной сигнал с элемента 20 поступает также на вход второго цифрового коммутатора 23, ко-горый по этой команде изменяет коммутацию второго аналового коммутатора 24 так, что управляющие сигналы с входа блока

7 проходят на выход без изменения, Начинается этап прямого сканирования зоны неопределенности, причем диапазон сканирования со временем расши- с ряется, что определяется генератором линейно-изменяющегося напряжения,

Второй цифровой коммутатор 23 работает следующим образом.

Он пропускает сигнал с выхода эле- ю мента 20 совпадения на свой открытый выход и этим же сигналом изменяют свою коммутацию. Следующий сигнал с выхода элемента 20 совпадения появится на другом выходе второго цифрового ком- 15 мутатора 23 и произведет обратную коммутацию, Таким образом, с помощью ком гутатора второй аналоговый комму- татор 2А по каждому сигналу с выхода элемента 20 совпадений изменяет коьшутацию, т.е. изменяет направле- скаьщрования области неопредс ен- иости.

Объем реверсивного счетчика 19 равен числу ячеек интервала неопреде- 25 jteHHocTH сигнапа с ППРЧ. Поэтому переполнение реверсивного счетчика 19 соответствует моменту, когда расши- ряющайся зона сканирования становится равной интервалу неопределенности сиг- пала по задержке, В этом случае сигнал переполнения с другого выхода реверсивного счетчика 19 поступает на другой управляющий вход первого аналогового коммутатора 21 и приводит его D исходное состояние, при котором ; вход блока 7 соединяется через пер- иый аналоговый коммутатор 21 и схему 26 объединения непосредственно с его

В 1ХОДОМ,

Блок 13 работает следующим обра - ;iCM,

В режиме слежения (исходное состояние) аналоговый коммутатор 33 соединяет выход фильтра 11 через схему объединения ЗА непосредственно с входом управляемого генератора 12, В случае срыва захвата сигнал об этом с блока 6 поступает на другой управляющий вход аналогового коммутатора , 33 и регистр 31. По этой команде ана- логовош коммутатор 33 соединяет выход цифроаналогового преобразователя 32 с входом управляемого генератора 12, а регистр 31 считывает величину управляющего напряжения с выхода аналого-цифрового преобразователя 30 и подает ео па цифроаналоговый преобразователь 32, с выхода которого управляющее

35

40

45

50

55

5

0

5

0

5

напряжение начинает поступать на вход управляемого генератора 12, По сигналу окончания поиска с блока 6, блок 13 устанавливается в исходное состояние.

Таким образом, сокращается анапизи- руемая зона неопределенности сложного сигнала и тем самым пропорционально сокращается время поиска.

Формула изобретения

1,Устройство синхронизации сложного сигнала, содержащее решающий блок

и последовательно соединенные блок слежения за задержкой, генератор кода, синтезатор, коррелятор и линейный детектор, выход которого подключен к сигнальному входу блока слежения за задержкой, первый информационный вход коррелятора является входом устройства, а выход подключен к сиг нааьному входу решающего блока, ь:)1ход которого подключен к второму информационному входу коррелятор.а, отличающееся тем, что, с целью сокра цс11ия времени поиска после срыва злхвата за счет сокращения анализируемой зоны неоцредепенпости сложного сигнала, введены блок памяти и блок сканирования, причем информационные- 1 ыходы решаюсцего блока черен блок сканирования подключены к информациошюму входу блока слежения за задержкой, управляющие вход ц выход которого подключен;), соответственно, к упрапляющим мыхо- ду и входу блока памяти, информлциоп- ные входы которого подк.ишчеп соответственно к первому и третьему информационным входам блока с:1ч лпирпнаиня ,

2,Устройство по li, 1 , о т л и ч а- ю щ е е с я тем, что, блок сканнрова- 1-шя содержит гюследонательно ссзеди- ненные первый аналоговый коммутатор, первый цифровой ког-1мутатор, реверсия- ный счетчик и первь1й элемент ИЛИ, последовательно соединенные элемент совпадения, второй цифровой комм, та- тор, второй аналоговый коммут.чгор, инвертор и схему объеднибния, последовательно соединенные генсрато; тшней- но-изменяющегося напряжения,аналого- цифровой преобразователь и регистр хранения, а также второй и третий элементы ИЛИ, причем объединенюяе информационные входы и перяы11 управляю11Ц1Й вход первого аналогового коммутатора являются первым и вторым вхоцами блока сканирования, а второй управляю913

щий вход подключен к втopo гy выходу реверсивного счетчика, другие выходы KOTopoi O подключены к соответствующим входам элеменпа совпадения, трети 1 вход блока сканирования подключен к объединенным первым входам второго и третьего элементов ИЛИ, к входу генератора линейно изменяющегося напряжения и второму входу первого эле- мента ИЛИ, выход которого подключен к первому управляющему входу первого цифрового коммутатора, к второму управляющему входу которого подключен выход элемента совпадения, объе- диненный с информационными входами второго цифрового коммутатора, к первому и второму управляющим входам которого подключены соответственно выход второго элемента ИЛИ и объе- динениые первый выход второго цифрового коммутатора и первый управляющий вход второго аналогового коммутатора, второй управляющий вход и объединенные информациан№1е входы которо- го подключены соответственно к выходу третьего элемента ИЛИ и к первому выходу первого аналогового коммутатора к второму выходу которого подключен

10

второй вход схемы оОт.едииения, третш} вход которой подключили к втopo гy пы- ходу второго аналогового коммут.гго- ра, второй выход второго цифрового коммутатора подключе} к объединенным вторым входам второго и третьего элементов ИЛИ, при этрм выход )l оОъе динения является выходом блокл cKainip вания.

3. Устройство по п,1, о т л и ч а- ю щ е е с я тем, что блок памяти содержит последовательно соединен1ше аналого-цифровой преобразователь, регистр хранения, цифроаналоговый преобразователь, аналоговый коммутатор и схему объединения, выход которой является выходом блока памяти, при этом первый, второй и третий входы блока памяти подключены, соо ветст- венно к первому управля1сщему входу аналогового комм гатора, к объединенным входу аналого-цифрового преобразователя и информлционно гу иходу аналогового коммутатора и к объединенным BTOJpOMy управляющему входу аналогового KOMNfyraropa и управляю- входу регистра хранения,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство поиска шумоподобных сигналов | 1989 |

|

SU1653170A1 |

| ПРИЕМНОЕ УСТРОЙСТВО ШИРОКОПОЛОСНЫХ СИГНАЛОВ | 1983 |

|

SU1840292A1 |

| Устройство поиска шумоподобного сигнала | 1982 |

|

SU1095433A2 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНЫХ СИГНАЛОВ | 1985 |

|

SU1840080A1 |

| Телевизионный координатор | 1983 |

|

SU1109956A1 |

| Устройство поиска шумоподобных сигналов | 1981 |

|

SU978377A1 |

| УСТРОЙСТВО ПОИСКА ШУМОПОДОБНОГО СИГНАЛА | 1990 |

|

RU2007044C1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1990 |

|

RU2040857C1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| АДАПТИВНОЕ УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ЗАДЕРЖКОЙ ШИРОКОПОЛОСНОГО СИГНАЛА | 1990 |

|

RU2040856C1 |

Изобретение относится к радиотехнике. Цель изобретения - сокращение времени поиска после срыва захвата. Устройство синхронизации сложного сигнала содержит коррелятор 1, состоящий из умножителя 2, полосового фильтра 3, квадратурного детектора 4 и интегратора 5, решающий блок 6, блок сканирования 7, линейный детектор 8, блок слежения 9 за задержкой, состоящий из дискриминатора 10, фильтра 11 и управляемого генератора 12, блок памяти 13, генератор 14 кода и синтезатор 15. Цель достигается за счет сокращения анализируемой зоны неопределенности сложного сигнала. Устройство по пп.2 и 3 ф-лы отличается выполнением блока сканирования 7 и блока памяти 13, даны их ил. 2 з.п. ф-лы, 3 ил.

Редактор М.Недолуженко

Составитель О.Мелькова Техред Л.Олийнык

Заказ 6612/57

Тираж 626

ВШИШИ Госуларстпениоро комитета по изобретениям и открытиям при ГКНТ СССР ПЗОЗЗ, Москва, Ж-35, Раушская лаб., д. А/5

Прои-эродстяриим-и чаате.пьский комбинат Патент, г. Ужгород, ул. Гагарина, 101

дзиг.З

Корректор М.Самборская

Подписное

| Putman С,А, Synchronization of frequency hopped spread spectrum signals | |||

| The Transactions of the S.A,Institute of Electrical Engineers, 1986, V 77, № 1, p | |||

| Кровля из глиняных обожженных плит с арматурой из проволочной сетки | 1921 |

|

SU120A1 |

Авторы

Даты

1989-10-30—Публикация

1987-08-17—Подача