1

(21)4320172/24-24

(22)31.08.87

(46) 07.11.89. Бюл. № 41

(71)Институт кибернетики им.В.М.Глушкова

(72)Й.В.Самус

(53)681.325 {088.8)

(56)Авторское свидетельство СССР № 1018231, кл. Н 03 М 1/46, 1981.

Цифровые электроизмерительные приборы./Под ред.В.М.Шляндина, 1972, с.271-272, рис.6-19,

(54)БИПОЛЯРНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ

(57)Изобретение относится к вычислительной технике и может быть использовано в качестве самостоятельного модуля или составной части устройств, в которых осуществляется преобразование аналоговых сигналов в цифровые коды преобразователя. Цель изобретения - повьпаение точности. Цель достигается введением в аналого-цифровой преобразователь дополнительного компаратора, цифрового переключателя, коммутатора и элемента ИСКЛЮ- ЧДШЩЕ ИЛИ, что позволяет обеспечить рщентичность преобразования по-г ложительных и отрицательных входных величин,- ликвидировать погрешности, обусловленные переходными процессами при переключении разрядов цифроанало- гового преобразователя, компенсировать аддитивную и уменьшить мультипликативную составляющие погрешности цифроанапоговых преобразователей, а также устранить влияние дрейфа порога срабатьшания компараторов в пределах одного кванта, на точность аналого-цифрового преобразования. ; 1 ил.

с

(О

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательно-параллельный аналого- цифровой преобразователь | 1978 |

|

SU743193A1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1378061A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1986 |

|

SU1473083A1 |

| Аналого-цифровой преобразователь | 1979 |

|

SU879770A1 |

| Преобразователь кода во временной интервал | 1985 |

|

SU1300637A1 |

| Преобразователь сигналов датчиков переменного тока | 1986 |

|

SU1332531A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Устройство для измерения уровней сигнала изображения | 1987 |

|

SU1520672A1 |

Изобретение относится к вычислительной технике и может быть использовано в качестве самостоятельного модуля или составной части устройств, в которых осуществляется преобразование аналоговых сигналов в цифровые коды преобразователя. Цель изобретения - повышение точности. Цель достигается введением в аналого-цифровой преобразователь дополнительного компаратора, цифрового переключателя, коммутатора и элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, что позволяет обеспечить идентичность преобразования положительных и отрицательных входных величин, ликвидировать погрешности, обусловленные переходными процессами при переключении разрядов цифроаналогового преобразователя, компенсировать аддитивную и уменьшить мультипликативную составляющие погрешности цифроаналоговых преобразователей, а также устранить влияние дрейфа порога срабатывания компараторов в пределах одного кванта на точность аналого-цифрового преобразования. 1 ил.

Изобретение относится к вычислительной технике и может быть использовано в качестве самостоятельного модуля или составной части устройств, в которых осуществляется преобразование аналоговых сигналов в цифровые коды.

Цель изобретения - повышение точности преобразователя.

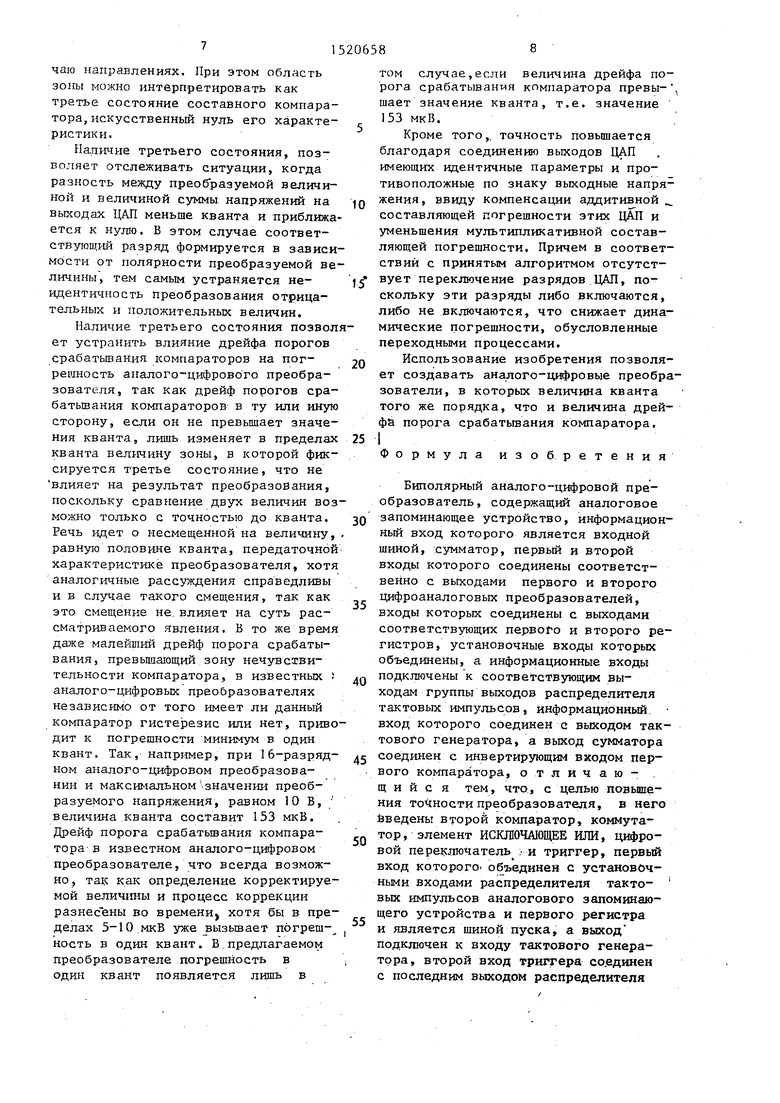

На чертеже изображена структурная схема аналого-цифрового преобразователя.

Преобразователь содержит триггер 1, аналоговое запоминающее устройство 2, сумматор 3, тактовый генератор 4, первый 5 и второй 6 компараторы ( )- разрядный распределитель 7 тактовых импульсов (п - число разрядов предлагаемого аналого-цифрового преобразователя), коммутатор 8, элемент ИСКЛ10ЧАЩЕЕ ИЛИ 9, первый 10 и второй }Г (п+1)-разрядные регистры, первый п-разрядный цифроаналого- вый преобразователь (ЦАП) 12, цифровой переключатель 13 и второй п-раз- рядный ЦАП 1 4.

Компараторы подобраны по критерию ццентичности параметров.

Аналого-цифровой преобразователь работает следующим образом.

В исходном состоянии на выходе триггера 1 установлен уровень логического О, что запрещает прохождение тактовых импульсов с вькода тактового генератора 4 на счетный вход

распределителя 7 тактовых импульсов. С приходом запускающегб импульса на установочные входы распределителя 7 тактовых импульсов первого 10 и вто- рого 11 регистров на их выходах устанавливаются уровни логического О, что, в свою очередь, вызьшает появление нулевых уровней напряжения на в-ыходах первого, 12 и второго 14 ЦАП и, соответственно, на выходе сумматора 3, Этим же импульсом разрешается запоминание преобразуемого напряжения в аналоговом запоминающем устройстве 2, а также взводится триггер 1. При этом разрешается прохождение тактовых импульсов с выхода тактового генератора 4 на вход распределителя 7 тактовых импульсов, По окончании запускающего импульса процесс запоминания в аналоговом запоминающем устройстве 2 прекращается. Таким образом, на неинвертирующем входе основного 5 и инвертирующем входе дополнительного 6 компараторов устанавливается значение преобразуег: мого напряжения, а на инвертирующем входе основного 5 и неинвертирующем входе дополнительного 6 компараторов - значение напряжения, снимаемого с выхода сумматора 3,, которое равно сумме выходных напряжений первого ЦДЛ 12, вырабатывающего напряжение положительной полярности, и второго ЦАП 14, вырабатьшающего напряжение отрицательной полярности. В певый моме,нт напряжение на выходе сумп матора 3 равно нулю.

Если не учитывать дрейф порога срабатьшания, то коьшаратор 5 должен реализовать функцию

ок

1 , при и... и.

де а

он.

вх

ВХ -

- логическое состояние на

О, при.Пр и.

выходе компаратора 5; . и „ - значение преобразуемого

напряжения;

и. - суммарное значение выходных напряжений первого 12 и второго 14 ЦАП

и -и.

+

цдп,

а компаратор 6, по ч ения, функ цию

- а

АК

1 , при Ug и, О, при Ug и

где ад - логическое состояние на

выходе компаратора 6. С учетом дрейфа пароги срабатывания компараторов 5 и 6 смещены относительно нуля, но, в связи с принятым способом соединения входов компараторов , смещены в противоположных направлениях, что используется для формирования третьего состояния, которое соответствует равенству сравниваемых напряжений с точностью до кванта. В этом случае на выходах компараторов 5 и 6 устанавливаются иден- т.ичные логические состояния, что и фиксируется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ §,на выходе которого устанавливается состояние логического О. Тем самым блокируется прохождение сигнала с выхода компаратора 5 на выходы коммутатора 8, а состояние выходов коммутатора 8 определяется знаковым выходом цифрового переключателя 13, т.е. реализуется функция..

5

к

I , если + i/CUgjj), если

О, если UBX

УЭ

+Ui

( Ug)

S.

(Us:+Ua) Ug,Ug. -« Ug

где а, - логическое состояние на прямом выходе коммутато-. ра, 8;

и - напряжение.дрейфа порога срабатьшания компараторов 5 и 6, причем должно выпол- няться условие Ug U, где Uj - значение напряжения -кванта;

единичная функция, определяемая как

F(U«J

ВХ

F(b)

1, при Ug О О, при Ug О

Так как дрейф порога срабатывания компараторов имеет место в любом случае, то величина зоны третьего состояния заведомо не равна нулю.

С приходом фронта первого тактово импульса состояние прямого и инверсного выходов коммутатора 8, которое на прямом выходе, если не установле- но третьей состояние, тождественно состоянию выхода компаратора 5, а на инверсном - противоположно ему записывается соответственно в первые разряды первого 10 и второго 11 ре-т гистров. Причем, если преобразуемое напряжение положительно , то на выходе компаратора 5 устанавливается 1 так как U Ug-,, которая и записывается в первый регистр 10, тем са- мым включается первый разряд ЦАП 12, Во второй регистр 11 записьшается О, и первьй разряд ЦАП 14 не включается. Если преобразуемое напряжение отрицательно, то на выходе компаратора 5 устанавливается уровень О,

так как Ug : Ug-,, ив этом случае первый разряд . первого регистра 10 записьшается О, а второго - 1, что приводит к включению первого разряда ЦАП 14 и не включению первого разряда ЦАП 12. Таким образом, определяется знак преобразуемого напряжения.

Как только определена полярность преобразуемого напряжения, цифровой переключатель 13 подключает выходы преобразователя к выходам первого регистра 10 при положительной полярности или к выходам второго регистра 1 1 в случае отрицательной полярности.

По фронту второго тактового импульса -во вторые разряды регистров 10 и 11 записьшается следующий результат сравнения преобразуемой величины и суммы выходных величин ЦДЛ 12 и 14. При этом, если преобразуемая величина по абсолютному значению больше значения сумм выходных величин ЦАП 12 и 14 то включается второй разряд ЦАЛ 12 и не включается второй разряд ЦАП 14, если меньше, то не включается второй разряд ЦАЛ 1 и включается второй разряд ЦАП 14, Определение остальных разрядов кода происходит аналогично, с той лишь разницей, что при возникновении третьего состояния состояния искусственного нуля, на прямом выходе коммутатора.8 устанавливается уровень 1 в .случае положительной полярности преобразуемой величины и

уровень О в спучае отрлд. телы-: : полярности, независимо от состояи.п.ч сигнала на выходе компаратора 5, что и определяет включение или не вклоче- ние соответствующих разрядов ЦДП 12 и 14. С приходом фронта (n+i)-го тактового импульса в первый IО и второй 11 регистры записьшается значение последнего разряда кода и одновременно сбрасывается триггер 1. Прохождение тактовых импульсов запрещается и процесс аналого-цшЬрово- го преобразования прекращается. Результат преобразования снимается с выходов цифрового переключателя 13,,

Повышение точности предлагаемого биполярного аналого-цифрового преобразователя достш ается за счет отслеживания ситуации, когда модуль разности преобразуемой величины и суммы выходных величин ЦАП становится меньше значения кванта и приближается к нулю. Причем сама зона,в которой отслеживаются эти ситуации, создается за счет дрейфа порога срабатывания основного и Дополнительного компараторов, поскольку значения этого дрейфа при идентичности параметров компараторов примерно равны, но из-за принятого способа включения входов компараторов их пороги сраба- тьшания смещаются в противоположные направления. Идентичности параметров компараторов можно добиться либо подбором компараторов в пары, либо исполнением их в одном корцусе на одном кристалле, Тем более, что необходимо и достаточно лишь, чтобы в каждом отдельном компараторе дрейф происходил в одном направлении, а величины этих дрейфов были примерно равны. При этом предполагается, что начальное смещение порогов сраба- тьюания компараторов скомпенсировано. Так как в реальных компараторах дрейф всегда имеет место то величина зоны третьего состояния не равна Нулю в любом случае. Признаком попадания в зону является формирование на выходах компараторов одинаковых логических состояний: состоянию логического О на выходах компаратор ров соответствует смещение порога срабатывания первого компаратора вправо от нуля, а второго - влево; состояние возникает при смещении в противоположных предыдущему слу

чаю направлениях. При этом область зоны можно интерпретировать как третье состояние составного компаратора, искусственный нуль его характеристики.

Напичие третьего состояния, позволяет отслеживать ситуации, когда разность между преоб разуемой величиной и величиной суммы напряжений на выходах ЦАП меньше кванта и приближается к нулю. В этом случае соответствующий разряд формируется в зависи- мбсти от полярности преобразуемой величины, тем самым устраняется неидентичность преобразования отрицательных и положительных величин.

Наличие третьего состояния позволет устранить влияние дрейфа порогов срабатьшания компараторов на погрешность аналого-цифрово го преобразователя, так как дрейф порогов срабатьшания компараторов в ту или иную сторону, если он не превышает значения кванта, лишь изменяет в пределах кванта вел1-1чину зоны, в которой фиксируется третье состояние, что не влияет на результат преобразования, поскольку сравнение двух величин возможно только с точностью до кванта. Речь идет о несмещенной на величину, равную половине кванта, передаточной характеристике преобразователя, хотя аналогичные рассуждения справедливы и в случае такого смещения, так как это смещение не. влияет на суть рассматриваемого явления. В то же время даже малейший дрейф порога срабатывания, превышающий зону нечувствительности компаратора, в известных аналого-цифровых преобразователях независимо от того имеет ли данный компаратор гистерезис или нет, приводит к погрешности минимум в один квант. Так, например, при 16-разрядном аналого-цифровом преобразовании и максимальном значении преобразуемого напряжения, равном 10В, величина кванта составит 153 мкБ. Дрейф порога срабатывания компаратора в известном аналого-цифровом преобразователе, что всегда возможно, так как определение корректируемой велич1гаы и процесс коррекции разнесены во времени, хотя бы в пределах 5-10.мкВ уже вызьшает погреш- ность в один квант. В.предлагаемом преобразователе погрешность в один квант появляется лишь в

5

0

5

0

5

0

5

0

5

том случае,если величина дрейфа порога срабатывания компаратора превы- шает значение кванта, т.е. значение 153 мкВ.

Кроме того,, точность повьш1ается благодаря соединению выходов ЦАП имеющих идентичные параметры и противоположные по знаку выходные напряжения, ввиду компенсации аддитивной составляющей погрешности этих ЦАП и уменьшения мультипликативной составляющей погрешности. Причем в соответствий с принятым алгоритмом отсутствует переключение разрядов ЦАП, поскольку эти разряды либо включаются, либо не включаются, что снижает динамические погрешности, обусловленные переходными процессами.

Использование изобретения позволяет создавать аналого-цифровые преобразователи, в которых величина кванта того же порядка, что и величина дрейфа порога срабатьшания компаратора.

I

Формула изобретения

Биполярный аналого-цифровой преобразователь, содержащий аналоговое запоминающее устройство, информационный вход которого является входной шиной, сумматор, первый и второй входы которого соединены соответственно с выходами первого и второго цифроаналоговык преобразователей, входы которых соединены с выходами соответствующих первого и второго регистров, установочные входы которых объединены, а информационные входы подключены к соответствующим выходам группы выходов распределителя тактовых импульсов, информационный вход которого соединен с выходом тактового генератора, а выход сумматора соединен с инвертирующим входом первого компаратора, отличаю- . щ и и с я тем, что, с целью повышения точности преобразователя, в него йведень второй компаратор, коммутатор, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, цифровой переключатель ; и триггер, первый вход КОТОРОГО объединен с установочными входами распределителя такте- вых импульсов аналогового запоминающего устройства и первого регистра и является шиной пуска, а выход подключен к входу тактового генератора, второй вход трихтера соединен с последним выходом распределителя

тактовых импульсов, выход аналогового запоминающего устройства соединен с неинвертирующим входом первого и инвертирующим входом второго компараторов, неинвертирующий вход последнего соединен с выходом сумматора, выходы первого и второго ком-- параторрв соединены с первым и вторым входами элемента ИСКЛЮЧАЮЩЕЕ ИЛИ выход которого подключен к первому входу коммутатора, второй вход которого соединен с выходом первого . компаратора, а третий вход - с выхоСоставитель В.Махнанов Редактор И.Шмакова ; Техред л.Сердюкова

Заказ 6769/57

Тираж 884

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская .наб,, д. 4/5

дом знакового разряда цифрового переключателя, остальные выходы которого являются информационной ВЫХОДНО

шиной, а первая и вторая группы информационных входов соединены соответственно с выходами первого и второго регистров, дополнительные входы которых соединены с первым и вторым управляющими входами цифрового переключателя, а первьш и второй входы записи регистров соединены соответственно с прямым и инверсным выходами коммутатора.

Корректор Э .Лончакова

Подписное

Авторы

Даты

1989-11-07—Публикация

1987-08-31—Подача