У1

(чЭ

Изобретение относится к электротехнике и может быть использовано в мостовых тиристорньгх преобразователях частоты

Целью изобретения является повьше- ние помехозащищенности и быстродействия устройства для управления тирис- торным преобразователем

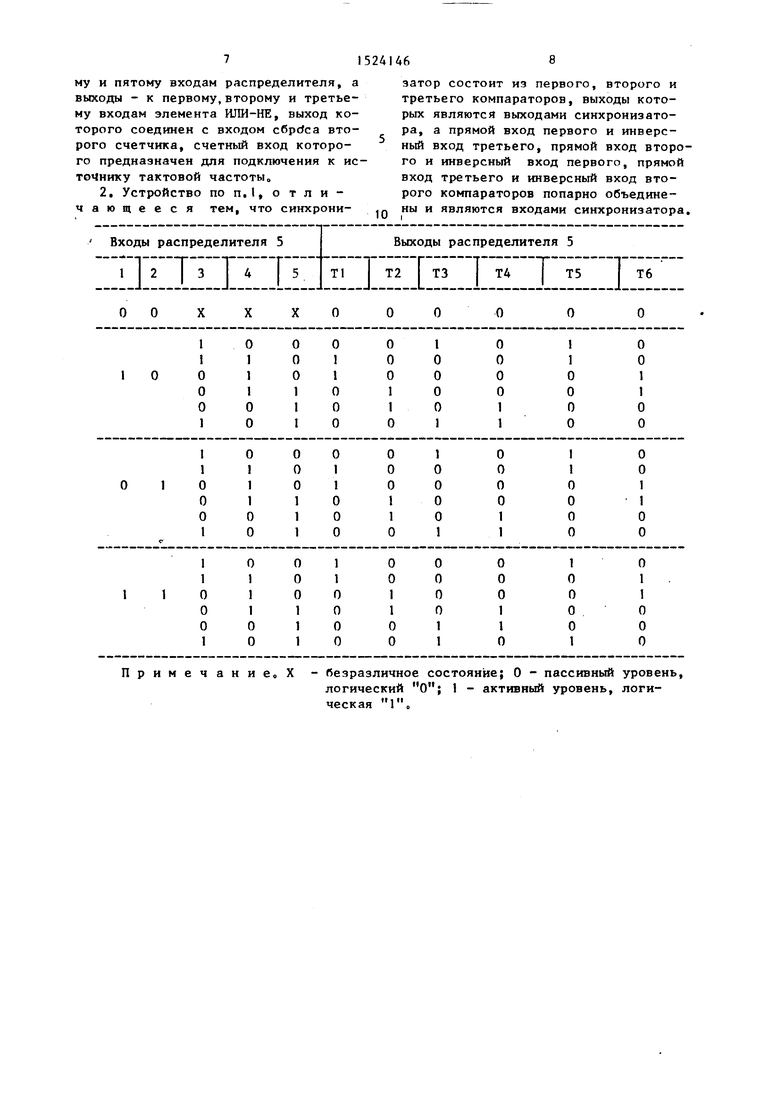

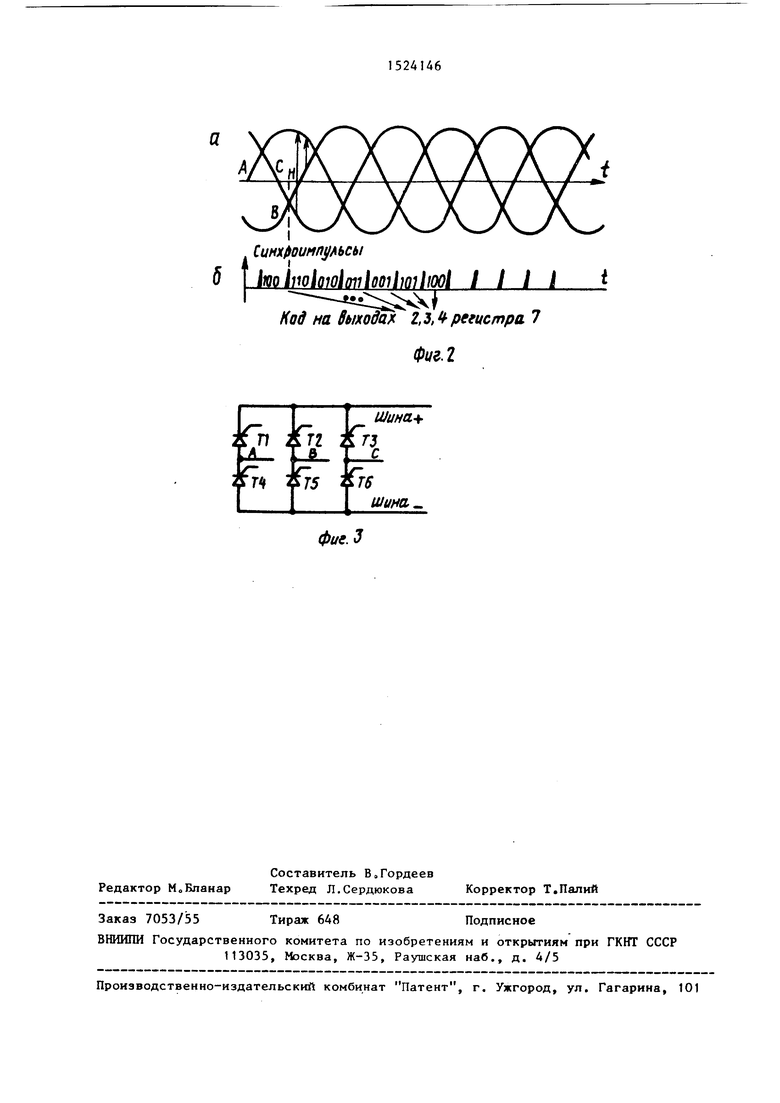

На фиг.1 приведена функциональная схема устройства для управления тиристорным преобразователем; на фиг с 2-диаграммы напряжений питакЛЦей сети, синхроимпульсов на выходе второго счетчика и соответствующие вре- менным отрезкам коды на выходах регистра; на фиг„ 3 - схема мостового тиристорного преобразователя,соответствующего приведенной таблице ис- .ткнности распределителяо

Устройство содержит первый 1,второй 2 и третий 3 компараторы, прямой вход первого 1 и инверсный вход третьего 3, прямой вход второго 2 и инверсный вход первого 1, а также прямой вход третьего 3 и инверсный вход второго 2 компараторов попарно объединены, и подключены к источнику сетевого напряжения, первый счетчик 4, младшие разряды установочных вхо- дов которого соединены с младшими разрядами входов кода управления, а старший - с общей шиной, счетный вход предназначен для подключения к источнику опорной fg частоты,выход соединен с первым входом распределителя 5, а вход установки - с выходом второго счетчика бис входом синхронизации регистра 7, первый вход которого подключен к старшему разряду входов кода управления, первый выход к второму входу распределителя 5,второй, третий и четвертый входы - к выходам первого 1, второго 2 и третьего 3 компараторов и к первым входам первого 8, второго 9 и третьего 10 элементов ИСКЛЮЧАЮПЩЕ ИЛИ соответственно, вторые входы которых соединены с вторым, третьим и четвертым выходами регистра 7 и с третьим, чет

вертым и пятым входами распределителя 5, а выходы - с первым, вторым и третьим входами элемента ИЛИ-НЕ 11, выход которого подключен к входу сброса второго счетчика 6, счетньй вход которого предназначен для подключения к источнику тактовой f частоты, а выходы распределителя 5 предназначены для управления электродами ти

Q

0

5

ристоров, синхронизатор 12 состоит из первого 1, второго 2 и третьего 3 компаратора с,

Устройство работает следующим образом

Напряжения А,В, и С сети попарно сравниваются между собой с помощью компараторов 1 - 3, выходные сигналы которых, с помощью элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 8-10 сравниваются с соответствующими им выходными сигналами регистра 7 В случае, если эти сигналы попарно равны, то на выходах всех элементов 8-10 установлены нули, выходной сигнал элемента ИЛИ-НЕ 11 равен 1 и второй счетчик 6 сброшен в О

В момент изменения соотношений между напряжениями .А,В,С, сигнал на выходе одного из компараторов 1,2, или 3 изменяется, на выходе элемента 11 устанавливается О, при котором счетчик начинает подсчет импульсов тактовой частоты f, В случае, если срабатьшание компаратора вызвано действием импульсной помехи, то с прекращением действия этой помехи счетчик 6 сбрасьгеается в О и схема возвращается в исходное состояние, а иначе, после заполнения счетчика 6, Тс,ео через время M/f , где М - объем счетчика, а f - величина тактовой частоты, превосходящее длительность импульсной помехи в сети (что достигается выбором М и ft) на его выходе устанавливается 1, При этом в счетчик Див регистр 7 переписывается содержимое их входов установки Сигналы на соответствующих входах и выходах регистра 7 становятся равными, на выходах элементов 8-10 устанавливаются О и счетчик 6 сбрасьюаетсЯо

Дпительность импульсов, формируемых при этом на выходе второго счетчика 6 (синхроимпульсов), определяется временем распространения сигнала через регистр 7, элементы 8 (9, 10) и 11 и счетчик 6, По моментам времени формирования синхроимпульсы совпадают с моментами времени,при которых фазы напряжений сети принимают значения 30, 90, 150, 210, 270 и 330 град, (фиг,2), т.е. совпадают с моментами нулевого уровня разностных фазовых напряжений сети,

В момент формирования синхроимпульса в младшие разряды счетчика 4

записывается содержимое соответствующих младших разрядов кода управления, а в старший - О. На выходе

счетчика 4, которым является выход его старшего разряда, устанавливается На первом выходе регистра 7 устанавливается значение, равное значению старшего разряда входов кода управления о

На выходе первого А счетчика устанавливается 1 после его заполнения, т.е. через промежуток времени, равный (P-N)/fp, где Р - объем счетчика 4, N - содержимое младших разря- величибР сети . - частота напряжения сетИ

дов кода управления, а f на опорной частоты, равная

где

сети

Сигналы, поступающие с выходов регистра 7 и с выхода первого счетчика 4, управляют работой распределителя 5 сигналов управления электродами тиристоров следующим образом

Пусть, например, сигнал синхронизации сформирован в момент перехода вы- ходных сигналов регистра 7 из состоя- НИИ 100 в состоянии ПО на его втором третьем и четвертом выходах соответственно (точка Н, фиг„2).

Если при этом на его первом выходе устанавливается что соответствует малым величинам действующих значений выходного напряжения тиристорно- го преобразователя, то до момента установки 1 на выходе счетчика 4 все выходные управляющие сигналы распределителя 5 - нули (пассивные), В момент установки 1 на выходе счетчика А, на соответствующих выходах распределителя 5 устанавливаются активные сигналы управления, при которых поджигаются тиристоры, соединяющие плюсовую выходную шину преобразователя с фазой А, а минусовую - с фазой В питающей сети.

Если на первом выходе регистра 7 установлена 1, что соответствует большим величинам действующих значений выходного напряжения преобразователя, то после установки кода управления плюсовая выходная шина преобразователя подключается к фазе А, а минусовая до момента установки на выходе счетчика 4 1 - к фазе В, а после установки - к фазе С питающей сети Коммутация осуществляется путем формирования на соответствующих выходах распределителя 5 активных сигналов.

152А146

При последующих переходах состояний на выходах регистра 7, на выходах Т1-Т6 распределителя 5 устанавливаются активные сигналы в соответ- ствии с логической функцией, показанной в таблице, соответствующей управлению тиристорным мостом (фиго3),где тиристоры Т1-Т6 соответствуют обозначениям управляющих выходов распределителя 5 (фиг о 1)о

10

5

0

0

5

5

0

5

0

5

Распределитель 5 представляет собой устройство с жесткой логикой,со- ответсвующей приведенной в таблице. Это устройство может быть вьтолнено как на дискретных элементах, например логических элементах, так и на интегральных схемах, например на одной микросхеме с соответствующей расшивкой.

Формула изобретения

I, Устрюйство для управления тиристорным преобразователем, включающее синхронизатор, распределитель,первый и второй счетчики, причем входы синхронизатора подключены к источнику сетевого напряжения, младшие разряды установочных входов первого счетчика соединены с младшими разрядами входов кода управления, а счетный вход подключен к источнику опорной частоты, вькод первого счетчика соединен с входом распределителя, выходы которого предназначены для подключения к управляющим входам тиристоров, о т - личающеес я тем, что, с целью повьш1ения помехозащищенности и быстродействия, в него введены регистр, первый, второй и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ и трехвхОдовой элемент ШТИ-НЕ, причем старший разряд установочного входа счетчика подключен к общей шине, вход установки - к выходу второго счетчика и входу синхронизации регистра, первый вход которого соединен со старшим разрядом входов кода управления, первый выход регистра соединен с вторым входом распределителя, а второй, третий и четвертый входы соответственно соединены с выходами синхронизатора и первыми входами первого, второго и третьего элементов ИСКЛЮЧАЮ1ЧЕЕ 1ШИ, вторые входы которых подключены к второму, третьему и четвертому выходам регистра и к третьему, четвертому и пятому входам распределителя, а выходы - к первому, второму и третьему входам элемента ИЛИ-НЕ, выход которого соединен с входом c6pdca второго счетчика, счетный вход которого предназначен для подключения к источнику тактовой частоты

2, Устройство по п.I, о т л и - чающееся тем, что синхрони

затор состоит из первого, второго и третьего компараторов, выходы которых являются выходами синхронизатора, а прямой вход первого и инверс- ньй вход третьего, прямой вход второго и инверсный вход первого, прямой вход третьего и инверсный вход второго компараторов попарно объединены и являются входами синхронизатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления трехфазным тиристорным регулятором мощности | 1988 |

|

SU1667035A1 |

| Устройство для управления @ -фазным вентильным преобразователем | 1989 |

|

SU1721756A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

| Устройство импульсного регулирования мощности переменного тока | 1983 |

|

SU1100693A1 |

| Устройство для автоматического переключения однофазных нагрузок в низковольтных распределительных сетях | 1981 |

|

SU1026234A1 |

| Устройство для пуска асинхронного электродвигателя | 1984 |

|

SU1274099A1 |

| Многоканальное дискретное фазосдвигающее устройство | 1980 |

|

SU955413A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1261116A1 |

| Дискретно-цифровой электропривод | 1985 |

|

SU1350800A1 |

| Устройство импульсного регулирования мощности в @ -фазной сети без нейтрали | 1985 |

|

SU1272327A1 |

Изобретение относится к электротехнике и может быть использовано в мостовых тиристорных преобразователях частоты. Целью изобретения является повышение помехозащищенности и быстродействия. Устройство содержит первый 1, второй 2 и третий 3 компараторы, первый счетчик 4, распределитель 5, второй счетчик 6, регистр 7, первый 8, второй 9 и третий элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, элемень ИЛИ-НЕ 11 и синхронизатор 12. Устройство обеспечивает малую временную задержку при кодах управления, соответствующих малым углам поджига тиристоров. 1 з.п. ф-лы, 3 ил, 1 табл.

О О

О

Примечание, X

безразличное состояние; О - пассивный уровень, логический 1 - активный уровень, логическая 1.

О

О

О

а

1 hoMaioloiilooiljoil OOl I I I I -- С::;: чГ

Код на Вшода)( ts.ff регистра 7

Фиг. 2

sn &n srj

:Гг АГ5 Г5

фие. 3

ШинаШина

| Устройство для управления мостовымпРЕОбРАзОВАТЕлЕМ | 1979 |

|

SU836754A1 |

| Устройство для управления тиристорным преобразователем | 1985 |

|

SU1343516A1 |

Авторы

Даты

1989-11-23—Публикация

1988-03-10—Подача