Изобретение относится к вычислительной технике и автоматике и предназначено для выполнения операции преобразования параллельного двоичного кода (слова) в последовательный код сообщения с программируемой длительностью паузы начала преобразования после запуска преобразователя и программируемым форматом преобразования, а также для формирования синхроимпульсов сопровождения сообщения, трех битов состояния (пуска, режима преобразования и окончания преобразования) и контрольного бита четности с обеспечением программной возможности вставки его в конец сообщения и может быть использовано при построении контроллеров локальной сети (КЛС), например КЛС на основе ГОСТ 18977-79 и РТМ 1495-75 по протоколам, являющимся правилами обмена информацией между станциями локальной сети (СЛС) по мультиплексной и/или раздельным линиям связи сообщениями (последовательными кодами разрядности 12 или 24 или 32 бит младшими разрядами вперед и старшим битом контроля четности), разделенными между собой, как правило, паузами длительностью от четырех до сорока периодов Т частоты следования тактовых импульсов преобразования и т.п. [1].

В минимальной конфигурации в составе СЛС можно выделить (см., например, в [1] на с. 221 рис.5.9) КЛС, образованный преобразователем параллельного кода в последовательный (блоком слова/сообщения), преобразователем последовательного кода в параллельный (блоком бита/слова), кодером, декодером, аналоговым приемопередатчиком и устройством управления (УУ) и синхронизации (блоком связи с подсистемой), для взаимосинхронизации и управления КЛС в целом, электронную вычислительную машину (ЭВМ) содержит процессор (однокристальную ЭВМ) и память, в общем случае содержащую постоянное (ПЗУ), оперативное (ОЗУ) и двухпортовое оперативное запоминающее устройство (ДОЗУ) и системную магистраль (СМ) для связи с внешними устройствами ввода-вывода данных и управления КЛС в процессе информационного взаимодействия между ЭВМ и составными частями КЛС с помощью УУ.

Легко видеть, что для рационального распределения в СЛС функций между аппаратно-программными средствами преобразователь параллельного кода в последовательный (как составная часть КЛС, входящего в СЛС) должен с помощью УУ гибко управляться от ЭВМ и быть максимально инвариантным как к типу СМ и способам обмена информацией между ЭВМ и КЛС, так и к протоколам локальной сети.

Следует заметить, что в настоящее время непосредственно сама операция преобразования параллельного двоичного кода в последовательный технически реализуется тривиально, в частности, с помощью простого регистра с параллельным асинхронным вводом и последовательным синхронизирующим выводом (например, на микросхеме типа 533 ИР9 для формирования однобайтового сообщения) или с помощью универсального регистра с синхронизирующими как параллельным вводом-выводом, так и последовательным выводом-вводом (например, на микросхеме типа 1533 ИР24 для формирования сообщения однобайтовыми фрагментами с помощью входного буферного регистра - см. в [2] на с. 104 рис. 2.26).

Однако в СЛС каждой операции формирования сообщения предшествует процедура инициализации УУ и загрузки преобразователя параллельного кода в последовательный, запуск этого преобразователя, отработка им паузы или по протоколу, или для устранения асинхронности во времени между запуском и тактовыми импульсами преобразования, и только затем выполняется сама операции преобразования, после выполнения которой, как правило, необходима выдача прерывания ЭВМ об окончании преобразования.

В этой связи создание простого преобразователя параллельного кода в последовательный с требуемыми функциональными возможностями, обеспечивающими гибкую управляемость от ЭВМ при максимальной независимости как от типа СМ и способов обмена информацией между ЭВМ и составными частями КЛС, так и протоколов локальной сети, представляет, на наш взгляд, актуальную техническую задачу, разрешение которой позволит повысить качество вновь разрабатываемых КЛС, поддерживающих в локальных сетях обмен отдельными сообщениями (словами) при минимальных аппаратурных затратах.

Основным недостатком известных преобразователей [3]-[7] является ограниченность их функциональных возможностей (например, отсутствие в них возможности как программирования длительности паузы начала преобразования после запуска и формата преобразования, так и формирования контрольного бита с программированием возможности вставки его в конец сообщения), что обусловлено созданием их с акцентом на выполнение лишь основной функции (соответствующей модификации операции преобразования параллельного кода в последовательный код) при слабой управляемости каждого из них от ЭВМ.

Известен преобразователь [5], содержащий регистр, распределитель импульсов, два элемента ИЛИ, группу элементов И, триггер выдачи, триггер подготовки, информационные входы, тактовый вход, информационный выход, тактовый выход и выход запроса информации.

В исходном состоянии триггер выдачи сброшен, триггер подготовки установлен, распределитель импульсов активизирован для выдачи на информационный выход младшего бита регистра, а на выходе запроса выставлен сигнал, снимаемый с инверсного выхода триггера выдачи и означающий, что преобразователь готов к запуску для выполнения очередной операции преобразования.

Запуск преобразователя [5] осуществляется загрузкой в регистр кода, поступающего на информационные входы в виде импульсов, совпадающих на временной оси с одним из импульсов на тактовом входе преобразователя, причем на первый (младший) информационный вход при запуске всегда поступает маркерный (единичный) импульс, непосредственно сбрасывающий триггер подготовки и спадом запускающий преобразователь установкой триггера выдачи.

Установленный триггер выдачи разрешает прохождение входных тактовых импульсов через первый элемент И группы на входы опроса остальных элементов И группы и синхровход распределителя импульсов, переключающегося в следующее состояние по спаду каждого импульса, действующего на его синхровходе. Таким образом, в процессе выполнения операции распределитель импульсов последовательно подключает выходы регистра на информационный выход преобразователя через соответствующие элементы И группы и первый элемент ИЛИ, а по спаду сигнала с выхода старшего разряда распределителя триггер выдачи сбрасывается, а триггер подготовки устанавливается. На этом выполнение операции преобразования заканчивается, а очередной запуск преобразователя начнется по окончании следующего маркерного импульса.

Основным недостатком преобразователя [5] является ограниченность его функциональных возможностей (например, отсутствие возможности программирования формата преобразования), обусловленная, в частности, специализированным как вводом, так и выводом, поскольку как при вводе, так и при выводе присутствует маркерный бит. В этой связи преобразователь [5] имеет ограниченную область применения и может быть использован при построении контроллеров асинхронных последовательных интерфейсов типа RS-232C.

Известен преобразователь [6], содержащий группу регистров, соединенных между собою так, что последовательный выход предыдущего регистра соединен с последовательным входом последующего регистра, причем параллельные входы регистров объединены между собой и соединены с информационным кодовым входом преобразователя, тактовый вход которого соединен с синхровходами всех регистров, элементы И, элемент ИЛИ, выход которого является выходом последовательного кода сообщения преобразователя, а входы элемента ИЛИ соединены с выходами элементов И, вход обнуления, триггеры адреса вывода, входы сброса которых соединены с входом обнуления преобразователя, дешифратор и вход адреса, соединенный с информационным входом дешифратора, первая группа стробированных выходов дешифратора соединена с входами записи всех регистров соответственно, а вторая группа стробированных выходов (в описании преобразователя [6] раздельное стробирование групп выходов дешифратора не отражено, поскольку описание составлено с помощью простой функциональной схемы, а не с помощью электрической функциональной схемы) соединена с входами установки триггеров адреса вывода, выходы которых соединены с первыми входами элементов И, вторые входы которых соединены с последовательными выходами всех регистров, а третьи входы элементов И объединены между собой и соединены с тактовым входом преобразователя.

Перед началом преобразования массив информации (например, кадр, образованный соответствующей совокупностью двоичных слов) адресно записывается в регистры и адресно устанавливается только один из триггеров адреса вывода. После этого на тактовый вход преобразователя подается последовательность импульсов, число которых равно числу бит сообщения, формируемого на выходе элемента ИЛИ. Таким образом, преобразователь может начинать преобразование записанного массива информации с любого слова (регистра) массива.

Основным недостатком преобразователя [6] при использовании его, например, для построения КЛС является избыточность оборудования (триггеров адреса, элементов И и элемента ИЛИ), которая оказывается неиспользованной при формировании сообщения программно в виде как одного двоичного слова, так и массива слов. Этот недостаток обусловлен адресной программной организацией начала вывода информации из преобразователя, которую трудно, на наш взгляд, эффективно использовать при построении устройств с программным (а не жестким) управлением, так как перед каждым преобразованием в регистры преобразователя слова массива программно можно загрузить в любом порядке.

Из известных технических решений наиболее близким к предлагаемому является преобразователь [7], содержащий счетчик, сдвигатель, образованный дешифратором, коммутатором и первым регистром сдвига, дешифратор нуля, второй регистр сдвига, два генератора импульсов, информационный кодовый вход (входная шина данных), выход, являющийся выходом коммутатора сдвигателя, первый управляющий выход, являющийся инверсным выходом дешифратора нуля, второй управляющий выход, являющийся инверсным выходом переполнения на вычитание счетчика, и вход установки (запуска).

В исходном состоянии счетчик и второй регистр сброшены и работа обоих генераторов импульсов запрещена. Перед запуском на информационном кодовом входе установлен код, который по импульсу запуска загружается одновременно в оба регистра. При наличии информации во втором регистре (т.е. его содержимое не равно нулю) на инверсном (первом) выходе дешифратора нуля вырабатывается единичный сигнал, запрещающий работу дешифратора сдвигателя и первого генератора, а на прямом выходе дешифратора нуля вырабатывается нулевой сигнал, разрешающий работу второго генератора импульсов, по импульсам которого содержимое счетчика увеличивается, а второго регистра сдвигается до нуля. В момент обнуления второго регистра содержимое счетчика определяет номер самого старшего единичного бита в исходном преобразуемом коде (содержится в первом регистре) и сигнал на инвертирующем (или прямом) выходе дешифратора нуля переключается из "1 в 0" (или из "0 в 1"). Это запрещает работу второго генератора и разрешает работу дешифратора и первого генератора, по каждому импульсу которого содержимое счетчика уменьшается на единицу, а содержимое первого регистра сдвигается на бит. Процесс преобразования продолжается до момента обнуления содержимого счетчика, который отмечается переключением сигнала на втором управляющем выходе преобразователя с "1 на 0". Следовательно, сам процесс преобразования начинается по спаду сигнала на первом выходе преобразователя, а заканчивается по спаду сигнала на втором управляющем выходе преобразователя.

Таким образом, в каждом цикле функционирования преобразователя после его запуска можно выделить два периода:

период Т1 формирования в счетчике кода номера самого старшего единичного бита в преобразуемом коде, содержащемся в первом регистре;

период Т2 выполнения собственно операции преобразования. Легко видеть, что при равенстве частот функционирования обоих генераторов импульсов

T1=T2=N•T,

где Т - период частоты следования импульсов первого (или второго) генератора;

N - номер старшего единичного бита в исходном коде, сдвигаемом в периоде Tl во втором регистре младшими разрядами вперед;

• - знак операции умножения.

Основным недостатком преобразователя [7] является его сложность (наличие в нем двух регистров с параллельным вводом-выводом и последовательным сдвигом, двух управляемых генераторов импульсов и сложного сдвигателя) и ограниченность области его применения, что обусловлено низким уровнем его программной управляемости, в том числе аппаратным специфическим выполнением в нем преобразования за два периода с зависимостью длительности выполнения операции от положения старшего единичного бита в исходном преобразуемом коде.

Предлагаемым изобретением решается задача расширения области использования преобразователя и сокращение его аппаратурных затрат повышением уровня его программной управляемости за счет обеспечения программирования формата преобразования и длительности паузы после запуска и формирования трех битов состояния (пуска, режима преобразования, окончания преобразования) и контрольного бита четности с программным обеспечением возможности вставки его в конец сообщения.

Для достижения этого технического результата в преобразователь параллельного кода в последовательный, содержащий счетчик, сдвигатель, вход запуска, выход последовательного кода сообщения, являющийся выходом сдвигателя, выход синхроимпульсов сопровождения сообщения и n-разрядный информационный кодовый вход, являющийся информационным кодовым входом сдвигателя, введены три элемента И-НЕ, триггер пуска, компаратор, элемент ИЛИ-НЕ, шесть элементов И, k=n/8 входов импульсов записи, соединенных с входами импульсов записи сдвигателя и входами первого элемента И, выход которого соединен с входом сброса триггера пуска и первым входом второго элемента И, тактовый вход, соединенный с первыми входами первого и второго элементов И-НЕ и третьего элемента И, выход бита пуска, соединенный с прямым выходом триггера пуска, вторым входом первого элемента И-НЕ и первыми входами элемента ИЛИ-НЕ и четвертого элемента И, m-разрядный (где 2 в степени m не меньше, чем n), программный кодовый вход формата преобразования, соединенный с первым информационным кодовым входом компаратора, выход которого соединен с первыми входами третьего элемента И-НЕ и пятого элемента И, программный битовый вход разрешения вставки контрольного бита в конец сообщения, соединенный с первым входом шестого элемента И, выход бита режима преобразования, соединенный с выходом четвертого элемента И и вторыми входами третьего и пятого элементов И, и выход бита окончания преобразования, являющийся выходом элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего И-НЕ и третьим входом первого элемента И-НЕ, выход которого соединен со счетным входом счетчика, причем выход третьего элемента И соединен с синхровходом сдвигателя и выходом синхроимпульсов сопровождения сообщения преобразователя, информационные выходы m младших разрядов счетчика соединены с вторым информационным кодовым входом компаратора, вход запуска преобразователя соединен с входами установки сдвигателя и триггера пуска и вторым входом второго элемента И, выход которого соединен с входом записи счетчика, информационный выход старшего разряда которого соединен с вторыми входами третьего элемента И-НЕ и четвертого элемента И, входы q (q не меньше m) младших разрядов информационного кодового входа преобразователя соединены с информационными входами младших разрядов счетчика, информационный вход старшего разряда которого соединен с шиной логического нуля (корпусом) преобразователя и информационным входом триггера пуска, синхровход которого соединен с выходом второго элемента И-НЕ, второй вход которого соединен с выходом пятого элемента И и вторым входом шестого элемента И, выход которого соединен с управляющим входом сдвигателя, который содержит два элемента ИЛИ, k байтовых регистров с асинхронным параллельным вводом и синхронизирующим последовательным выводом кодов младшими разрядами вперед, два элемента НЕ, седьмой и восьмой элементы И, и триггер контрольного бита, вход установки которого является входом установки сдвигателя, входы n-разрядного информационного кодового входа которого соединены с информационными параллельными входами регистров сдвигателя так, что первый регистр является младшим, а k-й регистр старшим, последовательный выход которого через все предыдущие регистры связан с последовательным входом первого регистра, прямой последовательный выход которого соединен с последовательным входом k-го регистра и первым входом седьмого элемента И, выход которого соединен с первым входом первого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, а выход первого элемента ИЛИ является выходом сдвигателя, k входов импульсов записи которого соответственно соединены с асинхронными входами записи регистров с первого по k-й, синхровход сдвигателя связан через первый элемент НЕ с синхровходами всех регистров и первым входом второго элемента ИЛИ, второй вход которого соединен с инверсным последовательным выходом первого регистра, а выход соединен с синхровходом триггера контрольного бита, вход сброса которого соединен с шиной логической "1" преобразователя, управляющий вход сдвигателя соединен с первым входом восьмого элемента И и связан через второй элемент НЕ с вторым входом седьмого элемента И, второй вход восьмого элемента И соединен с прямым выходом триггера контрольного бита, инверсный выход которого соединен с его информационным входом, а инверсные входы разрешения сдвига всех регистров соединены с шиной логического нуля преобразователя.

Авторам неизвестны технические решения, содержащие признаки, эквивалентные отличительным признакам (введение трех элементов И-НЕ, триггера пуска, компаратора, элемента ИЛИ-НЕ, шести элементов И, программного кодового входа формата преобразования, программного битового входа разрешения вставки контрольного бита в конец сообщения, входов импульсов записи, тактового входа и битовых выходов пуска, режима преобразования и окончания преобразования) предлагаемого преобразователя, которые расширяют область его использования при значительно меньших аппаратурных затратах по сравнению с прототипом [7].

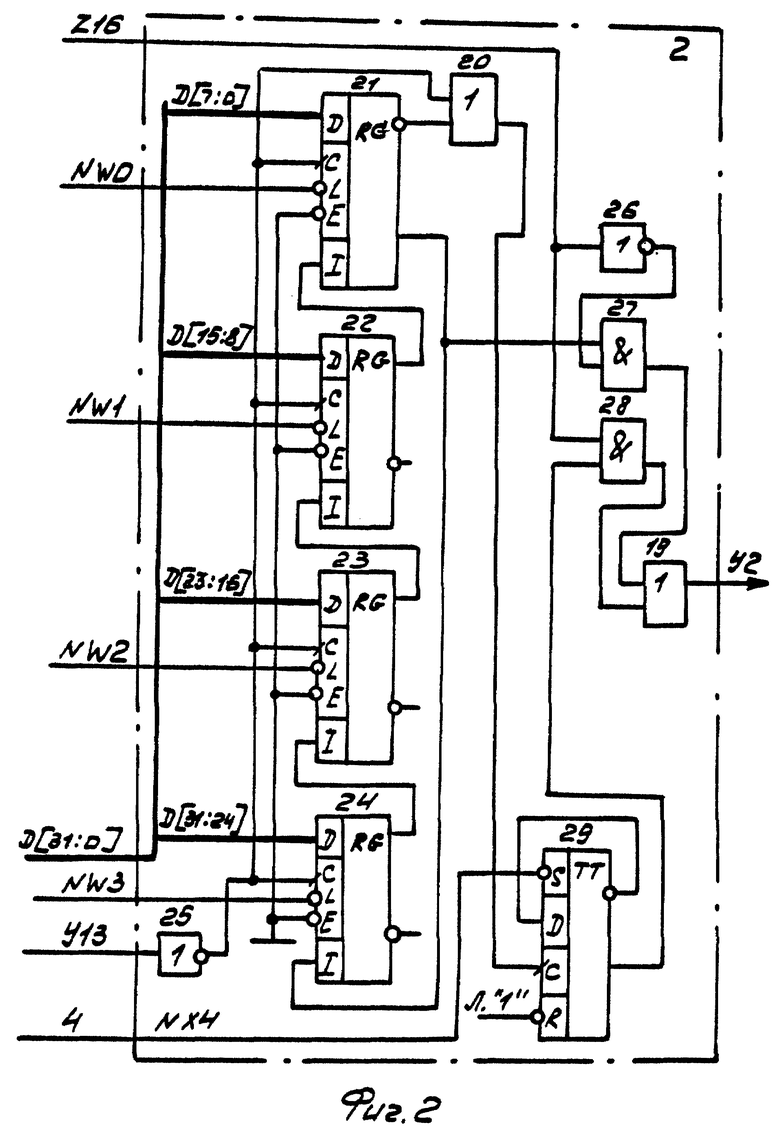

На фиг. 1 приведена реализация предлагаемого преобразователя на уровне электрической функциональной схемы в библиотеке элементов серии 533 для n= 32, q=6, m=5 и k=4.

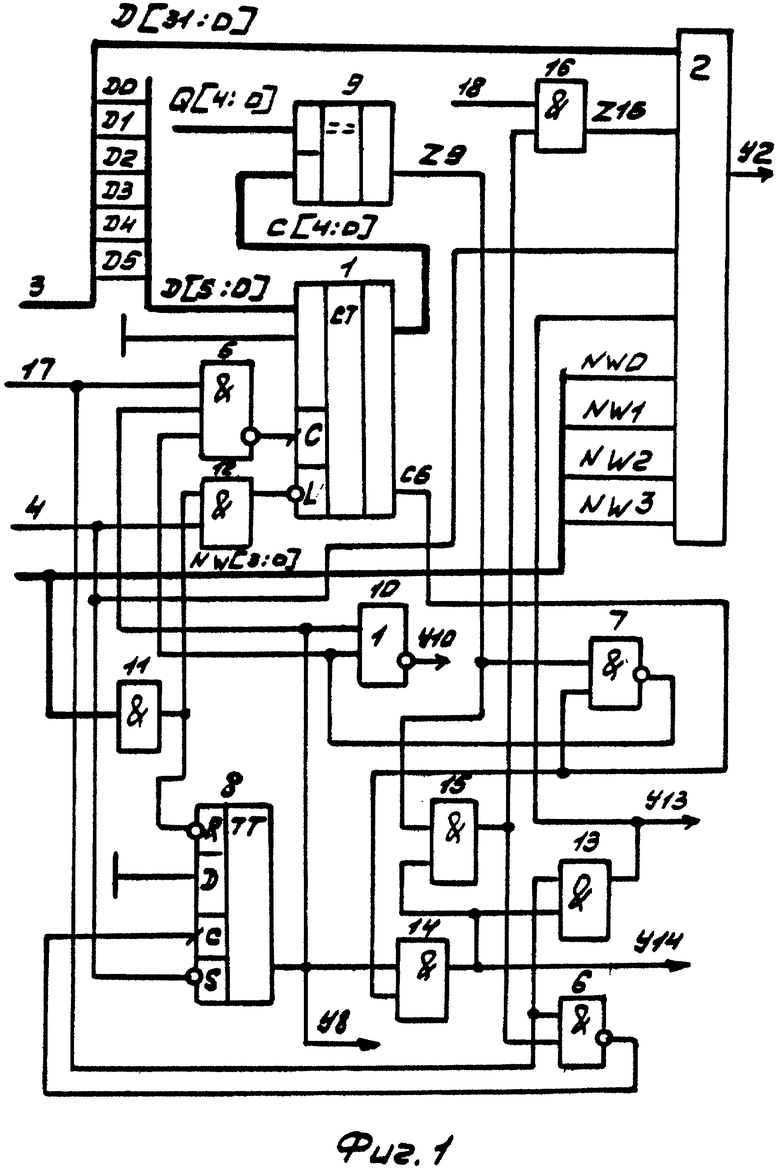

На фиг.2 представлена электрическая функциональная схема сдвигателя.

Преобразователь параллельного кода в последовательный (фиг.1) содержит счетчик 1, сдвигатель 2, n=32-разрядный информационный кодовый вход 3, являющийся информационным кодовым входом сдвигателя 2, входы младших q=6 разрядов которого соединены с информационными входами младших разрядов счетчика 1, вход 4 запуска, три элемента И-НЕ 5, 6 и 7, триггер 8 пуска, компаратор 9, элемент 10 ИЛИ-НЕ, шесть элементов И 11-16, k=n/8=4 входов импульсов записи, соединенных с входами импульсов записи сдвигателя 2 и входами первого 11 элемента И, выход которого соединен с входом сброса триггера 8 пуска и первым входом второго 12 элемента И, тактовый вход 17, соединенный с первыми входами первого 5 и второго 6 элементов И-НЕ и третьего 13 элемента И, выход бита пуска, соединенный с прямым выходом триггера 8 пуска, вторым входом первого 5 элемента И-НЕ и первыми входами элемента 10 ИЛИ-НЕ и четвертого 14 элемента И, m=5-разрядный программный кодовый вход формата преобразования, являющийся первым информационным кодовым входом компаратора 9, выход которого соединен с первыми входами третьего 7 элемента И-НЕ и пятого 15 элемента И, программный битовый вход 18 разрешения вставки контрольного бита в конец сообщения, соединенный с первым входом шестого 16 элемента И, выход синхроимпульсов сопровождения сообщения, являющийся выходом третьего 13 элемента И, который соединен с синхровходом сдвигателя 2, выход бита окончания преобразования, являющийся выходом элемента 10 ИЛИ-НЕ, второй вход которого соединен с выходом третьего 7 элемента И-НЕ и третьим входом первого 5 элемента И-НЕ, выход которого соединен со счетным входом счетчика 1, выходы m=5 младших разрядов которого соединены с вторым информационным кодовым входом компаратора 9, выход бита режима преобразования, соединенный с выходом четвертого 14 элемента И и вторыми входами третьего 13 и пятого 15 элементов И, причем вход 4 запуска соединен с установочными входами сдвигателя 2 и триггера 8 пуска и вторым входом второго 12 элемента И, выход которого соединен с входом записи счетчика 1, информационный выход старшего разряда которого соединен с вторыми входами третьего 7 элемента И-НЕ и четвертого 14 элемента И, шина логического нуля (корпуса) преобразователя соединена с информационным входом старшего разряда счетчика 1 и информационным входом триггера 8 пуска, синхровход которого соединен с выходом второго 6 элемента И-НЕ, второй вход которого соединен с выходом пятого 15 элемента И и вторым входом шестого 16 элемента И, выход которого соединен с управляющим входом сдвигателя 2, который содержит (фиг.2) два элемента ИЛИ 19 и 20, k=4 байтовых регистра 21, 22, 23 и 24 с асинхронным параллельным вводом и синхронизирующим последовательным выводом кодов младшими разрядами вперед, два элемента НЕ 25 и 26, седьмой 27 и восьмой 28 элементы И и триггер 29 контрольного бита, вход установки которого является входом установки сдвигателя 2, входы n= 32-разрядного информационного кодового входа которого соединены с информационными параллельными входами регистров 21-24 сдвигателя 2 так, что первый 21 регистр является младшим, а k=4-ый регистр 24 старшим, последовательный выход которого через предыдущие регистры 23 и 22 связан с последовательным входом первого 21 регистра, прямой последовательный выход которого соединен с последовательным входом k=4-гo 24 регистра и первым входом седьмого 27 элемента И, выход которого соединен с входом первого 19 элемента ИЛИ, второй вход которого соединен с выходом восьмого 28 элемента И, а выход соединен с выходом сдвигателя 2, k=4 входов импульсов записи которого соответственно соединены с асинхронными входами записи регистров с первого 21 по k= 4-ый 24, синхровход сдвигателя 2 через первый 25 элемент НЕ связан с синхровходами регистров 21-24 и первым входом второго 20 элемента ИЛИ, второй вход которого соединен с инверсным последовательным выходом первого 21 регистра, а выход соединен с синхровходом триггера 29 контрольного бита, вход сброса которого соединен с шиной логической "1" преобразователя, управляющий вход сдвигателя 2 соединен с первым входом восьмого 28 элемента И и связан через второй 26 элемент НЕ с вторым входом седьмого 27 элемента И, второй вход восьмого 28 элемента И соединен с прямым выходом триггера 29 контрольного бита, инверсный выход которого соединен с его информационным входом, а инверсные входы разрешения сдвига регистров 21-24 соединены с шиной логического нуля преобразователя.

Преобразователь (фиг.1 и 2) реализован на интегральных микросхемах (ИС) серии 533 так, что счетчик 1 выполнен на двух ИС 533ИЕ7, компаратор 9 - на двух ИС 533 (СП1 и ЛП5), триггеры 10 и 29 - на одной ИС 533ТМ2, каждый из регистров 21-24 - на одной ИС 533ИР9, а логические элементы на шести следующих ИС 533: ЛА2, ЛН1, двух ЛИ2, ЛИ6 и ЛЛ1.

Описание функционирования преобразователя ведется далее с помощью системы положений и обозначений, определенных в следующих пунктах.

1. Используется модифицированный язык описания Булевых (логических) функций - ABEL, в котором операторы И (конъюнкции), ИЛИ (дизъюнкции) и НЕ (инверсии) имеют соответственно обозначения "&", "#" и "!", например, Y=!Х1# ! Х2 логическая функция аргументов X1 и Х2 вырабатывается так, что сначала аргументы инвертируются, а затем над ними выполняется операция ИЛИ (#).

Исходные инверсные переменные обозначим с помощью буквы N, например, NX4 означает исходный инверсный аргумент, т.е. NX4=!X4.

2. Коды на информационном 3 и программном кодовых входах преобразователя обозначим соответственно через D[31:0]=D31D30...D0 и Q[4:0]=Q4Q3Q2Q1Q0, а формируемый счетчиком 1 код - через С[6:0]=С6С5С4С3С2С1С0, где нулевые (D0, Q0, С0) младшие, a (D31, Q4, С6) старшие разрядные цифры (0 или 1) этих кодов. В зависимости от разрядности (например, р=8 или р=16 или р=32) шины данных системной магистрали (СМ) СЛС входы регистров 21-24 при р=32 раздельны, при р=16 объединены попарно байтами (т.е. D[7:0]=D[23:16] и D[15:8]= D[31:24]), а при р=8 байтовые входы всех регистров объединены поразрядно, т. е. D[7:0]=D[15:8]=D[23:16]=D[31:24].

3. Как инверсные переменные импульсы записи на входах преобразователя обозначены через NW3, NW2, NW1, NW0 в качестве компонент входного вектора (кода) NW[3: 0]=NW3 NW2 NW1 NW0 записи. В зависимости от параметра "р" (см. п. 1) импульсы записи могут формироваться УУ КЛС или раздельно и последовательно во времени независимо от значения "р", либо одновременно попарно (сначала NW0= NW1, а затем NW2= NW3 - при р=16 или 32), либо все одновременно (т.е. NW0=NW1= NW2=NW3) только при р=32. В этой связи предлагаемый преобразователь оказывается практически независим от типа СМ СЛС.

4. Поступающие на входы 4, 17 и 18 инверсные импульсы запуска, тактовые импульсы и программный битовый сигнал разрешения вставки контрольного бита в конец сообщения обозначим соответственно через NX4, Х17 и X18 как логические переменные.

5. Формируемые на выходах соответствующих составных частей преобразователя битовые сигналы как логические переменные обозначим с помощью буквы Y для выходных сигналов преобразователя (т.е. Y2, Y8, Y10, Y13, Y14) и буквы Z для внутренних сигналов, где после буквы Y (или Z) стоит номер составной части преобразователя, например, Y8 (или Z9) - сигнал, формируемый триггером 8 пуска (или компаратором 9).

6. Компаратор 9 непрерывно сравнивает коды Q[4:0]=Q4Q3Q2Q1Q0 и С[4:0]= С4С3С2С1С0 и формирует переменную Z9 согласно выражениям

Z9=0 при Q[4:0] не равном С[4:0], (1)

Z9=1 при Q[4:0]=C[4:0] (2)

7. Под фронтом или спадом любого сигнала (прямого или инверсного) понимается смена логического значения этого сигнала из "0 в 1" или из "1 в 0" соответственно.

8. Под установкой (или сбросом), например, триггера 8 понимается переключение этого триггера в "1" (или в "0").

9. Выходной последовательный код Y2 сообщения, выходной синхросигнал Y13 сопровождения сообщения и выходные битовые переменные Y10 окончания преобразования, Y14 режима преобразования, Y8 пуска (Y8 формирует триггер 8) вырабатываются в преобразователе (фиг.1, фиг.2) так

Y2=Z21&[!(X18&Y14&Z9)]#Z29&(X18&Y14&Z9), (3)

Y13=X17&Y14, (4)

Y10=(!Y8)&(C6&Z9), (5)

Y14=Y8&C6, (6)

что определяют четыре следующих режима (состояния) его функционирования как конечного последовательностного автомата:

Р0 подготовки (ожидания) при Y14Y10Y8=000, (7)

Р1 отработки паузы при Y14Y10Y8=001, (8)

Р2 преобразования при Y14Y10Y8 =101, (9)

Р3 окончания преобразования при Y14Y10Y0=010 (10)

С учетом изложенного выше (1)-(10) функционирование преобразователя в целом заключается в последовательном чередовании его режимов (состояний) Р0, P1, P2, Р3, Р0,..., Р3, Р0 и т.д. так, что переход в исходное состояние Р0 (7) может быть осуществлен из любого режима Р1(8), Р2(9), Р3(10) по инверсным импульсам

Z11=NW0&NW1&NW2&NW3, (11)

Z12=Z11&NX4, (12)

формируемым по инверсным импульсам вектора записи

NW[3:0]=NW3 NW2 NW1 NW0.

Непосредственно по Z12=0 в счетчик 1 загружается код "0D5D4D3D2D1D0" и он формирует нулевой сигнал С6=0, а по Z11=0 сбрасывается триггер 8 пуска, но переход в P1, P2 и Р3 осуществляется только из режимов Р0 (по NX4=0), P1 (по изменению содержимого счетчика 1 из "0111111" в "1000000") и P2 (по окончании инверсного импульса Z6=!(X17&Y14&Z9)) соответственно. В состоянии Р0 возможно изменение программного бита X18 и программного кода Q[4:0], определяющего формат преобразования - количество К импульсов Y13 в режиме Р2 преобразования длительностью ТР2-, согласно выражениям

К=1+Q0+2•Q1+4•Q2+8•Q3+16•Q4, - (13)

TP2=K•T, - (14)

где • - здесь и далее оператор операции умножения;

Qi - разрядная цифра (0 или 1) разряда i=0, 1, 2, 3, 4 кода Q[4:0];

Т - длительность периода частоты следования тактовых импульсов X17.

Далее, в зависимости от величины К (13) и параметра "р" (см. выше п.1 и 2) в регистры 21-24 сдвигателя с информационного кодового входа D[31:0] загружается код G[(K-1):0] (где G0=Z21) по одному или нескольким импульсам вектора записи NW[3:0] (например, соответствующим командам адресной записи ЭВМ), а затем по импульсу NX4 (по одной из команд адресной записи ЭВМ) преобразователь запускается установкой триггеров 8 и 29 и записью в счетчик 1 по импульсу Z12=NX4 кода C[6:0]=0D5D4D3D2D1D0, где код С[5:0]= D[5:0] определяется младшими разрядами кода D[31:0] на информационных входах младших разрядов счетчика 1, который в момент действия импульса NX4 определяет длительность ТР1 паузы (режима Р1) согласно выражению

ТР1=Т•[64-(С0+2•С1+4•С2+8•С3+16•С4+32•С5)], (15)

где Ci=Di - разрядная цифра (0 или 1) разряда i=0, 1,..., 5 счетчика 1 в момент действия импульса NX4=0.

После запуска в процессе функционирования преобразователя элемент 5 формирует инверсные счетные импульсы так

Z5=!(X17&Y8&Z7), (17)

что в режиме Р1 (8) по фронту каждого из импульсов Z5 содержимое счетчика 1 увеличивается на "1", и при изменении содержимого счетчика 1 из (0111111) в (1000000) начинается режим Р2 (9), в котором счетчик 1 продолжает (при Z7= 1) считать фронты импульсов Z5 (17), и формируются синхроимпульсы Y13 (4) сопровождения сообщения Y2 (3), импульсы Z25=!Y13 циклического сдвига содержимого регистров 21-24 по фронтам, инверсные импульсы Z20= Z25# !(Z21), по фронтам которых триггером 29 подсчитываются единичные биты в младших разрядах сообщения Y2 (3), и при обнаружении компаратором 9 равенства (2) выполняется последний (К-ый - см. (13) и (14)) период режима Р2, в котором формируются Z16=X18&Y14&Z9 для обеспечения возможности вставки контрольного бита Z29 в конец сообщения Y2 при Х18=1 согласно (3), Z7=!(C6& Z9)=0 для запрещения формирования инверсных счетных импульсов Z5 (17) и один инверсный импульс Z6=!(X17&Z15), по фронту которого триггер 8 пуска переключается из 1 в 0, а элемент 10 формирует единичный бит Y10 (5) окончания преобразования, означая переход преобразователя в режим Р3 (10). По сигналу Y10=1 непосредственно или через УУ осуществляется прерывание ЭВМ для дальнейшего программного управления преобразователем. Например, по первому импульсу NW0 сигнал Y10 (5) сбрасывается записью "0" в старший разряд С6 счетчика 1 по импульсу Z12=NW0 (12) либо начинается также подготовка преобразователя для выполнения очередной операции преобразования записью в регистр 21 байта D[7:0]= G[7:0].

Проведем сопоставление объемов оборудования (аппаратурных затрат) предлагаемого преобразователя и прототипа [7] при реализации их для n=32-разрядного информационного кодового входа на ИС серии 533 по методике, изложенной на с. 180 в монографии: Балашов Е.П., Пузанков Д.В. Проектирование информационно-управляющих систем. - М.: Радио и связь, 1987. - 256 с. ил. На основании этой методики объемы сравниваемых объектов рассчитываем в условных корпусах так, что за единицу измерения примем корпус ИС с 14-тью выводами (например, ИС 533ТМ2 - два D триггера), по отношению к которому корпус ИС с 16-тью выводами (например, ИС 533ИЕ7 - реверсивный 4-х разрядный счетчик с асинхронными обнулением и загрузкой) имеет весовой коэффициент 1,5.

Наименьший объем оборудования предлагаемый преобразователь будет иметь при реализации счетчика 1 на двух ИС 533ИЕ7, компаратора 9 на ИС 533СП1 и ИС 533ЛП5, триггеров 6 и 29 на одной ИС 533ТМ2, регистров 21-24 на четырех ИС 533ИР9, логических элементов 5-7, 11-16, 19, 20, 25-28 на одной ИС 533ЛН1 (шесть элементов НЕ), одной ИС 533ЛИ6 (двух элементах 4И), двух ИС 533ЛИ2 (восемь элементов 2И), одной ИС 533ЛА2 (четыре элемента 2И-НЕ) и одной ИС 533ЛЛ1 (четыре элемента ИЛИ).

Прототип [7] наименьший объем оборудования будет иметь при реализации счетчика 1 на двух ИС 533ИЕ7, дешифратора 4 на ИС 533ИД7 и ИС 533ЛН1 для формирования прямых выходных сигналов, коммутатора 4 на ИС 533КП7 (селектор-мультиплексор - восемь входов на один выход со стробированием), регистров 4 и 6 на 16 ИС 533ИР16 (16 четырехразрядных регистров сдвига с параллельным выходом, синхронным последовательно-параллельным вводом с тремя состояниями выходов с выбором по прямому сигналу) и одной ИС 533 ЛЛ1 (четыре элемента 2ИЛИ) для управления синхровходами регистров по ИЛИ при записи и при сдвиге, дешифратора 5 нуля на пяти ИС 533ЛЕ1 (20-ти элементах ИЛИ-НЕ) и двух ИС 533ЛА2 (двух элементах 8И-НЕ), генераторов 7 и 8 импульсов на двух ИС 533 (ТМ2 и ЛА3).

С учетом изложенного выше оценим объемы оборудовании предлагаемого преобразователя и прототипа [7] с помощью формулы

V=V1+V2+V3+V4, (18)

где V - объем оборудования устройства, оцениваемый в количестве условных корпусов, где за единицу измерения принят тип корпус ИС 533ТМ2, по отношению к которому тип корпуса любой из ИС 533 ИЕ7, СП1, ИР9, ИД7, КП7 имеет весовой коэффициент 1,5.

V1 - объем оборудования устройства, приходящийся на триггеры (ИС 533ТМ2);

V2 - объем оборудования, приходящийся на счетчик (две ИС 533ИЕ7);

V3 - объем оборудования, приходящийся на регистры (четыре ИС Р9 в предлагаемом преобразователе или 16 ИС ИР 16 + ИС ЛЛ1 в прототипе [7]);

V4 - объем оборудования, приходящийся на остальные составные части устройства.

На основании (18) получаем, что объемы оборудовании предлагаемого преобразователя и прототипа [7] оцениваются соответственно величинами

V1=1+3+6+8,5=18,5, (19)

V2=1+3+17+11,5=34 (20)

Сравнивая (19) и (20), получаем

V2/V1=1,836, (21)

что объем оборудования предлагаемого преобразователя примерно в 1,8 раза меньше объема оборудования прототипа [7].

Таким образом, по сравнению с прототипом [7] предлагаемый преобразователь, благодаря его существенным признакам, имеет более широкую область использования за счет значительного повышения уровня его программной управляемости (форматом преобразования согласно (13) и (14); длительности паузы согласно (15); возможности вставки контрольного бита Z29 в конец сообщения Y2 согласно (3)) и формирования им битов состояния (пуска Y8 триггером 8 пуска, режима преобразования Y14 (6) и окончания преобразования Y10 (5)) при значительно меньшем объеме оборудования (см. оценку (21)).

ЛИТЕРАТУРА

1. Хвощ С.Т. и др. Организация последовательных мультиплексных каналов систем автоматического управления. /С.Т. Хвощ, В.В. Дорошенко, В.В. Горовой, Под общ. ред. С.Т. Хвоща. - Л.: Машиностроение. Ленингр. Отд-ние, 1989. - 271 с., ил. "1.9. Последовательные каналы информационного обмена в коде RZ", с. (57-63).

2. Ю.В. Новиков, Д.Г. Карпенко. Аппаратура локальных сетей: функции, выбор, разработка. /Под общей редакцией Ю.В. Новикова. - М., Издательство ЭКОМ, 1988. - 288 с.: ил. "Рис.2.26. Использование универсального сдвигового регистра для преобразования кода", с. 104.

3. А. с. 656107, М.Кл. 2 G 11 C 19/00, СССР. Устройство сдвига цифровой информации. /В.И. Редченко, А.А. Изергин и И.И. Корниенко. Опубл. 05.04.1979. Бюл. 13.

4. А.с. 767751, М.Кл. 3 G 06 F 5/04, СССР. Преобразователь параллельного кода в последовательный. /В.А. Коломенский, В.Н. Свирин и Р.А. Чувильчикова. Опубл. 30.09.1980. Бюл. 36.

5. А.с. 857973, М.Кл. 3 G 06 F 5/04, СССР. Преобразователь параллельного кода в последовательный. /В.И. Дронов, И.Ю Когге и А.В. Балаболин. Опубл. 23.08.1981. Бюл. 31.

6. А.с. 1075253, 3 CSD G 06 F 5/02, СССР. Преобразователь параллельного кода в последовательный. /В.И. Редченко. Опубл. 23.02.1984. Бюл. 7.

7. ПРОТОТИП а.с. 1119002, 3CSD G 06 F, H 03 К 13/256, СССР. Преобразователь параллельного кода в последовательный. /А.А. Самчинский и Б.Г. Шаров. Опубл. 15.10.1984. Бюл. 38.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА И ПРЕОБРАЗОВАНИЯ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2001 |

|

RU2203520C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для выполнения операции преобразования параллельного кода в последовательный код сообщения с программируемой длительностью паузы начала преобразования после запуска преобразователя и программируемым форматом преобразования, формирования синхроимпульсов сопровождения сообщения, трех битов состояния и контрольного бита четности с обеспечением программной возможности вставки его в конец сообщения и может быть использован при построении контроллеров локальной сети. Техническим результатом является расширение области использования преобразователя и сокращение объема его оборудования. Устройство содержит счетчик, сдвигатель, три элемента И-НЕ, триггер пуска, компаратор, элемент ИЛИ-НЕ, шесть элементов И. 2 ил.

Преобразователь параллельного кода в последовательный, содержащий счетчик, сдвигатель, вход запуска, выход последовательного кода сообщения, являющийся выходом сдвигателя, выход синхроимпульсов сопровождения сообщения и n-разрядный информационный кодовый вход, являющийся информационным кодовым входом сдвигателя, отличающийся тем, что он содержит три элемента И-НЕ, триггер пуска, компаратор, элемент ИЛИ-НЕ, шесть элементов И, k=n/8 входов импульсов записи (при n, кратном восьми), соединенных с входами импульсов записи сдвигателя и входами первого элемента И, выход которого соединен с входом сброса триггера пуска и первым входом второго элемента И, тактовый вход, соединенный с первыми входами первого и второго элементов И-НЕ и третьего элемента И, выход бита пуска, соединенный с прямым выходом триггера пуска, вторым входом первого элемента И-НЕ и первыми входами четвертого элемента И и элемента ИЛИ-НЕ, m-разрядный (где 2 в степени m не меньше, чем n) программный кодовый вход формата преобразования, являющийся первым информационным кодовым входом компаратора, выход которого соединен с первыми входами третьего элемента И-НЕ и пятого элемента И, программный битовый вход разрешения вставки контрольного бита в конец сообщения, соединенный с первым входом шестого элемента И, выход бита окончания преобразования, являющийся выходом элемента ИЛИ-НЕ, второй вход которого соединен с выходом третьего элемента И-НЕ и третьим входом первого элемента И-НЕ, выход которого соединен с счетным входом счетчика, информационные выходы m младших разрядов которого соединены с вторым информационным кодовым входом компаратора, и выход бита режима преобразования, соединенный с выходом четвертого элемента И и вторыми входами третьего и пятого элементов И, причем выход третьего элемента И соединен с синхровходом сдвигателя и выходом синхроимпульсов сопровождения сообщения преобразователя, вход запуска преобразователя соединен с установочными входами сдвигателя и триггера пуска и вторым входом второго элемента И, выход которого соединен с входом записи счетчика, информационный выход старшего разряда которого соединен с вторыми входами третьего элемента И-НЕ и четвертого элемента И, входы q (q не меньше m) младших разрядов информационного кодового входа преобразователя соединены с информационными входами младших разрядов счетчика, информационный вход старшего разряда которого соединен с шиной логического нуля (корпусом) преобразователя и информационным входом триггера пуска, синхровход которого соединен с выходом второго элемента И-НЕ, второй вход которого соединен с выходом пятого элемента И и вторым входом шестого элемента И, выход которого соединен с управляющим входом сдвигателя, который содержит два элемента ИЛИ, k байтовых регистров с асинхронным параллельным вводом и синхронизирующим последовательным выводом кодов младшими разрядами вперед, два элемента НЕ, седьмой и восьмой элементы И, и триггер контрольного бита, вход установки которого является входом установки сдвигателя, входы n-разрядного информационного кодового входа которого соединены с информационными параллельными входами регистров сдвигателя так, что первый регистр является младшим, а k-й регистр старшим, последовательный выход которого через все предыдущие регистры связан с последовательным входом первого регистра, прямой последовательный выход которого соединен с последовательным входом k-го регистра и первым входом седьмого элемента И, выход которого соединен с входом первого элемента ИЛИ, второй вход которого соединен с выходом восьмого элемента И, а выход первого элемента ИЛИ является выходом сдвигателя, k входов импульсов записи которого соответственно соединены с асинхронными входами записи регистров с первого по k-й, синхровход сдвигателя связан через первый элемент НЕ с синхровходами всех регистров и первым входом второго элемента ИЛИ, второй вход которого соединен с инверсным последовательным выходом первого регистра, а выход соединен с синхровходом триггера контрольного бита, вход сброса которого соединен с шиной логической единицы преобразователя, управляющий вход сдвигателя соединен с первым входом восьмого элемента И и связан через второй элемент НЕ с вторым входом седьмого элемента И, второй вход восьмого элемента И соединен с прямым выходом триггера контрольного бита, инверсный выход которого соединен с его информационным входом, а инверсные входы разрешения сдвига всех регистров соединены с шиной логического нуля преобразователя.

| Преобразователь параллельного кода в последовательный | 1983 |

|

SU1119002A1 |

| Преобразователь параллельного кода в последовательный | 1982 |

|

SU1075253A1 |

| Преобразователь параллельного кода в последовательный | 1979 |

|

SU857973A1 |

| Преобразователь параллельного кода в последовательный | 1977 |

|

SU767751A1 |

| Устройство сдвига цифровой информации | 1977 |

|

SU656107A2 |

| Устройство преобразования параллельного кода в последовательный | 1987 |

|

SU1474853A1 |

| Преобразователь параллельного кода в последовательный | 1987 |

|

SU1547076A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 1997 |

|

RU2121754C1 |

| US 4885584 А, 05.12.1989 | |||

| МЕТОДИЧЕСКАЯ ПЕЧЬ ДЛЯ РАДИАЦИОННОГО НАГРЕВА | 0 |

|

SU313875A1 |

Авторы

Даты

2002-08-20—Публикация

2000-10-30—Подача