к

СП

со

00

со

Фм

Изобретение относится к технике связи.

Цель изобретения - повышение помехоустойчивости при одновременном упрощении .

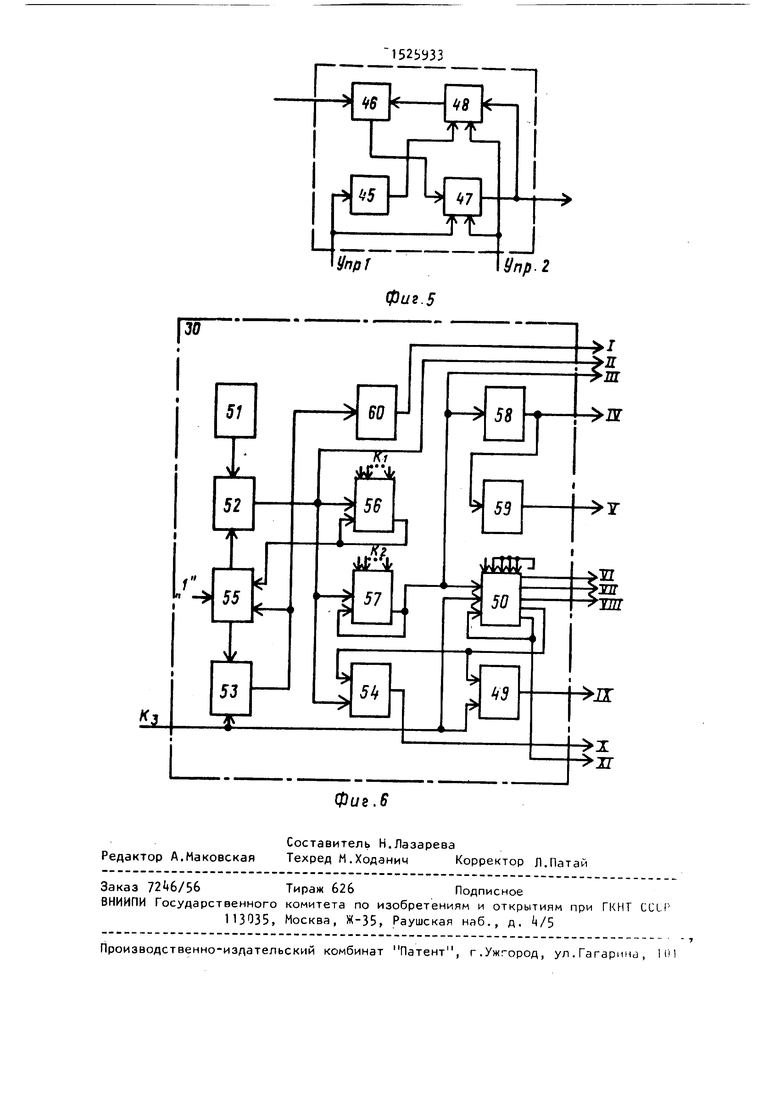

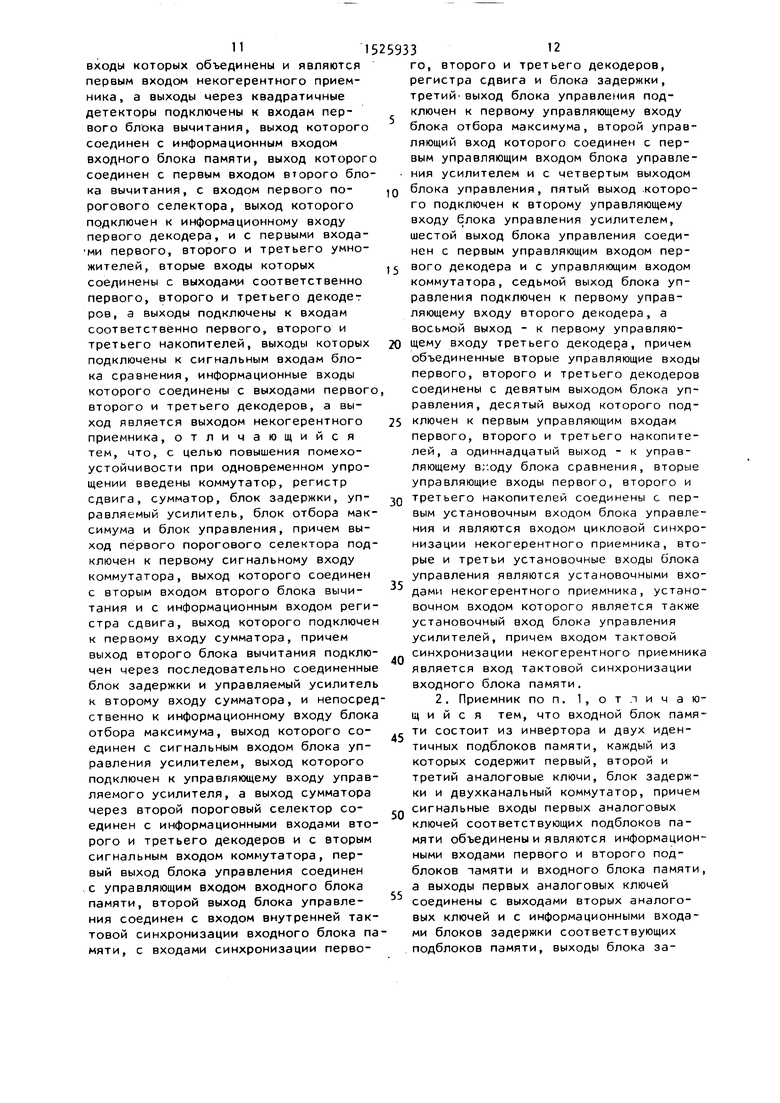

На фиг, 1 изображена структурная электрическая схема предлагаемого устройства; .на фиг. 2 - схема входного блока памяти; на фиг. 3 - схема блока Q отбора максимума; на фиг. j - схема блока управления усилителем; на фиг.5 - схема накопителя; на фиг. 6 - схема блока управления.

Некогерентный приемник содержит гласованные фильтры 1,2, квадратичные детекторы .3,, первый блок 5 вычитания, выходной блок 6 памяти, второй блок 7 вычитания, первый пороговый селектор 8, первый, второй и третий умнотд жители 9 - 11, первый, второй и третий декодеры 12 - И, каналы 15-17 обраотки, состоящие из первого, второо и третьего накопителей 18 - 20 и умножителей 9 11, блок 21 срав- 25 нения, коммутатор 22, регистр 23 двига, сумматор 2, блок 25 заержки, управляемый усилитель 26, лок 27 отбора максимума, блок 28 правления усилителем, второй поро- . говый селектор 29, блок 30 управления.

Входной блок 6 памяти содержит подблоки 31 памяти, инвертор 32, каждый подблок 31 состоит из первых, вторых и третьих аналоговых ключей 33 - 35, блока Зб задержки и двухканального коммутатора 37.

Блок 27 отбора максимума состоит из ячеек 38,39 памяти и блока lO сравнения,

Блок 28 управления усилителем сое- тоит из усилителя 1, блока 2 сравнения, ключа +3 и интегратора .

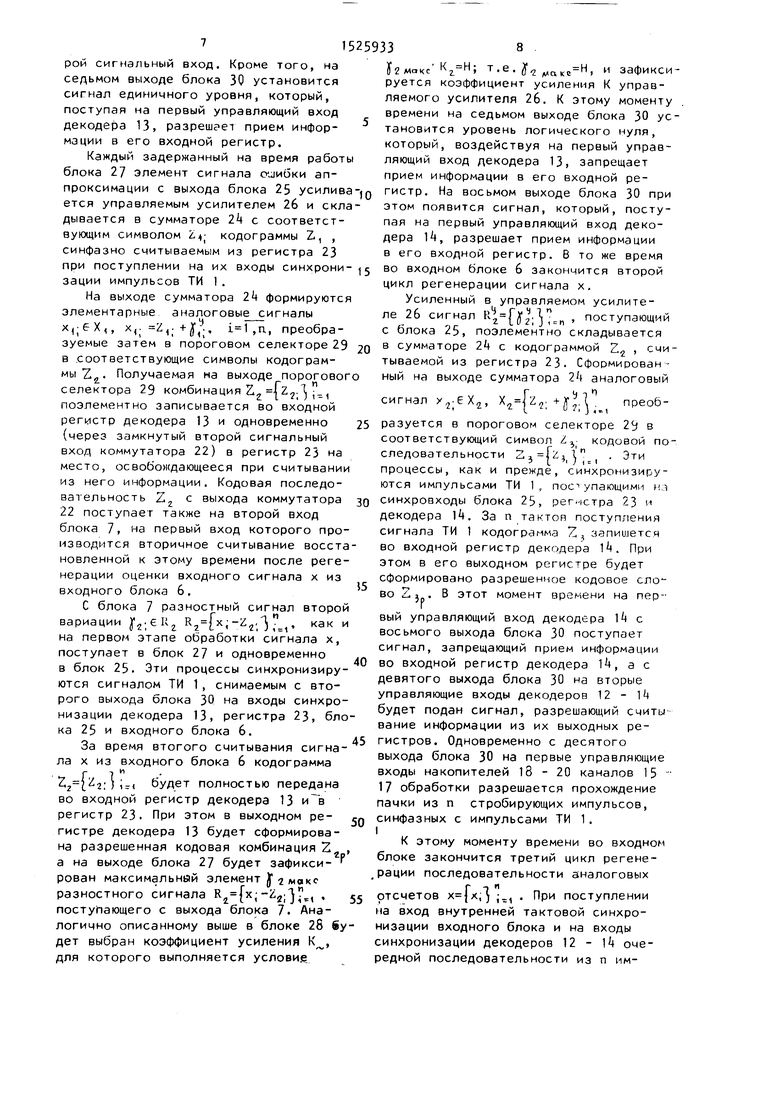

Накопитель 15 (1б,17) состоит из инвертора S, сумматора б и ячеек 7, 8 памяти.

Блок 30 управления содерж+1т RS- триггер , кольцевой регистр 50, генератор 51 тактовых импульсов, первый, второй, третий элементы И 52 - S , D-триггер 55, первый и второй счетчи- 50 ки 56,57, блок 58 задержки, инвертор 59, Т-триггер 60.

Некогерентный приемник работает следующим образом.

Перед первым включением устройства 55 в систему связи на установочных вхо- дах К, 6jioKa 30 управления (ВУ) устанавливается (например, с пульта) дво45

Q

с д 5

0

5

ичный эквивалент числа, соответствующего пятикратной длине кодового блока, а на установочных входах К, - двоичный эквивалент числа, соответствующего длине кодовой комбинации. Кроме того, на входе установки порогового напряжения блока 28 управления усилителем (БУУ) фиксируется потенциал, соответствующий используемому каналу связи.

За время установления синхронизации (после поступления сигнала цикловой синхронизации на установочный вход Kj блока 30) устройство приводится в состояние готовности к приему и обработке входного сигнала, при котором первый подблок памяти входного блока 6 памяти (БП) установлен сигналом, поступающим с первого выхода блока 30 на управляющий вход входного блока 6, в режим приема входной информации, а второй подблок памяти входного блока 6 - в режим выдачи-хранения принятой на предыдущем цикле информации; блок 27 отбора максимума устанавливается в режим готовности приема информации сигналом, поступающим с третьего выхода блока . 30 на первый управляющий вход блока 27; накопители 18 - 20 сбрасываются в нулевое состояние сигналом синхронизации (СП), поступающим на их вторые управляющие входы; в блоке 21 сравнения информационные входы закрываются сигналом, поступающий с девятого выхода блока 30; сигналом, поступающим с шестого выхода блока 30 на управляющий вход коммутатора 22 и на первый управляющий вход декодера 12, к выходу коммутатора 22 подключается его первый сигнальный вход, а в ,текодере 12 разрешается прием информации во - входной регистр; входные регистры декодеров 13 и I закрыты сигналами, поступающими соответственно с седьмого и восьмого выходов блока 30 на первые управляющие входы этих декодеров.

На вход приёмника поступает аналоговый сигнал, сформированный на основе разрешенной комбинации принимаемого помехоустойчивого кода. Каждый входной элементарный сигнал предварительно обрабатывается в двух параллельных каналах, состоящих из согласованных фильтров 1 и 2 и квадратичных детекторов 3 и , На выходе каналов формируются аналоговые элементарные сигналы, определяющие соответствующие ортогональные проекции входного сигнала. Эти сигналы поступают на входы блока 5 вычитания, с выхода которого их разность в виде последовательности разностных эле ментарных аналоговых сигналов xj , j 1,,n запоминается в ячейках входного блока 5 при синхронном поступлении на вход внешней тактовой синхронизации блока 6 строби- рующих импульсов ТИ. Одновременно из второго подблока памяти на последующие

Блок 27 прои еолит равнен|1е гмппп туд элементов , ,п пос тупаю-.цег п на его вход сигнала, В результате оЬ работки всех п компонент разностного сигнала R, ( J,;,B блоке 27 будет получен элемент сигнала с максимальнг,); амплитудой У , ,д,р, который импульсам.и, поступающими с третьего и четвертого выходов блока 3U соответственно на первый и второй управляющие входы блока 27, будет выдан на вы код блока 27. При этом блок 27 будет приведен в исходное состояние готовности

| название | год | авторы | номер документа |

|---|---|---|---|

| Информационно-управляющая система центрального теплового пункта жилых общественных и промышленных зданий | 1987 |

|

SU1511751A1 |

| Некогерентный приемник | 1981 |

|

SU1003370A1 |

| Устройство для приема избыточной информации | 1981 |

|

SU978373A1 |

| РАДИОМОДЕМ | 2024 |

|

RU2830959C1 |

| УСТРОЙСТВО ПРИЕМА И ОБРАБОТКИ ИНФОРМАЦИИ | 2002 |

|

RU2213424C1 |

| МНОГОКАНАЛЬНАЯ ТЕЛЕМЕТРИЧЕСКАЯ СИСТЕМА СБОРА СЕЙСМИЧЕСКИХ ДАННЫХ | 2003 |

|

RU2244945C1 |

| Устройство для зондирования ионосферы | 1990 |

|

SU1742762A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| Устройство для сопряжения вычислительной машины с каналами связи | 1980 |

|

SU918944A1 |

| Устройство для коммутации сообщений | 1988 |

|

SU1529235A1 |

Изобретение относится к технике связи. Цель изобретения - повышение помехоустойчивости при одновременном упрощении. Некогерентный приемник содержит согласованные фильтры 1 и 2, квадратичные детекторы 3 и 4, блоки вычитания 5 и 7, блок памяти 6, пороговые селекторы 8 и 29, декодеры 12, 13 и 14, каналы 15, 16 и 17 обработки, состоящие из умножителей 9, 10 и 11 и накопителей 18, 19 и 20, блок сравнения 21. Цель достигается введением коммутатора 22, регистра 23 сдвига, сумматора 24, блока задержки 25, управляемого усилителя 26 с его блоком управления 28, блока отбора 27 максимума и блока управления 30, с помощью которых осуществляются циклы оценки входного сигнала. При этом анализируются соотношения величин выходных сигналов и к выходу приемника подключается тот декодер, которому соответствует канал обработки сигнала с наибольшей амплитудой выходного сигнала. Приемник по п.п. 2 - 6 ф-лы отличается выполнением блока памяти 6, накопителей 18, 19, и 20, блоков управления 28 и 30 и блока отбора 27. 5 з.п. ф-лы, 6 ил.

каскады приемника считывается последо-,к приему следующей последовательности

вательность элементарных сигналов,аналоговых отсчетов сигнала ошибки

принятая во входной блок 6 на предыду-аппроксимации jj. , ,n. щем цикле работы устройства. Эта ком- Одновременно импульс, поступающий

бинация аналоговых отсчетов, представ-с четвертого выхода блока 30 на перляющая собой точную оценку . 20вый управляющий вход блока 28, уставходного избыточного сигнала, считыва-навливает блок 2 в состояние готовется из входного блока 6 (с регенера-ности приема входной информации,

цией) с частотой поступающих на входПо окончании установочного импульса внутренней тактовой синхронизации блока 6 стробирующих импульсов ТИ 1 с второго выхода блока 30.

Первое считывание оценки аналогового сигнала х из входного блока 6 производится на первый вход блока 7 вычитания и на пороговый селектор 8, на выходе которого формируется двоичнаякодовая последовательность Z,; ,

,n, где Z,; Signx; -аппроксимирующая комбинация аналоговых отсчетов , Элементы кодограммы Z,z, последовательно поступают во входной регистр декодера 12 для вторичной обработки. Кодограмма Z, через замкнутый первый сигнальный вход коммутатора 22 посимвольно передается на информационный вход регистра 23 сдвига, в который она записывается синфазно поступающими с второго выхода блока 30 на синхровход ре25

30

на первом управляющем входе блока 28 на его второй управляющий вход с пятого выхода блока 30 поступает сигнал запускающий, например, генеоатор линейно изменяющегося напряжения, выходное напряжение которого управляет коэффициентом усиления управляемого усилителя 26. При этом в блоке 28 осуществляется контроль выходной величины управляемого усилителя 26. В момент достижения амплитудой

If, . К значения порога h, заданного на входе установки порогового напряжения блока 28, потенциал на выходе генератора линейно изменяющего ся напряжения, а следовательно,

выбранный коэффициент усиления К, управляемого усилителя 26 фиксируется .

В этот момент времени закончит40

50

гистра 23 импульсами ТИ 1. Одновремен- ся первое считывание комбинации ана- но двоичная комбинация Z, с выхода логовых отсчетов из входного блока 6. коммутатора 22 поступает на второй вход блока 7 синхронно со считываемой на его первый вход комбинацией аналоговых отсчетов X, при этом на выходе блока 7 для каждого i-ro элемента . . оценки X, ,п будет сформирован аналоговый сигнал ошибки аппроксимации y,; x;-Zv .,n. Последовательность элементов сигнала Ri(f(, поступает в блоки 27 и 25 для задержки на время работы блока 27 синхронно поступающими на ее вход синхронизации имНа шестом выходе блока 30 установится уровень логического нуля, поступающий на первый управляющий вход декодера 12 и управляющий вход коммутатора 22, При этом прием информации во входной регистр декодера 12 будет запрещен, а в его выходном регистре будет храниться полученное в результате обработки кодограммь Z,, принятой на пер- вом этапе работы устройства, разрешенное кодовое слово Тц . Коммутатор 22 переключится в состояние, при KOTO- DOM к его выходу будет подключен втопульсами ТИ 1 .

По окончании установочного импульса

5

0

на первом управляющем входе блока 28 на его второй управляющий вход с пятого выхода блока 30 поступает сигнал, запускающий, например, генеоатор линейно изменяющегося напряжения, выходное напряжение которого управляет коэффициентом усиления управляемого усилителя 26. При этом в блоке 28 осуществляется контроль выходной величины управляемого усилителя 26. В момент достижения амплитудой

If, . К значения порога h, заданного на входе установки порогового напряжения блока 28, потенциал на выходе генератора линейно изменяющегося напряжения, а следовательно,

выбранный коэффициент усиления К, управляемого усилителя 26 фиксируется .

В этот момент времени закончит0

ся первое считывание комбинации ана- логовых отсчетов из входного блока 6.

На шестом выходе блока 30 установится уровень логического нуля, поступающий на первый управляющий вход декодера 12 и управляющий вход коммутатора 22, При этом прием информации во входной регистр декодера 12 будет запрещен, а в его выходном регистре будет храниться полученное в результате обработки кодограммь Z,, принятой на пер- вом этапе работы устройства, разрешенное кодовое слово Тц . Коммутатор 22 переключится в состояние, при KOTO- DOM к его выходу будет подключен второй сигнальный вход. Кроме того, на седьмом выходе блока 30 установится сигнал единичного уровня, который, поступая на первый управляющий вход декодера 13, разрешает прием информации в его входной регистр.

Каждый задержанный на время работы блока 27 элемент сигнала саибки аппроксимации с выхода блока 25 усиливается управляемым усилителем 26 и складывается в сумматоре 2А с соответствующим символом кодограммы Z, , синфазно считываемым из регистра 23

при поступлении на их входы синхрони- 5 о входном блоке 6 закончится второй

цикл регенерации сигнала х.

Усиленный в управляемом усилителе 26 сигнал - 2; зации импульсов ТИ

На выходе сумматора 2 формируются элементарные аналоговые сигналы

(. i; 1; (V 1.П 1 преобразуемые затем в пороговом селекторе 29 в соответствующие символы кодограммы Z. Получаемая на выходе порогового

- 2.Р М

селектора 29 комбинация Z |2.1| ;, поэлементно записывается во входной регистр декодера 13 и одновременно (через замкнутый второй сигнальный вход коммутатора 22) в регистр 23 на место, освобождающееся при считывании из него информации. Кодовая последовательность Z с выхода коммутатора 22 поступает также на второй вход блока 7, на первый вход которого производится вторичное считывание восстановленной к этому времени после регенерации оценки входного сигнала х из входного блока 6.

С блока 7 разностный сигнал второй

вариации fj; ,1) i на первом этапе обработки сигнала х, поступает в блок 27 и одновременно в блок 25. Эти процессы синхронизируются сигналом ТИ 1, снимаемым с второго выхода блока 30 на входы синхронизации декодера 13, регистра 23, блока 25 и входного блока 6.

За время втогого считывания сигнала X из входного блока 6 кодограмма

Г 7

J ir( будет полностью передана во входной регистр декодера 13 регистр 23. При этом в выходном регистре декодера 13 будет сформирована разрешенная кодовая комбинация 2 , а на выходе блока 27 будет зафикси-

поступающий

с блока 25, поэлементно складывается 2Q в сумматоре 2Ц с кодограммой Z , счи тываемой из регистра 23. Сформированный на выходе сумматора 2 t аналоговый

Г 9 т сигнал у,,.еХ2, Z,; + у . t , преоб25 разуется в пороговом селекторе 2) в соответствующий символ Z. кодовой по следовательности , , Эти процессы, как и прежде, синхронизируются импульсами ТИ 1, пос упающими из

30 синхровходы блока 25, рег -ютра 23 и декодера lA. За п тактои поступления сигнала ТИ 1 кодограмма Z, запишется во входной регистр декодера И. При этом в его выходном регистре будет сформировано разрешенное кодовое слово Z j . В этот момент времени на первый управляющий вход декодера с восьмого выхода блока 30 поступает сигнал, запрещающий прием информации

40 во входной регистр декодера 1, а с девятого выхода блока 30 на вторые управляющие входы декодеров 12 - 14 будет подан сигнал, разрешающий считы вание информации из их выходных ре45 гистров. Одновременно с десятого

выхода блока 30 на первые управляющие входы накопителей 18-20 каналов 15 17 обработки разрешается прохождение пачки из п стробирующих импульсов,

5Q синфазных с импульсами ТИ 1.

К этому моменту времени во входном блоке закончится третий цикл регене 5

рован максимальней элемент Jf макс

разностного сигнала поступающего с выхода блока 7. Аналогично описанному выше в блоке 28 будет выбран коэффициент усиления К, для которого выполняется услови.«г

рации последовательности аналоговых

55 отсчетов ;, . При поступлении на вход внутренней тактовой синхронизации входного блока и на входы синхронизации декодеров 12 - И очередной последовательности из п имУ 2 макс ;

г- -Й -г vc4cc зафиксируется коэффициент усиления К управляемого усилителя 26. К этому моменту времени на седьмом выходе блока 30 установится уровень логического нуля, который, воздействуя на первый управляющий вход декодера 13, запрещает прием информации в его входной регистр. На восьмом выходе блока 30 при этом появится сигнал, который, поступая на первый управляющий вход декодера , разрешает прием информации в его входной регистр. В то же время

Усиленный в управляемом усилителе 26 сигнал - 2; поступающий

с блока 25, поэлементно складывается Q в сумматоре 2Ц с кодограммой Z , считываемой из регистра 23. Сформированный на выходе сумматора 2 t аналоговый

Г 9 т сигнал у,,.еХ2, Z,; + у . t , преоб5 разуется в пороговом селекторе 2) в соответствующий символ Z. кодовой последовательности , , Эти процессы, как и прежде, синхронизируются импульсами ТИ 1, пос упающими из

0 синхровходы блока 25, рег -ютра 23 и декодера lA. За п тактои поступления сигнала ТИ 1 кодограмма Z, запишется во входной регистр декодера И. При этом в его выходном регистре будет сформировано разрешенное кодовое слово Z j . В этот момент времени на первый управляющий вход декодера с восьмого выхода блока 30 поступает сигнал, запрещающий прием информации

0 во входной регистр декодера 1, а с девятого выхода блока 30 на вторые управляющие входы декодеров 12 - 14 будет подан сигнал, разрешающий считы вание информации из их выходных ре5 гистров. Одновременно с десятого

выхода блока 30 на первые управляющие входы накопителей 18-20 каналов 15 17 обработки разрешается прохождение пачки из п стробирующих импульсов,

Q синфазных с импульсами ТИ 1.

К этому моменту времени во входном блоке закончится третий цикл регене 5

рации последовательности аналоговых

55 отсчетов ;, . При поступлении на вход внутренней тактовой синхронизации входного блока и на входы синхронизации декодеров 12 - И очередной последовательности из п импульсов ТИ 1 на вторые входы умножителей 9-11 будет производиться последовательное считывание элементов сигнала х из входного блока 6, а на первые входы умножителей 9 11 из выходных регистров соответствующих декодеров 12 - 1 будут синхронно считываться разрешенные ..кодовые комбинации Z, , 21 г Р

и 7, .С выходов умножителей 9 1 1

Р

результаты поэлементного умножения выдаются на информационные входы соответствующих накопителей 18 -20, установленных в нулевое состояние импульсом синхронизации, поступившим на их вторые управляющие входы в начале цикла обработки оцент. х входного сигнала.

После выдачи с десятого выхода блока 3fi на первые управляющие входы накопителей 18 - 20 всей пачки из п импульсов стробирования (это соответствует окончанию четвертого цикла регенерации сигнала X во входном блоке 6) на выходе каждого из них будут сформированы сигналы, амплитуды которых про- пори.иональны степеням близости между сигналом X и соответствующими разре- шечными кодовыми словами Z,p, Z.2p

и Z При этом на десятом выходе

блока 30 фиксируется уровень логического нуля (при котором накопители 18 20устанавливаются в режим хранения сформированных на их выходах потенциалов, а на управляющем входе блока

21устанавливается разрешающий уро-. вень сигнала, поступающего с одиннадцатого выхода блока 30.

Выходные сигналы U., U и IJ накопителей 18-20 поступают на соответствующие сигнальные входы блока 21, выполняющего функции устройства принятия решения в некогерентном приемнике В результате анализа соотношений величин сигналов блок 21 подключает к выходу приемника выходной регистр того декодера, которому соответствует канал обработки сигнала с наибольшей амплитудой выходного сигнала V.,),b

Этот момент времени соответствует готовности устройства к этапу выдачи обработанной информации на выход приемника .

С поступлением очередной последовательности п импульсов ТИ 1 (это соответствует пятой регенерации комбина

ции отсчетов во входном блоке 6) на входы синхронизации декодеров 12 - 1 на выходе приемника через соответствующий информационный вход блока 21 считывается разрешенная кодовая комбинация Z, из выходного регистра

выбранного декодера.

По окончании выдачи последнего сим10 вола разрешенного кодового блока 2,

Р

на выход приемника с одиннадцатого выхода блока 30 на управляющий вход блока 21 поступает сигнал, отключающий

., информационные входы блока 21 от выхода приемного устройства.

Кроме того, с шестого выхода блока 30 на первый управляющий вход декодера 12 и на управляющий вход ком20 мутатора 22 поступает сигнал единичного уровни, при котором к выходу коммутатора 22 подключается его первый сигнальный вход, а входной регистр декодера 12 открывается для приема очеред25 ной кодограммы, формируемой в пороговом селекторе 8 в результате прохождения через него комбинации аналоговых отсчетов, принятых к этому времени Бо входной блок 6, т.е. приемное

Q устройство приводится в исходное состояние, в котором оно будет находиться до поступления очередного импульса цикловой синх.ронизации СИ.

При поступлении следующего импульса СИ накопители 15 - 20 соответст 5 вуюцих каналов 15 - 17 обработки обну- лятся, а на первом выходе блока 30 установится потенциал, который переключит реким работы подблоков памяти во входном блоке 6, причем подблок памяти, который работал на предыдущем цикле в режиме выдачи-хранения информации, установится в режим приема аналогового сигнала, поступающего с выхода первого блока 5, а второй подблок памяти - в режим выдачи-хранения принятой комбинации аналоговых отсчетов оценки очередного сигнала ссюбщения.

Далее все процессы обработки принятого во входной блок 6 сигнала протекают аналогично описанным выше.

40

45

50

Формула изобретения

входы которых объединены и являются первым входом некогерентного приемника, а выходы через квадратичные детекторы подключены к входам первого блока вычитания, выход которого соединен с информационным входом входного блока памяти, выход которого соединен с первым входом второго блока вычитания, с входом первого порогового селектора, выход которого подключен к информационному входу первого декодера, и с первыми входа- ми первого, второго и третьего умножителей, вторые входы которых соединены с выходами соответственно первого, второго и третьего декодет ров, а выходы подключены к входам соответственно первого, второго и третьего накопителей, выходы которых подключены к сигнальным входам блока сравнения, информационные входы которого соединены с выходами первого второго и третьего декодеров, а выход является выходом некогерентного приемника, отличающийся тем, что, с целью повышения помехоустойчивости при одновременном упрощении введены коммутатор, регистр сдвига, сумматор, блок задержки, управляемый усилитель, блок отбора максимума и блок управления, причем выход первого порогового селектора подключен к первому сигнальному входу коммутатора, выход которого соединен с вторым входом второго блока вычитания и с информационным входом регистра сдвига, выход которого подключен к первому входу сумматора, причем выход второго блока вычитания подключен через последовательно соединенные блок задержки и управляемый усилитель к второму входу сумматора, и непосредственно к информационному входу блока отбора максимума, выход которого соединен с сигнальным входом блока управления усилителем, выход которого подключен к управляющему входу управляемого усилителя, а выход сумматора через второй пороговый селектор соединен с информационными входами второго и третьего декодеров и с вторым сигнальным входом коммутатора, первый выход блока управления соединен с управляющим входом входного блока памяти, второй выход блока управления соединен с входом внутренней тактовой синхронизации входного блока памяти, с входами синхронизации перво

5

0

5

0

5

0

5

0

5

ГО, второго и третьего декодеров, регистра сдвига и блока задержки, третий выход блока управления подключен к первому управляющему входу блока отбора максимума, второй управляющий вход которого соединен с первым управляющим входом блока управления усилителем и с четвертым выходом блока управления, пятый выход которого подключен к второму управляющему входу блока управления усилителем, шестой выход блока управления соединен с первым управляющим входом первого декодера и с управляющим входом коммутатора, седьмой выход блока управления подключен к первому управляющему входу второго декодера, а восьмой выход - к первому управляющему входу третьего декодера, причем объединенные вторые управляющие входы первого, второго и третьего декодеров соединены с девятым выходом блока управления, десятый выход которого подключен к первым управляющим входам первого, второго и третьего накопителей, а одиннадцатый выход - к управляющему вг.оду блока сравнения, вторые управляющие входы первого, второго и третьего накопителей соединены с первым установочным входом блока управления и являются входом цикловой синхронизации некогерентного приемника, вторые и третьи установочные входы блока управления являются установочными входами некогерентного приемника, установочном входом которого является также установочный вход блока управления усилителей, причем входом тактовой синхронизации некогерентного приемника является вход тактовой синхронизации входного блока памяти,

дермки в каждом подблоке памяти объединены с входами второго и третьего аналоговых ключей, выходы третьих ана логовых ключей, являющиеся информационными выходами соответствующих подблоков памяти, объединены и являются выходом входного.блока памяти, при чем управляющие входы первого аналогового ключа и двухканального коммутатора первого подблока памяти и управляющие входы второго и третьего аналоговых к.ючей второго подблока памяти подключены к входу инвертора, являющемуся управляющим входом входного блока памяти, а выход инвертора соединен с управляющими входами второго и третьего аналоговых ключей пер вого подблока ламяти и с управляющими входами первого аналогового ключа и двухканального коммутатора второго подблока памяти, выход двухканального коммутатооа в подблоке памяти соединен с входом синхронизации бло1-;а задеожки, причем первые сигналь ные входы дв: хклнальных коммутаторов обоих подблоков памяти объединены и являются входом тактовой синхрониза- ци1 | вхг. блока памяти, а вторые сигнальные в/оды двухканальных комму- jTopon являются входом внутренней тактовой си -1/ронизации входного блока памяти.

Ц. Приемник по п. 1,отличаю lit и и с я тем, что блок управления усилителем состоит из усилителя, блока сравнения, ключа и интегратора, причем вход усилителя является сиг5

ЬУЗЗ

нальным входом блока управления усилителем, а выход подключен к первому входу блока сравнения, второй вход которого является установочным входом некогерентного приемника, выход блока сравнения соединен с управляющим входом ключа, сигнальный вход которого является вторым управляющим вхоjQ дом блока управления усилителем, а выход ключа соединен с сигнальным входом интегратора, выход которого соединен с управляющим входом усилителя и является выходом блока управления усилитеI г лем, установочный вход интегратора является первым управляющим входом блока управления усилителем.

20 максимума состоит из двух ячеек памяти и блока сравнения, первый вход которого, являющийся информационным входом блока отбора максимума, соединен с информационным входом первой 25 ячейки памяти, выход которой подключен к второму входу блока сравнения и к информационному входу второй ячейкч памяти, выход которой является выходом блока отбора макс: мума, а

oQ первый управляющий является первым у; равляющим. входом блока отбора максимума, вторым управляющим входом которого является первый управляющий вход первой ячейки памяти, второй управляющий вход которой соединен

с выходом блока сравнения.

45

50

55

единен с выходом первого элемента И, который является вторым выходом блока управления, со счетным входом второго счетчика и с первым входом третьего элемента И, причем выход второго счетчика, являющийся третьим выходом блока управления, соединен с входом записи кода второго счетчика, информационные входы которого являются вторыми установочными входами блока управления. Выход второго счетчика соединен также через блок задержки с входом инвертора, выход которого является пятым выходом блока управления, четвертым выходом которого является выход блока задержки, выход второго счетчика соединен с входом последовательного приема кольцевого регистра, выходы первого, второго и третьего разрядов кольцевого регистра являютФиг. Z

У пр. г ynft.J фик.з

ся соответственно шестым, седьмым и восьмым выходами блока управления,, выход четвертого разряда кольцевого регистра подключен к первому установочному входу RS-триггера, выход которого является девятым выходом блока управления, и к втор ому входу третьего элемента И, выход которого является десятым .выходом блока управления, информационный вход кольцевого регистра объединен с вторым установочным входом КЗ-триггера, с вторым входом второго элемента И и

является третьим установочным входом блока управления, а выход пятого разряда кольцевого регистра подключен к информационному входу последовательного приема информации кольцевого регистра и является одиннадцатым выходом блока управления.

Упр.2 Упр.Г

Фиг.

Ипр-2

фиг.5

| Управляемый аэростат | 1927 |

|

SU10033A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| () НЕКОГЕРЕНТНЫИ ПРИЕМНИК | |||

Авторы

Даты

1989-11-30—Публикация

1988-01-19—Подача