(21)4377826/24-10

(22)17.02.88

(46) 07.12.89. БЕОЛ. № 45

(72) И.В. Чуманов и Л.И. Чуманова

(53)681.84(088.8)

(56)Авторское свидетельство СССР № 1332376, кл. G 11В 27/36, 24.03.86.

Авторское свидетельство СССР № 1273994, кл. G 11В 27/36, 29.04.85.

(54)УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ОШИБОК ВОСПРОИЗВЕДЕНИЯ ИНФОРКД.ЦИИ С НОСИТЕЛЯ МАГНИТНОЙ ЗАПИСИ

(57)Изобретение относится к прибо- боростроению, технике магнитной записи информации и может быть использовано для контроля потоков ошибок канала цифровой магнитной записи. Цель изобретения - повьппение точности контроля ошибок за счет индикации структуры пакета ошибок сигнала магнитной записи. Указанная цель достигается тем, что в устройство, содержащее входную шину I сигнала, шину 2 псевдослучайной последовательности, первый 3 и пторой 4 сумматоры по модулю два, первый 5 и второй 6 регистры сдвига, коммутатор 7, первый 8 детектор ошибок, триггер 9, второй 10 детектор ошибок, введены второй триггер П, элемент И 12, инвертор 13, индикатор 14 и элемент 15 управления. Устройство позволяет идентифицировать ошибку воспроизведения и тип ее в пакете . 1 ил.

С

(Л

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля ошибок магнитной записи-воспроизведения цифровой информации | 1985 |

|

SU1273994A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для контроля ошибок многоканального аппарата магнитной записи | 1987 |

|

SU1432604A1 |

| Устройство диагностического контроля аппаратуры цифровой магнитной записи | 1987 |

|

SU1478253A1 |

| Устройство для контроля ошибок цифровой магнитной записи | 1985 |

|

SU1283847A1 |

| Устройство для контроля аппарата магнитной записи | 1985 |

|

SU1283848A1 |

| Устройство для контроля ошибок воспроизведения информации с носителя магнитной записи | 1989 |

|

SU1619339A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

Изобретение относится к приборостроению, технике магнитной записи информации и может быть использовано для контроля потоков ошибок канала цифровой магнитной записи. Цель изобретения - повышение точности контроля ошибок за счет индикации структуры пакета ошибок сигнала магнитной записи. Указанная цель достигается тем, что в устройство, содержащее входную шину 1 сигнала, шину 2 псевдослучайной последовательности, первый 3 и второй 4 сумматоры по модулю два, первый 5 и второй 6 регистры сдвига, коммутатор 7, первый 8 детектор ошибок, триггер 9, второй 10 детектор ошибок, введены второй триггер 11, элемент И 12, инвертор 13, индикатор 14 и элемент 15 управления. Устройство позволяет идентифицировать ошибку воспроизведения и тип ее в пакете. 1 ил.

Изобретение относится к приборостроению, к технике магнитной записи и может быть использовано в отдельной аппаратуре контроля для исследования потоков ошибок канала цифровой магнитной записи-воспроизведения.

Цель изобретения - повышение точности контроля ошибок за счет индикации структуры пакета ошибок сигна- ла воспроизведения с носителя магнитной записи.

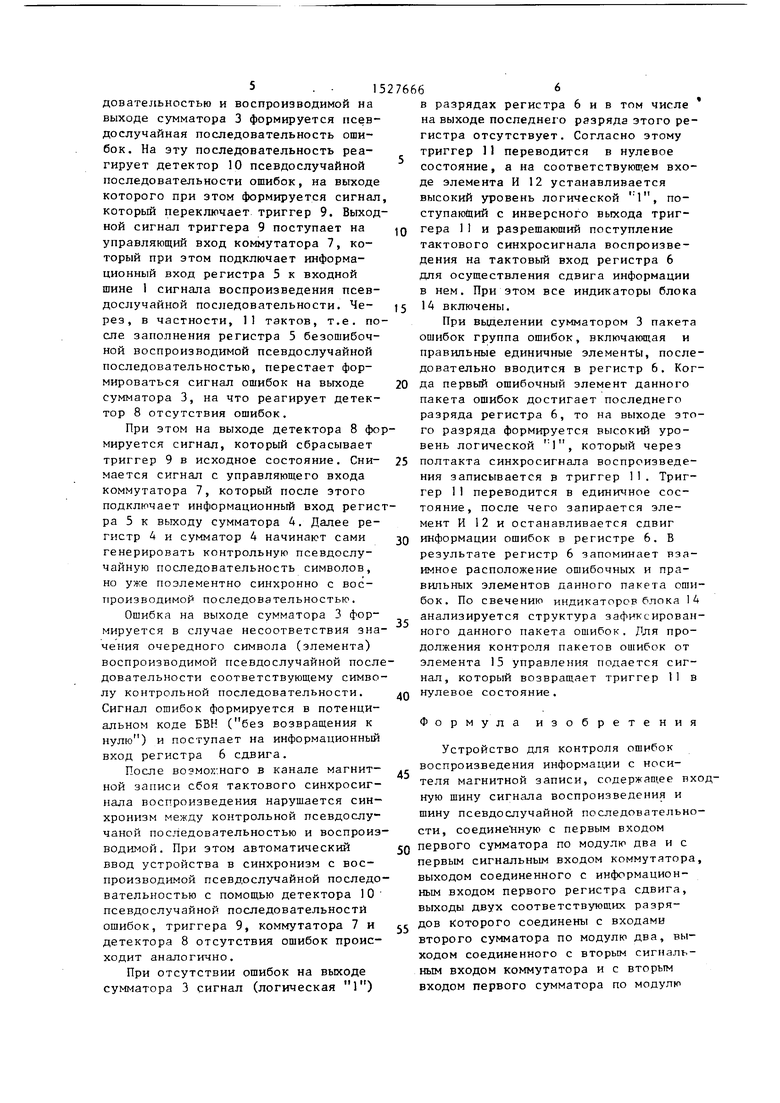

На чертеже представлена структурная схема устройства.

Устройство содержит входную шину 1 сигнала воспроизведения псевдослучайной последовательности импульсов (символов), входную шину 2 тактового синхросигнала воспроизведения, первый 3 и второй 4 сумматоры по модулю два, первый 5 и второй 6 регистры сдвига, коммутатор 7, детектор 8 отсутствия ошибок, триггер 9, детектор 10 псевдослучайной последовательности ошибок , дополнительньй триггер 11, эле- мент И 12, инвертор 13, блок 14 индикаторов и элемент 15 управления.

Входная шина 1 сигнала воспроизведения псевдослучайной последова- тельности соединен с первым входом сумматора 3 по модулю два и первым сигнальным входом коммутатора 7, выход которого соединен с информационным входом регистра 5 сдвига. Выходы девятого и одиннадцатого разрядов регистра 5 сдвига соединены с входами сумматора 4 по модулю два, выход которого соединен с вторым сигнальным входом комьгутатора 7 и вторым вхо- дом сумматора 3 по модулю два. Выход сумматора 3 соединен с информационным входом регистра 6 сдвига, информационным входом детектора 8 отсутствия ошибок и информационным входом детек- тора 10 псевдослучайной последовательности ошибок, выход которого соединен с первым, тактирующим входом триггера 8. Второй установочный в нулевое состояние вход триггера 9 сое- динен с выходом детектора 8 отсутствия ошибок, а выход - с управляющим входом коммутатора 7. Выходы всех раз рядов регистра 6 сдвига соединены с соответствующими индикаторами блока 14. Выход последнего разряда регистра 6 сдвига соединен, кроме того, с первым информащ1онным входом триггера 1 1 , ;пшерсньп1 выход которого соединен с первым входом элемента И 12 выход которого соединен с тактовым входом регистра 6 сдвига. Входная шина 2 тактового синхросигнала воспроизведения соединена с тактовым входом регистра 5 сдвига, входом тактового сигнала детектора 8 отсутствия ошибок, входом тактового сигнала детектора 10 псевдослучайной последовательности ошибок, вторым входом элемента И 12 и входом инвертора 13, выход которого соединен с вторым тактирующим входом триггера 11. Выход элемента 15 управления соединен с третьим установочным в нулевое состояние входом триггера 11.

Регистры 5 и 6 соответственно и 11- и 28-разрядные регистры сдвига.

Электронный коммутатор 7 соединяет информационный вход регистра 5 с входной шиной 1 сигнала воспроизведения псевдослучайной последовательности при наличии на управляющем входе коммутатора выходного сигнала триггера 9. При отсутствии этого сигнала коммутатор 7 соединяет информационный вход регистра 5 с выходом сумматора 4.

Устройство работает следующим образом.

Ко.гда информационный вход регистра 5 подключен посредством коммутатора 7 к выходу сумматора 4, то регистр 5 и сумматор 4 образуют генератор контрольной псевдослучайной последовательности символов, идетичный .генератору (не показан) , который формирует известным образом записываемую на магнитный носитель (не показан) испытательную псевдослучайную последовательность символов .

Ошибки воспроизведенного испытательного сигнала определяются путем поэлементного сравнения на сумматоре 3 воспроизводимой псевдослучайной последовательности символов с контрольной поспедовательностью.

В синхронизм с воспроизводимой псевдослучайной последовательностью генератор контрольной псевдослучайной последовательности автоматически вводится путем кратковременного подключения посредством электронного коммутатора 7 информационного входа регистра 5 к входной шине I.

При отсутствии сг нхронизма между контрольной псевдослучайной после5 . 15

довательностью и воспроизводимой на выходе сумматора 3 формируется псевдослучайная последовательность ошибок. На эту последовательность реагирует детектор 10 псевдослучайной последовательности ошибок, на выходе которого при этом формируется сигнал которьш переключает триггер 9. Выходной сигнал триггера 9 поступает на управляющий вход коммутатора 7, который при этом подключает информационный вход регистра 5 к входной шине 1 сигнала воспроизведения псевдослучайной последовательности. Через, в частности, 11 тактов, т.е. после заполнения регистра 5 безошибочной воспроизводимой псевдослучайной последовательностью, перестает формироваться сигнал ошибок на выходе сумматора 3, на что реагирует детектор 8 отсутствия ошибок.

При этом на выходе детектора 8 формируется сигнал, который сбрасывает триггер 9 в исходное состояние. Снимается сигнал с управляющего входа коммутатора 7, который после этого подключает информационный вход регистра 5 к выходу сумматора 4. Далее регистр 4 и сумматор А начинают сами генерировать контрольную псевдослучайную последовательность символов, но уже поэлементно синхронно с воспроизводимой последовательностью.

Ошибка на выходе сумматора 3 формируется в случае несоответствия значения очередного символа (элемента) воспроизводимой псевдослучайной последовательности соответствующему символу контрольной последовательности. Сигнал ошибок формируется в потенциальном коде БВН (без возвращения к нулю) и поступает на информационный вход регистра 6 сдвига.

После возмох .наго в канале магнитной записи сбоя тактового синхросигнала воспроизведения нарушается синхронизм между контрольной псевдослу чапой последовательностью и воспроизводимой. При этом автоматический ввод устройства в синхронизм с воспроизводимой псевдослучайной последовательностью с помощью детектора 10 псевдослучайной последовательности ошибок, триггера 9, коммутатора 7 и детектора 8 отсутствия ошибок происходит аналогично.

При отсутствии ошибок на выходе сумматора 3 сигнал (логическая 1)

66

в разрядах регистра бив том числе на выходе последнего разряда этого регистра отсутствует. Согласно этому триггер 11 переводится в нулевое состояние, а на соответствующем входе элемента И 12 устанавливается высокий уровень логической , поступающий с инверсного выхода триггера 11 и разрешающий поступление тактового синхросигнала воспроизведения на тактовый вход регистра 6 для осуществления сдвига информации в нем. При этом все индикаторы блока

14 включены.

При выделении сумматором 3 пакета ошибок группа ошибок, включающая и правильные единичные элементы, последовательно вводится в регистр 6. Когда первый ошибочный элемент данного пакета ошибок достигает последнего разряда регистра 6, то на выходе этого разряда формируется высокий уровень логической 1 , который через

полтакта синхросигнала воспроизведения записывается в триггер 11. Триггер 11 переводится в единичное состояние, после чего запирается элемент И 12 и останавливается сдвиг

информации ошибок в регистре 6. В результате регистр 6 запоминает взаимное расположение ошибочных и правильных элементов данного пакета ошибок. По свечению индикаторов блока 14 анализируется структура зафиксированного данного пакета ошибок. Лля продолжения контроля пакетов ошибок от элемента 15 управления подается сигнал, который возвращает триггер 11 в

нулевое состояние.

Формула изобретения

Устройство для контроля ошибок воспроизведения информации с носителя магнитной записи, содержащее входную шину сигнала воспроизведения и шину псевдослучайной последовательности, соедине нную с первым входом

первого сумматора по модулю два и с первым сигнальным входом коммутатора, выходом соединенного с информационным входом первого регистра сдвига, выходы двух соответствующих разрядов которого соединены с входами

второго сумматора по модулю два, выходом соединенного с вторым сигнальным входом коммутатора и с вторым входом первого сумматора по модулю

два вьтход которого соединен с информационным входом второго регистра сдвига и с информационньми входами детектора отсутствия ошибок и детектора псевдослучайной последовательности ошибок, к выходам которых подсоединен триггер, выходом соединенный с управляющим входом коммутатора, причем тактовый вход первого регистра сдвига соединен с входами тактового сигнала детектора отсутствия ошибок и детектора псевдослу- чаной последовательности ошибок и с входной шиной тактового синхросигнала воспроизведения, отличающееся тем, что, с целью повышения точности контроля ошибок за счет индикации структуры пакета оши

бок сигнала воспроизведения, в него введены дополнительный триггер, элемент И, выходом соединенный с тактовым входом второго регистра сдвига, блок индикаторов, подключенных к выходам разрядов второго регистра сдвига, выход последнего разряда которого при этом соединен также с первым входом дополнительного триггера, выходом соединенного с первым входом элемента И, инвертор, выход которого соединен с вторым входом дополнительного триггера, а вход - с вторым входом элемента И и с входной шиной тактового синхросигнала воспроизведения, и элемент управления, подключенньш к третьему входу дополнительного триггера.

Авторы

Даты

1989-12-07—Публикация

1988-02-17—Подача