Изобретение относится к приборостроению, а именно к технике магнитной записи, и может быть использовано в контрольно-измерительной аппаратуре и встроенных средствах контроля для контро- ля сбоев тактовой синхронизации при воспроизведении цифровой информации.

Цель изобретения - расширение диапазона контроля величины сдвига тактовой синхронизации.

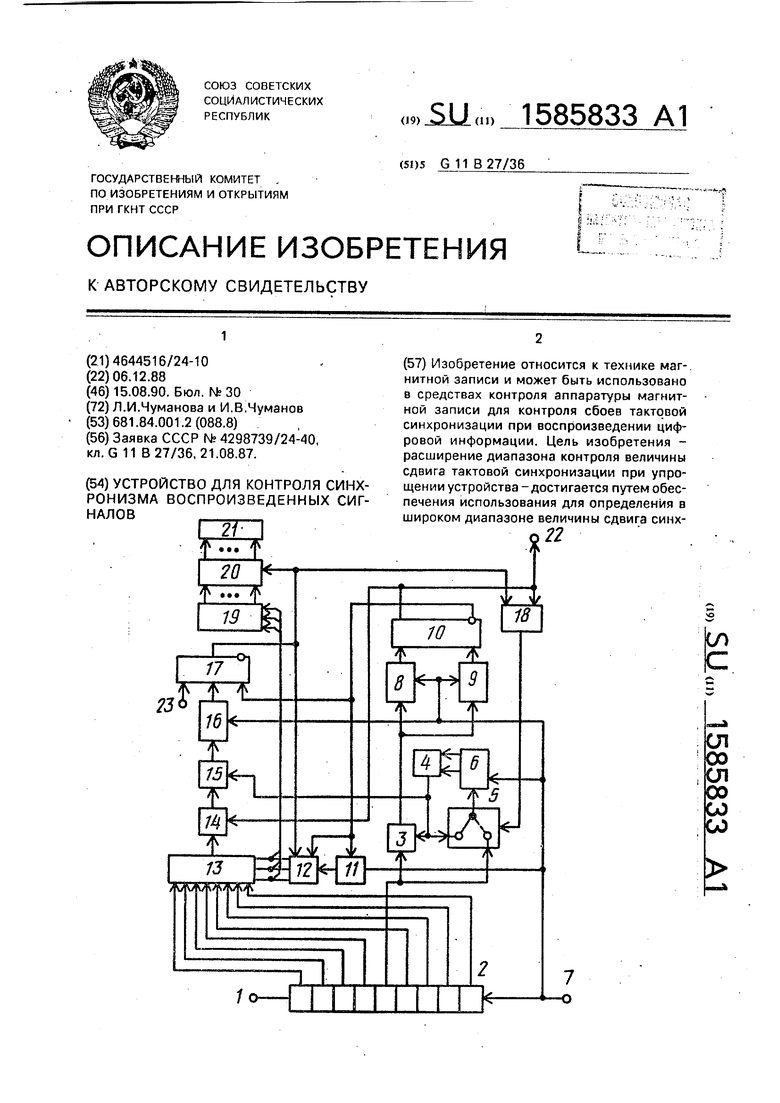

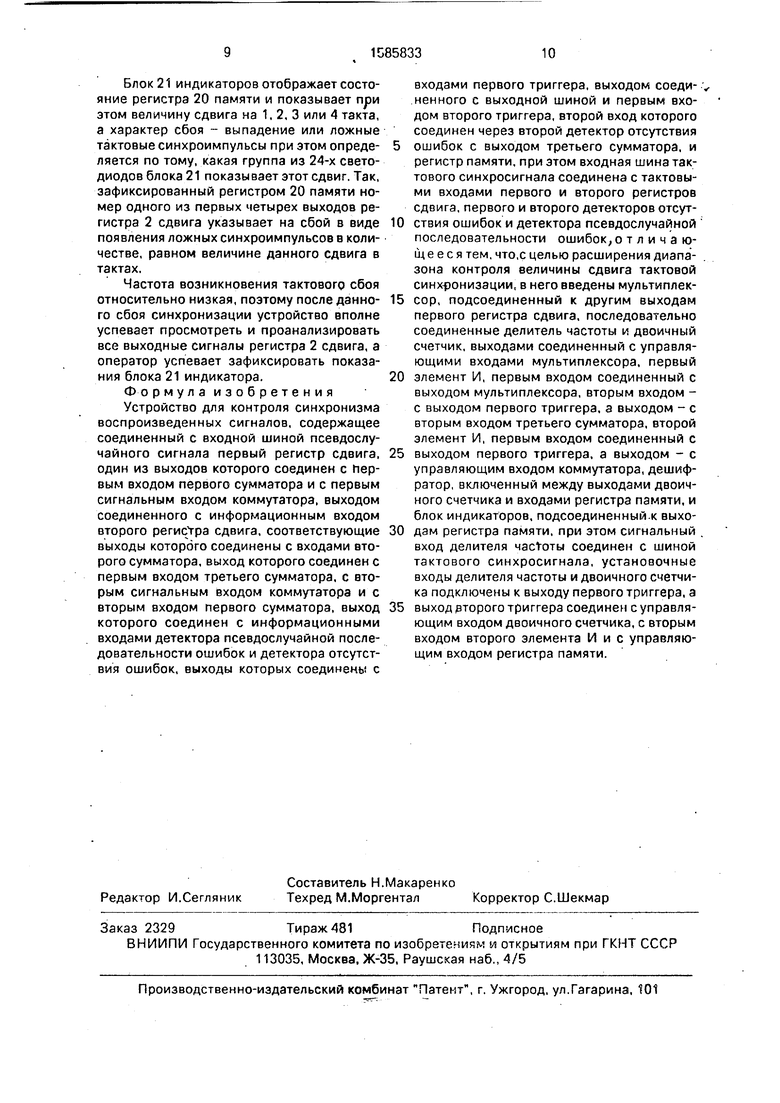

На чертеже изображена функциональная схема устройства (вариант для диапазона контроля сдвигов синхронизации до ± 4. такта).

Устройство для контроля сдвига (сбоя) синхронизации (проскальзывания) содержит входную шину 1 псевдослучайного сигнала воспроизведения, первый регистр 2 сдвига, первый 3 и второй 4 сумматоры по модулю два, электронный коммутатор 5, второй регистр б сдвига, входную шину 7 тактового синхросигнала воспроизведения, детектор 8 псевдослучайной последовательности ошибок, первый детектор 9 отсутствия ошибок, первый триггер 10, делитель 11 частоты, двоичный счетчик 12, мультиплексор 13, первый элемент И 14, третий сумматор 15 по мо,цулю два, второй детектор 16 отсутствия ошибок, второй триггер 17, второй элемент И 18. дешифратор 19, регистр 20 памяти, блок 21 индикаторов, выходную шину 22 сигнала рассогласования и шину 23 начальной установки.

Шина 1 соединена с информационным входом 9-разрядного регистра 2 сдвига, вы- ход пятого разряда которого соединен с первым входом сумматора 3 и с первым сигнальным входом коммутатора 5, выход

которого соединен с информационным входом регистра 6 сдвига, выходы двух разрядов которого, в частности, выходы 9-го и 11-го разрядов соединены с входами сумматора 4, выход которого соединен с первым входом сумматора 15, с вторым сигнальным входом коммутатора 5 и с вторым входом сумматора 3, выход которого соединен с информационными входами детектора 8 псевдослучайной последовательности ошибок и детектора 9 отсутствия ошибок, выходы которых соединены с входами триггера 10. Шина 7 соединена с тактовыми входами регистров 2 и 6 сдвига, детектора 8 псевдослучайной последовательности ошибок, детекторов 9 и 16 отсутствия о.шибок и с сигнальным входом делителя 11 частоты, выход которого соединен со счетным входом двоичного счетчика 12. Прямой выход триггера 10 соединен с выходной шиной 22, с вторым входом элемента И 14 и с первым входом элемента И 18, выход которого соединен с управляющим входом коммутатора 5. Выходы разрядов двоичного счетчика 12 соединены с входами дешифратора 19 и с управляющими входами мультиплексора 13, информационные входы которого подключены соответственно к выходам остальных восьми разрядов регистра 2 сдвига. Выход мультиплексора 13 соединен с первым входом элемента И 14, выход которого соединен с вторым входом сумматора 15, выход которого соединен с информационным входом детектора 16 отсутствия ошибок, выход которого соединен с вторым входом триггера 17. Инверсный выход триггера 10 соединен с устзнопочными в нулевое состояние входами делителя 11 частоты

и двоичного счетчика 12 и с первым входом триггера 17, выход которого соединен с BW рым входом элемента И 18, с входом остановки счета двоичного счетчика 12 м с входом управления параллельным вводом информации регистра 20 памяти, информационные входы которого подключены к выходам дешифратора 19, а выходы соединены с входами блока 21 индикаторов.

Регистр 2 сдвига - 9-разрядный

Электронный коммутатор 5 собран на основе логической схемы 2 И-2 ИЛИ, первые входы элементов И которой являются сигнальными входами коммутатора/ При этом второй оход одного элемента И соединен с управляющим входом коммутатора непосредственно, а второй вход другого элемента И - через инвертор.

Регистр 6 сдвига, в частности, - 11-разрядный и соответствует при этом разрядности кодообразующего регистра, тестовой псевдослучайной последовательности, поступающей на вход устройства.

Конкретное исполнение детектора 8 псевдослучайной последовательности и детекторов 9 и 16 отсутствия ошибок известно.

Блок 21 индикаторов состоит из восьми светодиодов.

. Устройство работает следующим образом.

На входные шины 1 и 7 подаются соответственно воспроизведенный цифровой сигнал и сопровождающий его тактовый синхросигнал с выходов контролируемого аппарата (или канала) цифровой магнитной записи - воспроиэведения.

Воспроизведенным сигналом является тестовая псевдослучайная последовательность символов, формирование которой перед записью производится известным образом с помощью, в частности. 11-разрядного регистра сдвига с отводами от 9-го и 11-го разрядов для организации логической обратной связи через сумматор по мо- дулю два. В соответствии с этим в устройстве использованы регистр 6 и сум- матор 4.

В первоначальный момент работы устройства синхронизма между поступающим по шине 1 и далее с выхода 5-го разряда регистра 2 сдвига входным цифровым сигналом и контрольным цифровым сигналом, формируемым регистром 6 сдвига и суммаором 4 (когда его выход замкнут с инфорационным входом регистра 6 через оммутатор 5), может не быть.

При отсутствии синхронизма, на входы умматора 3 поступают сигналы двух одинаовых псевдослучайных последовательно

стей, но сдвинутыедруг относительно друга. Согласно одному из свойств псевдослучайных последовательностей, на выходе сумматора 3 при этом будет формироваться также 5 псевдослучайная последовательность (ошибок), период которой и закон кодооб- разования соответствуют входной псевдослучайной последовательности. На эту последовательность ошибок реагирует де- 10 тектор 8 псевдослучайной последовательности, на выходе которого при этом формируется сигнал в виде высокого уровня напряжения, от которого переключается триггер 10.

15Первоначально режим ввода устройства в синхронизм с входным цифровым сигналом включается подачей разовой импульсной команды от кнопки (на чертеже не показана) по шине 23 на третий (второй 20 установочный) вход триггера 17, который при этом переключается в единичное состояние и открывает элемент И 18. Одновременно может производиться начальная установка этой же командой и регистра 20 25 памяти в нулевое состояние (эта связь на чертеже не показана).

Выходной сигнал триггера 10 проходит через элемент И 18 на управляющий вход коммутатора 5. При наличии этого сигнала, 30 коммутатор 5 соединяет информационный вход регистра 6 сдвига с выходом пятого разряда регистра 2 сдвига.

Начинается ввод в синхронизм формирователя контрольного сигнала - регистра 6 5 и сумматора 4 с поступающим цифровым сигналом. После записи в регистр 6 безошибочных символов входного цифрового сигнала в количестве не менее, чем число разрядов этого регистра, перестают форми- 0 роваться ошибки на выходе сумматора 3.

На выходе этого сумматора устанавливается постоянный низкий уровень, что фиксирует детектор 9 отсутствия ошибок. На выходе детектора 9 формируется сигнал, ко- 5 торый сбрасывает триггер 10 в исходное состояние.

Убирается сигнал - команда на управляющем входе коммутатора 5, после чего ин- - формационный вход регистра б сдвига 0 соединяется с выходом сумматора 4, Ввод в синхронизм закончился.

После этого регистр б с сумматором 4 начинает сам генерировать контрольный цифровой сигнал - псевдослучайную после- 5 довательность поэлементно синхронно с входным цифровым сигналом.

Сигнал (потенциал) с инверсното. выхода триггера 10 сбрасывает в ИСХОДНОЙ, нулевое состояние триггер 17 и устанавли аает в нулевое состояние и блокирует в-этом состоянии делитель 11 частоты и двоичный счетчик 12. Эломеят; I 14 и 18 заперты.

Продвижение информации в pei /:CTpax 2 и 6 и функционирование детектор01з 9 м 16 отсутствия ошибок и детектора 8 псевдослучайной последовательности обеспечивается входным тактовым синхросигналом воспроизведения.

Устройство предназначено для контроля сбоев выходного тактового синхросигнала аппарата магнитной записи (для оценки данного параметра) или канала цифровой магнитной записи - воспроизведения (при отработке канала), когда между выходом канала и выходом аппарата стоит дополнительное инерционное звено формирования выходного синхросигнала из состава системы обнаружения и исправления ошибок.

Нарушение синхронизма между входным цифровым сигналом воспроизведения ы его тактовым синхросигналом в устройстве контролируется путем контроля нарушения синхронизма между входным цифровым сигналом и контрольным цифровым сигналом, генерируемым устройством.

При синхронизме входного цифрового сигнала с контрольным сигналом ошибок на выходе сумматора 3 отсутствуют ли(5о фор- / ируются сигналы одиночных или групповых символьных ошибок, присутствующих в воспроизведенной информации. Детектор 8 псевдослучайной последовательности ошибок на эти сигналы не реагирует.

Уменьи ение или увеличение числа тактовых импульсов вызывает нарушение синхронизма между входным и контрольным сигналами вследствие сдвига входной информационной последовательности(про- скальзывание цифрового сигнала воспроизведения) влево или вправо на временной оси, т.е. относительно среднего вывода (выхода пятого разряда) регистра 2 сдеига и, следовательно, относительно контрольной последовательности, генерируемой регистром б и сумматором А. Величина сдвига определяется количеством пыпав- ших или ложных, тактовых импульсов.

Для определения величины сдвига (проскальзывания) меж,цу сигналами служит регистр 2 сдвига, имеющий по четыре отвода влеоо и вправо относительно среднего, пятого выхода, к которому подключена схема определения нарушения синхронизма, включающая о себя генератор контрольного сигнала (сумматор А. регистр 6 и коммутатор 5), сумматор 3, детектор В псевдослучайной последовательности ошибок, детектор 9 отсутствия ошибок и триггер 10.

Осг;ь 1ьныа выходы регистра 2 сдвига соединены через мультиппексор 13 и элемент

И 14 с входом схемы фиксации величины сдвига, включающей в себя сумматор 15, детектор 16 отсутствия ошибок и триггер 17.

При выпадении подряд одного.или нескольких тактовых синхроимпульсов, либо при возникновении подряд одного или нескольких ложных тактовых синхроимпульсов., входная информация соответственно

записывается с задержкой (выпадают символы) на один или несколько тактов в пер- разряд регистра 2, либо записывается с двухкратным или большим повторением значения одного из битов. В этом случае

формируется псевдослучайная последовательность ошибок на выходе сумматора 3, на что реагирует детектор 8 псевдослучайной последовательности, выходной сигнал которого при этом переключает триггер 10.

Сигнал с прямого выхода триггера 10

поступает на выходную шину 22 устройства для подсчета данного тактового сбоя и открывает элементы И 14 и 18.

Отсутствие сигнала на инверсном выходе триггера 10 при этом означает снятие блокировки с делителя 11 частоты, двоичного счетчика 12 и триггера 17.

Сдвиг входной информации на один или несколько тактов означает, что сигнал на

одном из остальных - 1, 2, 3, 4, 6, 7, 8 или 9-ом выходах регистра 2 совпадает поэлементно с контрольным сигналом, поступающим на второй вход сумматора 15. Для определения (отыскания) этого выхода

мультиплексор 13 начинает поочередно подключать выходы регистра 2 через открытый элемент И 14 к входу сумматора 15.

Периодичность смены адресов входов мультиплексора 13, задаваемых счетчиком

12, определяется делителем 11, который делит тактовую частоту, в частности, в 256 раз, т.е. анализ каждого выхода регистра 2 производится схемой фиксации данной величины сдвига в течение 256-ти тактов.

При появлении на выходе мультиплексора 13 сигнала, совпадающего поэлементно с контрольным, перестают формироваться ошибки на выходе суммато ра 15, на что реагирует детектор 16 отсутстВИЯ ошибок. Выходной сигнал детектора 16 переключает триггер 17, выходной сигнал которого при этом останавливает счет двоичного счетчика 12, производит запись данного номера (адреса) входа мультиплексора

13 (или, что то же, номера выхода регистра 2), дешифрированного дешифратором. 19, в регистр 20 памяти и проходит через элемент И 18 на управляющий вход коммутатора 5 для включения режима ввода устройства в синхронизм.

Блок 21 индикаторов отображает состояние регистра 20 памяти и показывает при этом величину сдвига на 1, 2, 3 или 4 такта, а характер сбоя - выпадение или ложные тактовые синхроимпульсы при этом опреде- ляется по тому, какая группа из 24-х свето- диодов блока 21 показывает этот сдвиг. Так, зафиксированный регистром 20 памяти номер одного из первых четырех выходов регистра 2 сдвига указывает на сбой в виде появления ложных синхроимпульсов в количестве, равном величине данного сдвига в тактах.

Частота возникновения тактового сбоя относительно низкая, поэтому после данно- го сбоя синхронизации устройство вполне успевает просмотреть и проанализировать все выходные сигналы регистра 2 сдвига, а оператор успевает зафиксировать показания блока 21 индикатора.

Формула изобретения

Устройство для контроля синхронизма воспроизведенных сигналов, содержащее соединенный с входной шиной псевдослучайного сигнала первый регистр сдвига, один из выходов которого соединен с hep- вым входом первого сумматора и с первым сигнальным входом коммутатора, выходом соединенного с информационным входом второго регис тра сдвига, соответствующие выходы которого соединены с входами второго сумматора, выход которого соединен с первым входом третьего сумматора, с вторым сигнальным входом коммутатора и с вторым входом первого сумматора, выход которого соединен с информационными входами детектора псевдослучайной последовательности ошибок и детектора отсутствия ошибок, выходы которых соединены с

входами первого триггера, выходом соединенного с выходной шиной и первым входом второго триггера, второй вход которого соединен через второй детектор отсутствия ошибок с выходом третьего сумматора, и регистр памяти, при этом входная шина тактового синхросигнала соединена с тактовыми входами первого и второго регистров сдвига, первого и второго детекторов отсутствия ошибок и детектора псевдослучайной последовательности ошибок, о т л и ч а ю- U4 е е с я тем, что,с целью расширения диапазона контроля величины сдвига тактовой cинxf)oнизaции, в него введены мультиплексор, подсоединенный к другим выходам первого регистра сдвига, последовательно соединенные делитель частоты и двоичный счетчик, выходами соединенный с управляющими входами мультиплексора, первый элемент И, первым входом соединенный с выходом мультиплексора, вторым входом - с выходом первого триггера, а выходом - с вторым входом третьего сумматора, второй элемент И, первым входом соединенный с выходом первого триггера, а выходом - с управляющим входом коммутатора, дешифратор, включенный между выходами двоичного счетчика и входами регистра памяти, и блок индикаторов, подсоединенный.к выходам регистра памяти, при этом сигнальный вход делителя чactoты соединен с шиной тактового синхросигнала, установочные входы делителя частоты и двоичного счетчика подключены к выходу первого триггера, а выход дторого триггера соединен с управляющим входом двоичного счетчика, с вторым входом второго элемента И и с управляющим входом регистра памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля ошибок магнитной записи-воспроизведения цифровой информации | 1985 |

|

SU1273994A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1985 |

|

SU1256092A1 |

| Устройство для контроля ошибок воспроизведения информации с носителя магнитной записи | 1988 |

|

SU1527666A1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| Устройство диагностического контроля аппаратуры цифровой магнитной записи | 1987 |

|

SU1478253A1 |

| Устройство для контроля ошибок многоканального аппарата магнитной записи | 1987 |

|

SU1432604A1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для контроля каналов записи аппарата магнитной записи | 1986 |

|

SU1411818A1 |

| Способ синхронной передачи дискретной информации в волоконно-оптических системах связи | 1989 |

|

SU1688430A1 |

| Устройство синхронизации источников сейсмических сигналов | 1991 |

|

SU1787278A3 |

Изобретение относится к технике магнитной записи и может быть использовано в средствах контроля аппаратуры магнитной записи для контроля сбоев тактовой синхронизации при воспроизведении цифровой информации. Цель изобретения - расширение диапазона контроля величины сдвига тактовой синхронизации при упрощении устройства - достигается путем обеспечения использования для определения в широком диапазоне величины сдвига синхронизации только одной анализирующей схемы фиксирования величины сдвига, состоящей из сумматора 15, детектора 16 отсутствия ошибок и триггера 17. После ввода устройства в синхронизм с воспроизводимым сигналом регистр 6 и сумматор 4 продолжают сами формировать контрольную псевдослучайную последовательность, синхронную с входной. Сбой синхросигнала приводит к появлению на выходе сумматора 3 псевдослучайной последовательности ошибок, на что реагирует детектор 8 и переключает триггер 10. Выходные сигналы триггера 10 открывают элементы И 14, 18 и снимают блокировку с делителя 11, счетчика 12 и триггера 17. Для определения величины данного сдвига мультиплексор 13 начинает поочередно подключать вход схемы фиксирования величины сдвига к выходам регистра 2. При поступлении на выход элемента И 14 псевдослучайной последовательности, поэлементно синхронной с контрольной, на выходе сумматора 15 перестает формироваться сигнал ошибок, на что реагирует детектор 16 и переключает триггер 17. Выходной сигнал триггера 17 останавливает счетчик 12 и записывает в регистр 20 номер данного выхода регистра 2, указывающий на величину сдвига и характер сбоя - выпадение или ложные синхроимпульсы, а также проходит через элемент И 18 на управляющий вход коммутатора 5 для включения режима повторного ввода устройства в синхронизм с воспроизводимым сигналом.

| Заявка СССР № 4298739/24-40, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1990-08-15—Публикация

1988-12-06—Подача