Изобретение относится к приборостроению, а именно к технике магнитной записи, и может быть использовано в отдельной аппаратуре контроля для исследования структуры групповых ошибок канала цифровой магнитной записи- воспроизведения о

Целью изобретения является повышение точности контроля путем расшире- ния диапазона индикации структуры пакетов ошибок сигнала воспроизведения о

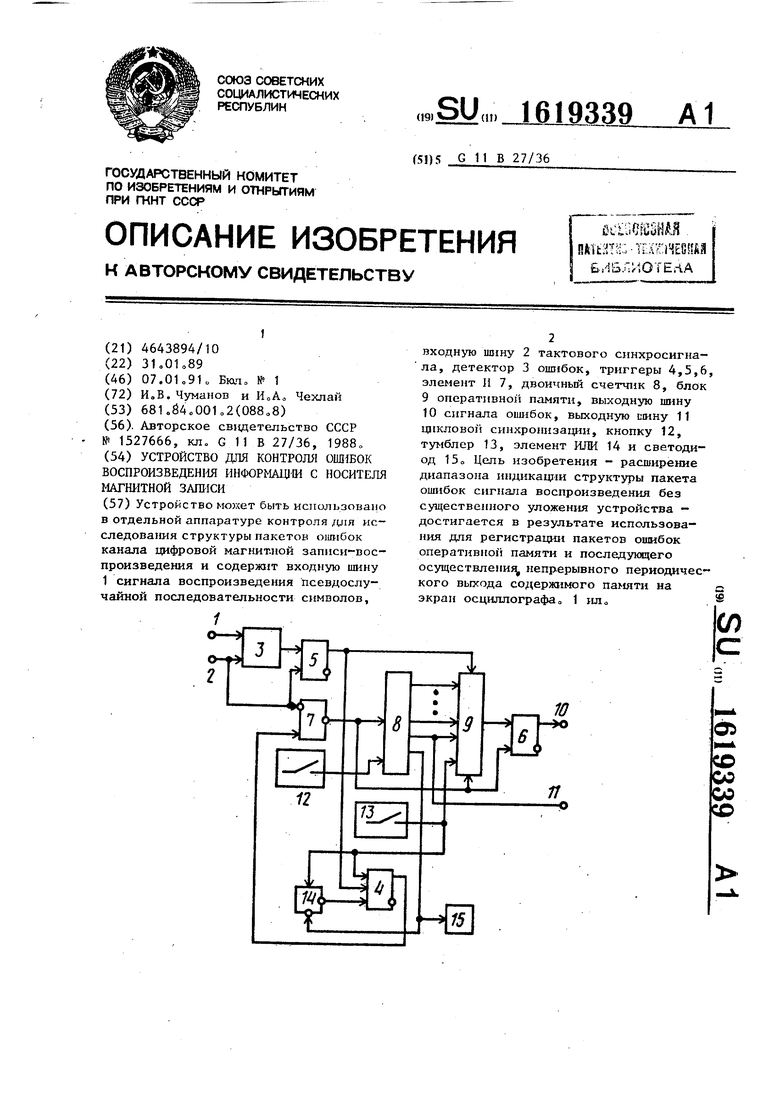

На чертеже представлена схема предлагаемого устройствао

Устройство содержит входную шину 1 сигнала воспроизведения тестовой псевдослучайной последовательности (символов), входную шину 2 тактового синхросигнала воспроизведения, детектор 3 ошибок, триггеры 4-6, элемент И 7, счетчик 8, блок 9 оперативной памяти (ОЗУ), выходную шину 10 сигнала ошибок, выходную шину 11 сигнала (цикловой) синхронизации, элементы

12и 1-3 управления, элемент ИЛИ 14 и индикатор 15

Входная шина 1 сигнала воспроизведения псевдослучайной последовательности соединена с информационным входом детектора 3 ошибок, выход ко- торого соединен с информационным входом D-триггера 5, выход которого сое- ,динен с тактирующим входом С триггера 4 и с информационным входом блока 9 оперативной памяти Выход разрядов (кроме последнего) счетчика 8 соединен с адресными входами блока 9 оперативной памяти, выход которого соединен с информационным входом D триггера 6 о Выход последнего соединен с выходной шиной 10 сигнала ошиЬокс Инверсный выход элемента И 7 соединен с тактирующим входом С триггера 6, с входом блокировки блока 9 оперативной памяти и со счетным входом счетчика 8 выход предпоследнего разряда которого соединен дополнительно с выходной шиной 11 синхронизациио Выход элемента

13управления соединен с входом управления записью/считыванием блока 9, с первым входом элемента ИЛИ 14 и с установочным в единичное состояние входом триггера 4, выход которого соединен с первым входом элемента И 7 о Выход элемента 12 соединен с устано- вочным в нулевое состояние входом двоичного счетчика 8, выход последнег разряда которого соединен с индикатором 15 и с вторым инверсным входом

элемента ИЛИ 14, инверсный выход которого соединен с установочным в нулевое состояние входом триггера 4„ Входная шина 2 соединена с тактовым входом детектора 3 ошибок, с тактирующим входом триггера 5 и с вторым инверсным входом элемента И 7„ На четвертый информационный вход D триггера 4 постоянно подан высокий уровень напряжения логической 1 (связь не показана).

Устройство предназначено для запоминания структуры данного пакета ошибок с обеспечением последующей индикации ее на экране осциллографа и работает следующим образом0

После последнего приема и запоминания блоком 9 пакета ошибок на выходе последнего 11-го разряда двоичного счетчика 8 устанавливается высокий уровень напряжения, который проходит через элемент ИЛИ 14 и сбрасывает в нулевое состояние триггер 40 Запирается элемент И 7, на выходе которого при этом остается высокий уровень напряжения, который блокирует блок 9 оперативной памяти„

Для приема нового пакета ошибок (со стиранием в памяти блока 9 устройства ошибок предыдущего пакета) сигналом от кнопки 12 устанавливают счетчик 8 в нулевое состояниес При этом тумблер 13 должен находиться в состоянии, при котором сигнал на его выходе отсутствует, что соответствует режиму запоминания (приема) ошибок, выделенных детектором Зс

При появлении в воспроизводимой псевдослучайной последовательности ошибок на выходе детектора 3 формируется сигнал, который по положительным фронтам тактового синхросигнала воспроизведения перезаписывается в триггер 5 о

Первый (в данной серии ошибок) положительный перепад уровней сигнала ошибок на выходе триггера 5 переключает триггер 4 в единичное состояние о На его выходе устанавливается высокий уровень напряжения, который открывает элемент И 7 для прохождения (без инвертирования) тактового синхросигнала на счетный вход двоичного счетчика 6, блокирующий вход блока 9 оперативной памяти и тактирующий вход триггера 6, Состояние выхода элемента И 7 - высокий уровень напряжения, т„е в данной положительной полуволне так

5161

тового сигнала состояние не изменилось

Запись сигналов ошибок в блок 9 оперативной памяти производится в моменты отрицательных перепадов уровней тактового сигнала на его блокирующем входе после установки соответствующего адреса однобитовой ячейки памяти блока 9 о Адрес устанавливается после переключения счетчика 8 положительным фронтом тактового синхросигнала,, При этом получается так, что смена адресов на соответствующих входах блока 9 происходит практически уже во время его блокировкио

Таким образом, отрицательным перепадом тактового синхросигнала в середине тактовой позиции сигнал первой ошибки данного пакета ошибок записывается в ячейку памяти блока 9 с нулевым адресом

Одновременно с записью в триггер 5 значения сигнала второй тактовой позиции -данного пакета ошибок положи- тельным фронтом тактового синхросигнала переключается счетчик 8.F этот же момент поступает высокий уровень напряжения (первая половина тактовой позиции) на блокирукшдш вход блока 9 оперативной памяти Отрицательным перепадом тактового синхросигнала и середине второй тактовой позиции данного пакета ошибок в блок 9 записываетс значение этой позиции в ячейку памяти с первым адресом 0001 и т„д. ,

Блок 9 на микросхеме 132РУ4 обеспечивает запоминание структуры пакета ошибок протяженностью до 1024 бит,

Через 1024 такта на выходе последнего 11-го разряда двоичного счетчика 8 устанавливается высокий уровень напряжения, который включает светодиод 15, а также проходит через элемент ИЛИ 14 и сбрасывает в нулевое состояние триггер 4, в результате чего запирается элемент И 7„

Свечение индикатора 15 при этом

свидетельствует о том, что устройство приняло и запомнило данный пакет оши- бок, выделенных детектором 3„

Далее тумблером 13 включается режим просмотра структуры принятого потока ошибоко

1 Для индикации зарегистрированного устройством пакета ошибок необходимо , использовать стандартный электронный осциллограф, который подключается к выходной шине 10 сигнала ошибок и ис

0

5

0

5

пользуется в режиме внешней синхронизации Вход внешней синхронизации осциллографа при этом подключается к выходной шине 11 цикловой синхронизации о

При подаче тумблером 13 сигнала, блок 9 оперативной памяти переводится в режим считывания, а триггер 4 устанавливается в единичное состояние„ Элемент ИЛИ 14 при этом блокирует действие выходного сигнала последнего разряда счетчика 8 на триггер 4 Открывается элемент И 7, и тактовый синхросигнал поступает постоянно на счетный вход довичного счетчика 8 для обеспечения последовательного переключения адресов ячеек памяти блока 9, на вход блокировки блока 9 оперативной памяти и на тактирующий вход выходного триггера 6 для перезаписи в него содержимого ячеек памяти блока 9о При ттом происходит последовательный вывод (с тактовой частотой синхросигнала воспроизведения) на выходную шину 10 устройства содержимого 1024 ячеек памяти блока 9, Циклы вывода периодически повторяются через 1024 такта„ Дня синхронизации выходного сигнала по циклям, т,еа по началу пачки ошибок, используется выходной сигнал предпоследнего разряда двоичного счетчи- к я 8 о

После окончания анализа структуры данного пакета ошибок включают режим записи информации в блок 9 оперативной памяти тумблером 13 и обнуляют счетчик 8 кнопкой 12„

Формула изобретения

Устройство для контроля ошибок вое произведения информации с носителя магнитной записи, содержащее детектор ошибок, входами связанный с входными шинами сигнала воспроизведения псев- дослучайнон последовательности и тактового синхросигнала воспроизведения эа выходом - с единичным входом первого триггера,последовательно соединенные второй триггер и элемент И, другой вход которого подключен к входной шине тактового синхросигнала воспроизведения, элемент управления, выход которого соединен с установочным входом второго триггера, и индикатор, отличающееся тем, что, с целью повышения точности контроля пу-

тем расширения диапазона индикации структуры ошибок сигнала воспроизведения, в него введен блок оперативной памяти, установочным входом соединенный с выходом1 элемента управления, счетчик счетным входом соединен с инверсным выходом элемента И, а выходами - с адресными входами блока опе ративной памяти, подключенного ин- J формационным входом к выходу первого триггера и первому входу второго триггера, дополнительный элемент управления, выходом соединенный с управляющим входом счетчика, третий триггер, 1 первым входом подключенный к выходу блока оперативной памяти, вторым входом - к инвертирующему выходу элемента И и входу блокировки блока оперативной памяти, а выходом - к выходной шине сигнала ошибок, при этом выход последнего свободного разряда счетчй- ка соединен с входом индикатора и инвертирующим входом элемента ИЛИ, другой вход которого соединен с элементом управления, а выход подключен к второму входу второго триггера, выход предпоследнего разряда счетчика соединен с выходной шиной синхронизации, а входная шина тактового синхросигнала воспроизведения подключена к другому входу первого триггера,,

Устройство может быть использовано в отдельной аппаратуре контроля для исследования структуры пакетов ошибок канала цифровой магнитной записи-воспроизведения и содержит входную шину 1 сигнала воспроизведения псевдослучайной последовательности символов, / входную шину 2 тактового синхросигнала, детектор 3 ошибок, триггеры 4,5,6, элемент И 7, двоичный счетчик 8, блок 9оперативной памяти, выходную шину 10сигнала ошибок, выходную пину 11 цикловой синхронизации, кнопку 12, тумблер 13, элемент ИЛИ 14 и светоди- од 15 о Цель изобретения - расширение диапазона индикации структуры пакета ошибок сигнала воспроизведения без существенного уложения устройства - достигается в результате использования для регистрации пакетов ошибок оперативной памяти и последующего осуществления непрерывного периодического выхода содержимого памяти на экран осциллографа о 1 ило SS (Л

| Устройство для контроля ошибок воспроизведения информации с носителя магнитной записи | 1988 |

|

SU1527666A1 |

Авторы

Даты

1991-01-07—Публикация

1989-01-31—Подача