ел to

со

4

О5

со

Изобретение относится к телевидению и может быть использовано в пере- дакяцих телевизионных (ТВ) камерах, выполненных в виде сборки линейных - фоточувствительных схем с зарядовой связью (ЛФСЗС), пррднязначенных дпя передачи графической и текстовой информации .

Цель изобретения - уменьшение ю времени формирования видеосигнала и повышение его точности.

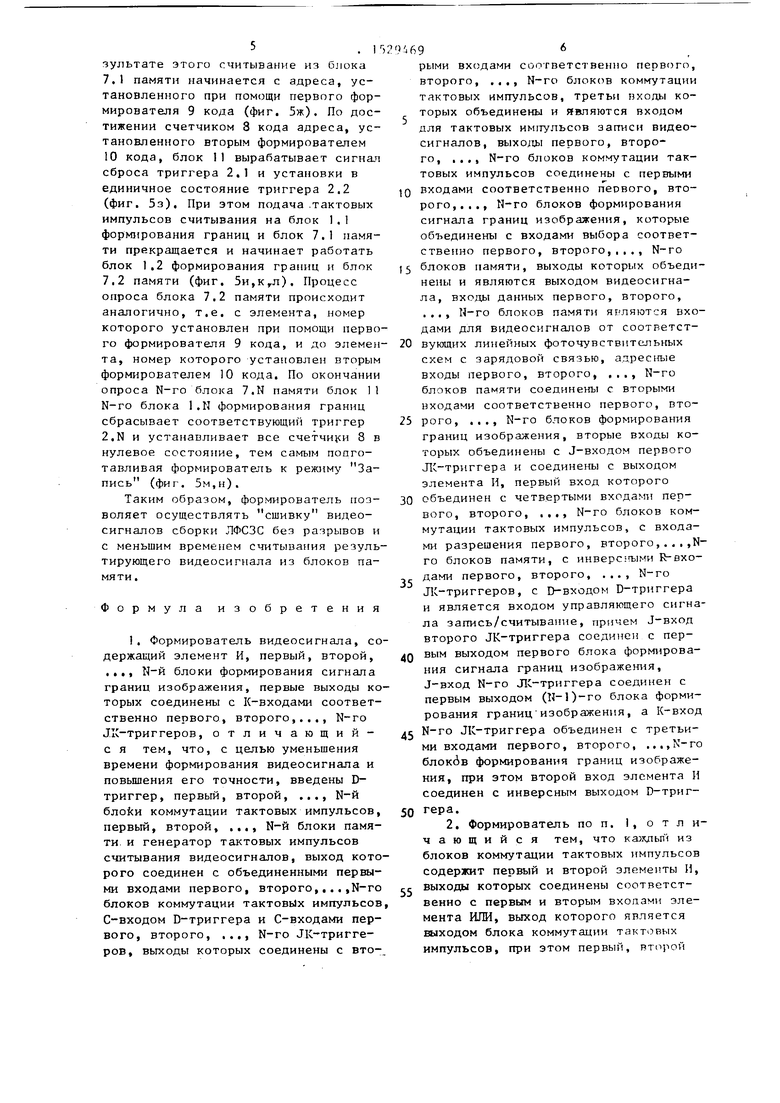

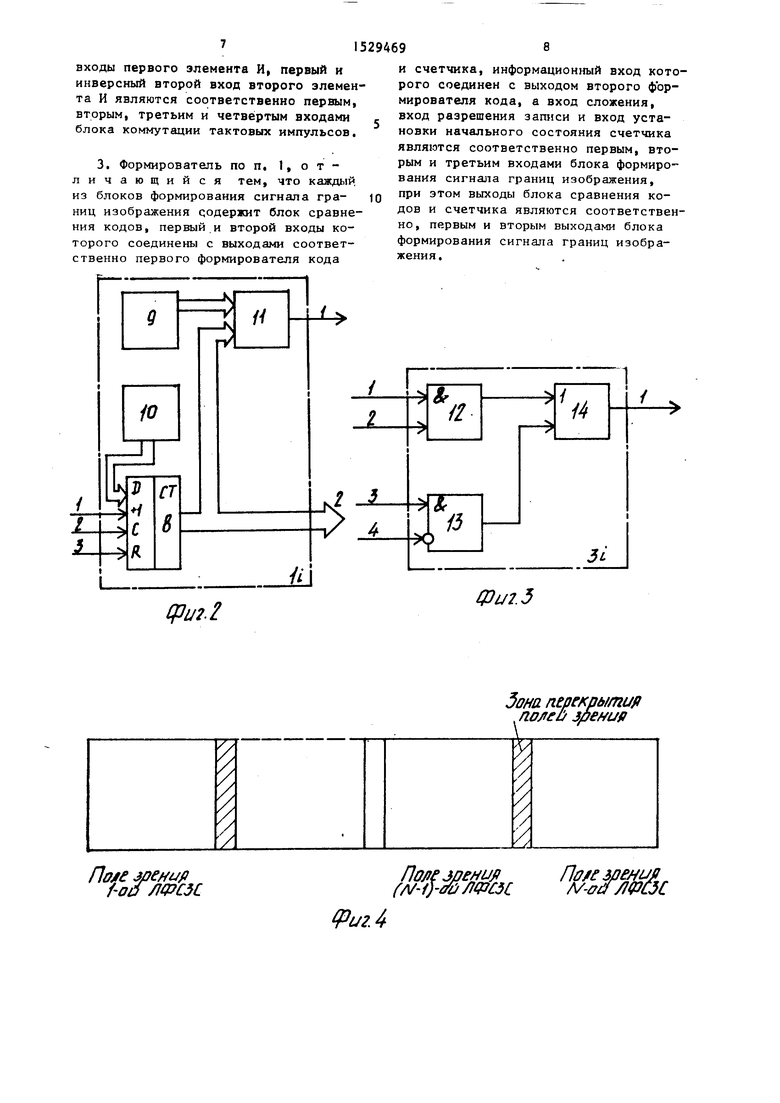

На фиг, 1 представлена структурная электрическая схема формировате- пя; на фиг, 2 - структурная электри- 15 ческая схема одного из блоков формирования границ изображения; на фиг,3- то же, одного из блоков коммутации тактовых импульсов ; на фиг, 4 - возможный вариант тест-изображения; 20 на фиг. 5 - временные диаграммы, поясняющие работу формирователя.

Формирователь (фиг, 1) содержит первый, второй,,,,,Н-й блоки 1,1, 1,2,,,,,1,N формирования границ 25 изображения, первый, .второй,,,,,N-й триггеры 21,22,,,,,2N, первый, второй, ,,,,К-й блоки 3,1, 3,2,,,,,3,N коммутации тактовых импульсов, генератор 4 тактовых импульсов считыва- ЗО ния видеосигналов,D-триггер 5, элемент И 6 и первый, второй, ,,,, N-й блоки 7,1, 7,2,,,,,7,N памяти,

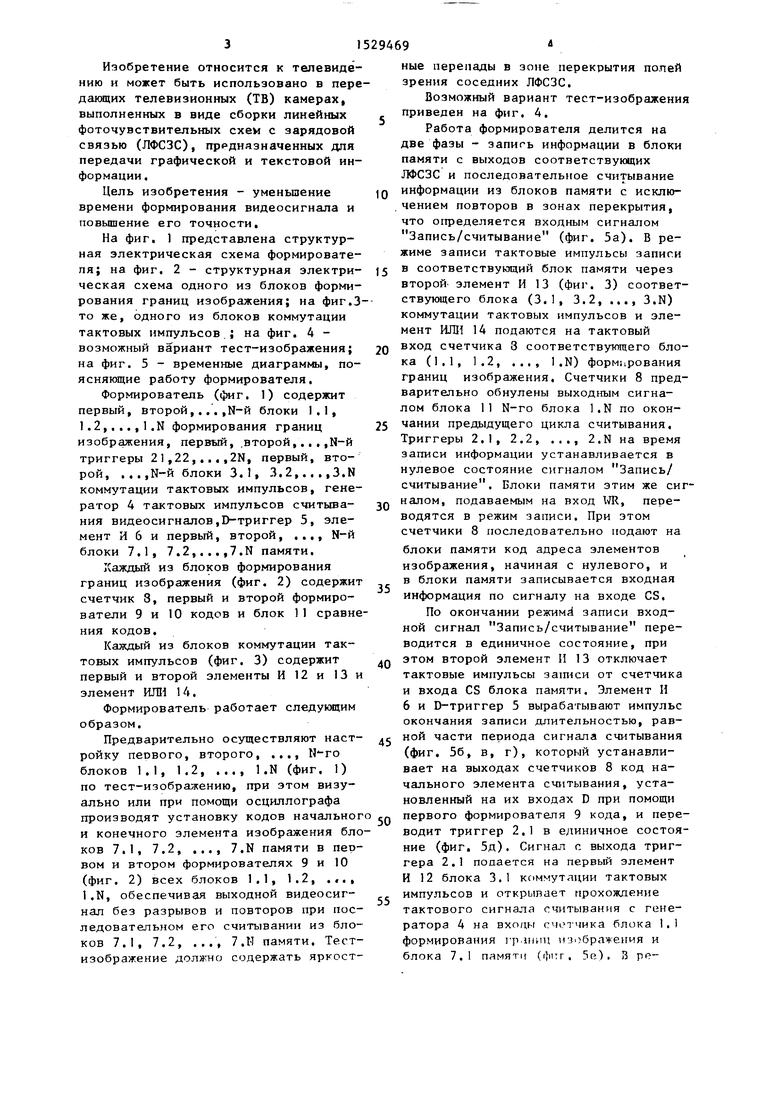

Каждый из блоков формирования границ изображения (фиг, 2) содержит счетчик 8, первый и второй формирователи 9 и 10 кодов и блок 11 сравнения кодов.

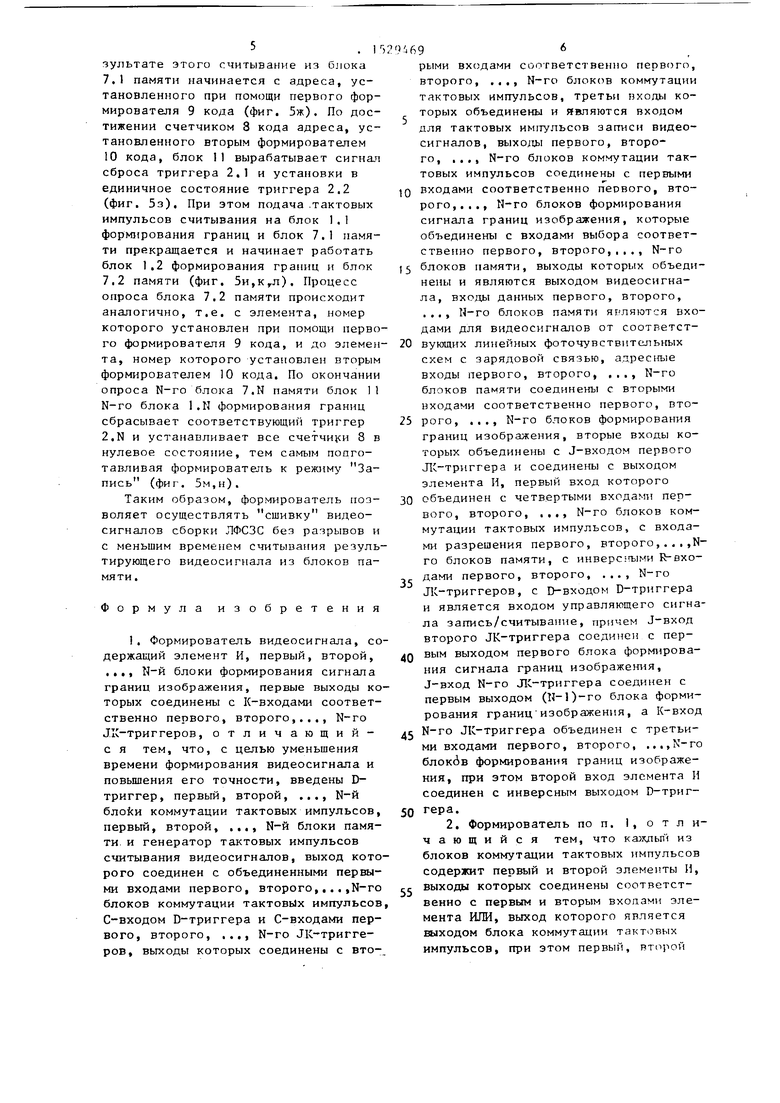

Каждый из блоков коммутации тактовых импульсов (фиг, 3) содержит первый и второй элементы И 12 и 13 и элемент ИЛИ 14,

Формирователь работает следующим образом.

Предварительно осуществляют наст- д ройку пеового, второго, ,,,, NTO блоков 1,1, 1,2, ,,,, 1,N (фиг, 1) по тест-изображению, при этом визуально или при помощи осциллографа

35

40

производят установку кодов начального ,« первого формирователя 9 кода

и конечного элемента изображения блоков 7,1, 7,2, ,,,, 7,N памяти в первом и втором формирователях 9 и 10 (фиг, 2) всех блоков 1,1, 1,2, ,«,,

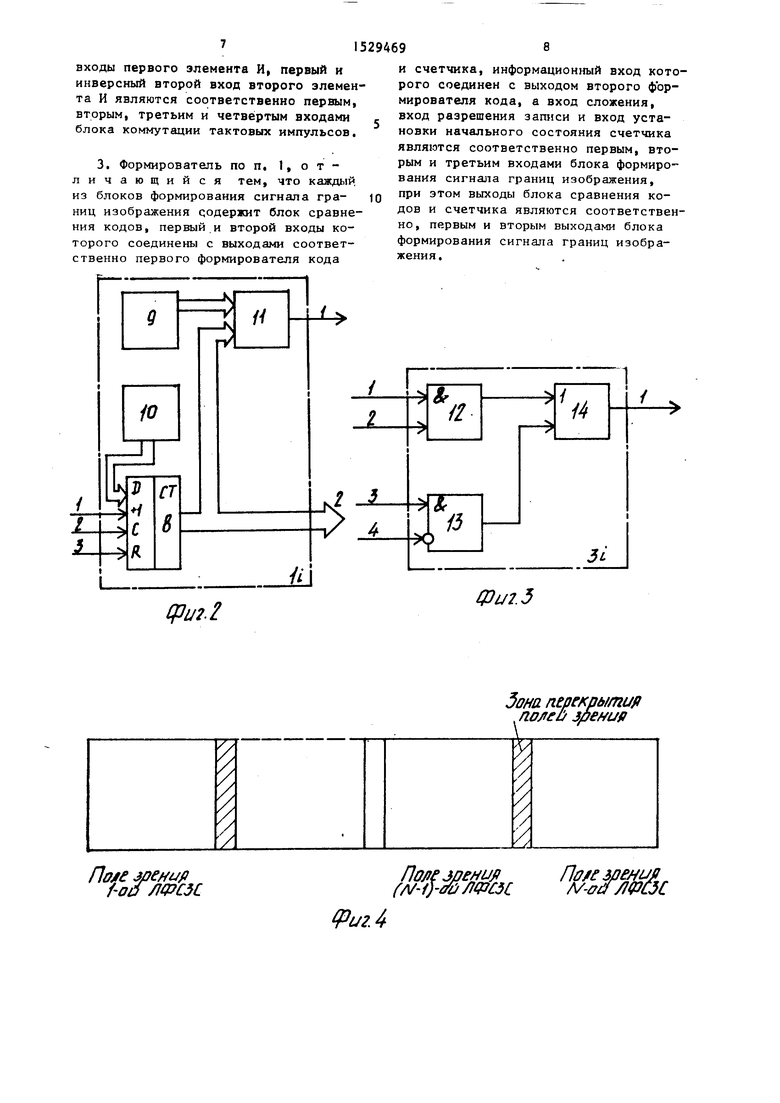

1,N, обеспечивая выходной видеосигнал без разрывов и повторов при последовательном его считывании из блоков 7,1, 7,2, ,,,, 7,М памяти. Тест- изображение должно содержать яркост55

ные перепады в зоне перекрыт зрения соседних ЛФСЗС,

Возможный вариант тест-из приведен на фиг, 4,

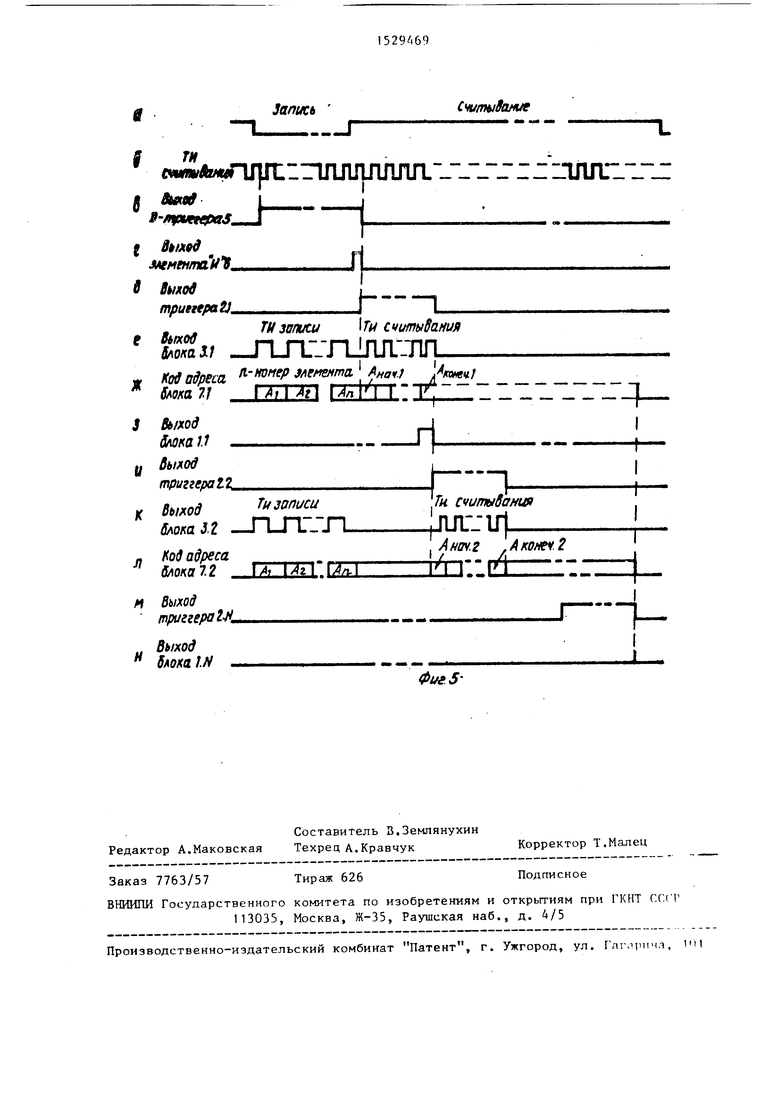

Работа формирователя дели две фазы - запить информации памяти с выходов соответствую ЛФСЗС и последовательное счит информации из блоков памяти чением повторов в зонах перек что определяется входным сиг Запись/считывание (фиг, 5а жиме записи тактовые импульсы в соответствующий блок памяти второй элемент И 13 (фиг, 3) ствующего блока (3,1, 3,2, ,, коммутации тактовых импульсов мент ИЛИ 14 подаются на такто вход счетчика 8 соответствующ ка (1,1, 1,2, ,,,, 1,N) форм границ изображения. Счетчики варительно обнулены выходным лом блока 11 N-ro блока 1,N п чании предыдущего цикла считы Триггеры 2,1, 2,2, ,.,, 2,N н записи информации устанавлива нулевое состояние сигналом З считывание. Блоки памяти эти налом, подаваемым на вход IJR водятся в режим записи. При э счетчики 8 последовательно по блоки памяти код адреса элем изображения, начиная с нулев в блоки памяти записывается информация по сигналу на вхо

По окончании режимг запис ной сигнал Запись/считывани водится в единичное состояни этом второй элемент И 13 откл тактовые импульсы за1шси от и входа CS блока памяти. Эле 6 и D-триггер 5 вырабатывают окончания записи длительност ной части периода сигнала счи (фиг, 56, в, г), который уст вает на выходах счетчиков 8 чального элемента считывания новленный на их входах D при

водит триггер 2,1 в единично ние (фиг. 5д). Сигнал с выхо гера 2,1 подается на первый И 12 блока 3.1 коммутации та импульсов и открывает прохожд тактового сигнала считывания ратора 4 на входы счетчика б формирования rji.iHHU изображе блока 7.1 памяти (фкг, 5е),

0

5 О

5

0

« первого формирователя 9 кода

5

ные перепады в зоне перекрытия полей зрения соседних ЛФСЗС,

Возможный вариант тест-изображения приведен на фиг, 4,

Работа формирователя делится на две фазы - запить информации в блоки памяти с выходов соответствующих ЛФСЗС и последовательное считывание информации из блоков памяти с исключением повторов в зонах перекрытия, что определяется входным сигналом Запись/считывание (фиг, 5а), В режиме записи тактовые импульсы записи в соответствующий блок памяти через второй элемент И 13 (фиг, 3) соответствующего блока (3,1, 3,2, ,,,, 3,N) коммутации тактовых импульсов и элемент ИЛИ 14 подаются на тактовый вход счетчика 8 соответствующего блока (1,1, 1,2, ,,,, 1,N) форм фования границ изображения. Счетчики 8 предварительно обнулены выходным сигналом блока 11 N-ro блока 1,N по окончании предыдущего цикла считывания. Триггеры 2,1, 2,2, ,.,, 2,N на время записи информации устанавливается в нулевое состояние сигналом Запись/ считывание. Блоки памяти этим же сигналом, подаваемым на вход IJR, переводятся в режим записи. При этом счетчики 8 последовательно подают на блоки памяти код адреса элементов изображения, начиная с нулевого, и в блоки памяти записывается входная информация по сигналу на входе CS,

По окончании режимг записи входной сигнал Запись/считывание переводится в единичное состояние, при этом второй элемент И 13 отключает тактовые импульсы за1шси от счетчика и входа CS блока памяти. Элемент И 6 и D-триггер 5 вырабатывают импульс окончания записи длительностью, равной части периода сигнала считывания (фиг, 56, в, г), который устанавливает на выходах счетчиков 8 код начального элемента считывания, установленный на их входах D при помощи

, и переводит триггер 2,1 в единичное состояние (фиг. 5д). Сигнал с выхода триггера 2,1 подается на первый элемент И 12 блока 3.1 коммутации тактовых импульсов и открывает прохождение тактового сигнала считывания с генератора 4 на входы счетчика блока 1. 1 формирования rji.iHHU изображения и блока 7.1 памяти (фкг, 5е), IB ре5. Г

зультате этого считывание из блока

7.1памяти начинается с адреса, установленного при помощи первого формирователя 9 кода (фиг. 5ж). По достижении счетчиком 8 кода адреса, установленного вторым формирователем 10 кода, блок II вырабатывает сигнал сброса триггера 2.1 и установки в единичное состояние триггера 2.2 (фиг. 5з), При этом подача .тактовых импульсов считывания на блок 1.1 формирования границ и блок 7.1 памяти прекращается и начинает работать блок 1.2 формирования границ и блок

7.2памяти (фиг. 5и,к,.л). Процесс опроса блока 7.2 памяти происходит аналогично, т.е. с элемента, номер которого установлен при помощи первого формирователя 9 кода, и до элемента, номер которого установлен вторым формирователем 10 кода. По окончании опроса N-ro блока 7.N памяти блок 11 N-ro блока 1.N формирования границ сбрасывает соответствующий триггер 2.N и устанавливает все счетчи и 8 в нулевое состояние, тем самым попго- тавливая формирователь к режиму Запись (фиг. 5м,н).

Таким образом, формирователь позволяет осуществлять сшивку видеосигналов сборки ЛФСЗС без разрывов и с меньшим временем считыва гия результирующего видеосигнала из блоков памяти .

Формула изобретения

. Формирователь видеосигнала, содержащий элемент И, первый, второй, ..,, N-Й блоки формирования сигнала границ изображения, первые выходы которых соединены с К-входами соответственно первого, второго,..., N-ro JK-триггеров, отличающий- с я тем, что, с целью уменьшения времени формирования видеосигнала и повышения его точности, введены D- триггер, первый, второй, ..., N-Й блokи коммутации тактовых импульсов, первый, второй, ..., N-Й блоки памяти, и генератор тактовых импульсов считывания видеосигналов, выход которого соединен с объединенными первыми входами первого, второго,...,N-ro блоков коммутации тактовЫх импульсов С-входом D-триггера и С-входами первого, второго, ..., N-ro JK-триггеров, выходы которых соединены с

рыми входами соответственно первого, второго, ..., N-ro блоков коммутации тактовых импульсов, третьи нхо.аьг которых объединены и являются входом для тактовых имгтульсов записи видеосигналов, выхо;да первого, второго, ,.., N-ro блоков коммутации тактовых импульсов соединены с первыми

Q входами соответственно первого, второго,..., N-ro блоков формирования сигнала границ изображения, которые объединены с входами выбора соответственно первого, второго,,.., N-ro

5 блоков памяти, выходы которых объединены и являются выходом видеосигнала, входы данных первого, второго, ..., N-ro блоков памяти являются входами для видеосигналов от соответст0 вующих линейных фоточувствителькых схем с зарядовой связью, адресные входы первого, второго, ..., N-ro блоков памяти соединены с вторыми входами соответственно первого, вто5 рого, ..., N-ro блоков формирования границ изображения, вторые входы которых объединены с J-входом первого Л -триггера и соединены с выходом элемента Н, первый вход которого

0 объединен с четвертыми входами первого, второго, ..., N-ro блоков коммутации тактовых импульсов, с входами разрешения первого, второго,...,N- го блоков памяти, с инверс гыми R-входами первого, второго, ..., N-ro ЛС-триггеров, с D-входом D-триггера и является входом управляющего сигнала запись/считывание, причем J-вход второго JK-триггера соединен с перп вым выходом первого блока формирования сигнала границ изображения, J-вход N-ro ЛС-триггера соединен с первым выходом (N-l)-ro блока формирования границ изображения, а К-вход

с N-ro JK-триггера объединен с третьими входами первого, второго, ...,N-ro блокбв формирования границ изображения, при этом второй вход элемента Н соединен с инверсным выходом D-триг0 гера.

2, Формирователь по п. 1, о т л и- чающийся тем, что казкдьш из блоков коммутации тактовых импульсов содержит первый и второй элементы И,

5

выходы которых соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого является выходом блока коммутации тактовых импульсов, при этом первый, BTopovi

входы первого элемента И, первый и инверсный второй вход второго элемента И являются соответственно первым, вторым, третьим и четвёртым входами блока коммутации тактовых импульсов.

3. Формирователь по п. 1, о т - личающийся тем, что каждый, из блоков формирования сигнала границ изображения содержит блок сравнения кодов, первый и второй входы которого соединены с выходами соответственно первого формирователя кода

и счетчика, информационный вход которого соединен с выходом второго формирователя кода, а вход сложения, вход разрешения записи и вход установки начального состояния счетчика являются соответственно первым, вторым и третьим входами блока формирования сигнала границ изображения, при этом выходы блока сравнения кодов и счетчика являются соответственно, первым и вторым выходами блока формирования сигнала границ изображения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ФОРМИРОВАНИЯ ВИДЕОСИГНАЛА | 1992 |

|

RU2027315C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для селекции элементов телевизионного изображения | 1983 |

|

SU1256054A1 |

| Устройство для отображения информации | 1989 |

|

SU1695373A1 |

| Устройство для индикации | 1984 |

|

SU1236540A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| Устройство обработки видеосигнала | 1989 |

|

SU1635284A1 |

| Устройство интерполяции для отображения графической информации | 1988 |

|

SU1525717A1 |

| СПОСОБ СЛЕЖЕНИЯ ЗА ОБЪЕКТОМ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2153235C2 |

| Формирователь сигнала изображения прибора с зарядовой связью (ПЗС) датчиков | 1988 |

|

SU1644401A1 |

Изобретение относится к телевидению. Цель изобретения - уменьшение времени формирования видеосигнала и повышение его точности. Формирователь видеосигнала содержит блоки 1 формирования границ изображения, триггеры 2, блоки 3 коммутации тактовых импульсов, г-р 4 тактовых импульсов считывания видеосигналов, D-триггер 5, эл-т И 6 и блоки памяти (БП) 7. Работа формирователя состоит из двух фаз: запись информации в БП 7 с выходов соответсвующих линейных фоточувствительных схем с зарядовой связью и последовательное считывание информации из БП 7 с исключением повторов в зонах перекрытия, что определяется входным сигналом "Запись/считывание". Такое выполнение формирователя позволяет осуществить "сшивку" видеосигналов сборки линейных фоточувствительных схем с зарядовой связью без разрывов и с меньшим временем считывания результирующего видеосигнала из БП 7. 2 з.п. ф-лы, 5 ил.

fpu2.2

.4

Фи2.5

5они ntofKpbmufl

Запись

ТН

е ытЛхмиГМ

Алл ,

SM9

eMM/natflf,

8шод триггера.

Выход

:г

.THзаписи Tn (.

Кд; ..jiJTvn.ijm-m.

Koffaffpeca 1 -тмер летмт11 Ана.} Ч

WO 7;I AnV Г TT

w

7/

Л/хо

ла;./

Лб/Д0(/

триггера t

ВымдГнзаписи

Илокад.г

Koi адреса блока 7.2

Вшо триггера l-fL

Выход блока 1 -HOftep /ifцента | ///g.; /конец} I IT .

...г1.

7f4 Ш19Ш9Л Кл

Ти cvumbtScfHtffl

JUL-JUt

I

, .4, .Аконе . /I

1А l/lZl M/Ll/I ТТЛ

Фиг.5

Редактор А.Маковская

Составитель З.Землянухин Техрец А.Кравчук

Заказ 7763/57

Тираж 626

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гпглрпмл, I M

c imiSuHue

:гпллп л

7f4 Ш19Ш9Л Кл

Ти cvumbtScfHtffl

JUL-JUt

I

, .4, .Аконе.2 . /I„

/I ТТЛ

Фиг.5

Корректор Т.Малец

Подписное

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1989-12-15—Публикация

1988-01-13—Подача