(Л

tol

СО

СО

О

1C

§

Изобретение относится к электросвязи и может быть использовано в системах телемеханики и передачи дан- ных для приема сигналов многопозиционной частотной модуляции.

Цель изобретения - повышение помехоустойчивости .

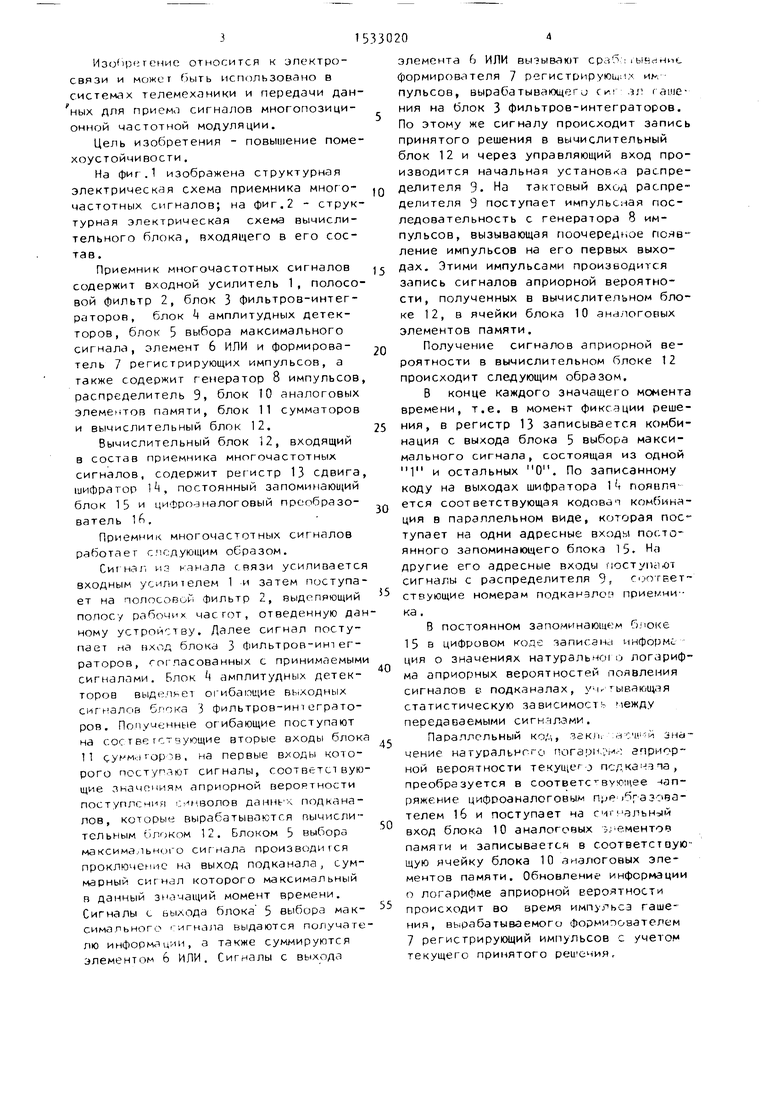

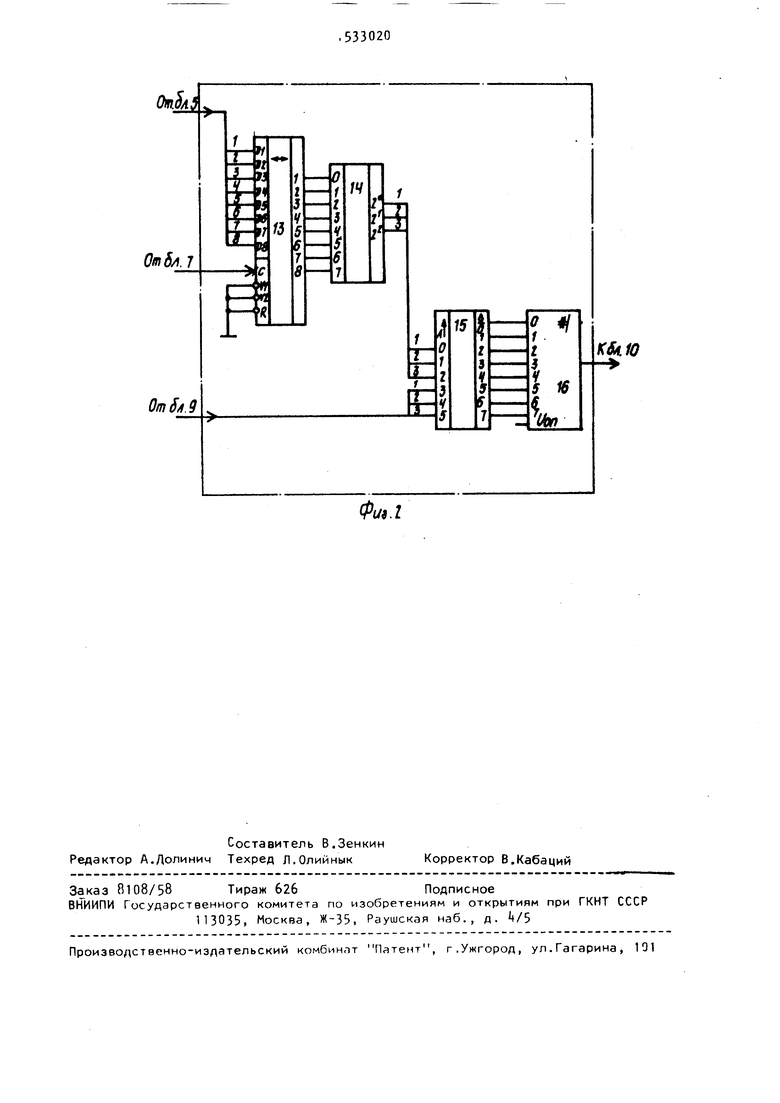

На фиг.1 изображена структурная электрическая схема приемника многочастотных сигналов; на фиг.2 - структурная электрическая схема вычислительного блока, входящего в его состав .

Приемник многочастотных сигналов содержит входной усилитель 1, полосовой фильтр 2, блок 3 фильтров-интег- раторов, блок 4 амплитудных детекторов, блок 5 выбора максимального сигнала, элемент 6 ИЛИ и формирователь 7 регистрирующих импульсов, а также содержит генератор 8 импульсов, распределитель 9, блок 10 аналоговых элементов памяти, блок 11 сумматоров и вычислительный блок 12.

Вычислительный блок 12, входящий в состав приемника многочастотных сигналов, содержит регистр 13 сдвига, шифратор И, постоянный запоминающий блок 15 и цифрою налоговый преобразователь 1 f.

Приемник многочастотных сигналов работает г гдующим образом.

Сиг на/, и ч напала связи усиливается входным усилителем 1 и затем поступает на полосовой фильтр 2, выделяющий попог/ рабочих частот, отведенную данному устрой тву. Далее сигнал поступает на вход блока 3 фильтров-интеграторов, ог пасованных с принимаемыми сигналами. Бпок Ц амплитудных детекторов выдгп ет oi ибапщие выгодных сигналов d ока 3 фильтров-интеграторов. Попучянные огибающие поступают на с о тве г -чующие вторые входы блока 11 сумм и , на первые входы которого поступают сигналы, гоотв т твую- щие значениям априорной вероятности поступлении -(волов даннь -. подканалов, которые вырабатываются вычислительным клоком 12. Блоком 5 выбора максима тьно о сигнала производи юя проключение на выход подканала, суммарный cm нал которого максимальный в данный значащий момент времени. Сигналы с ьыдода блока 5 выбора мак- еимапьноп1 игнала выдаются получателю информации, а также суммируются элементом 6 ИЛИ. Сигналы с выхода

0

5

0

0

5

0

5

0

5

элемента 6 ИЛИ вызывают ср-г формирователя 7 регистрируют, и пульсов, вырабатывающего си з. гашения на блок 3 фильтров-интеграторов. По этому же сигналу происходит запись принятого решения в вычислительный блок 12 и через управляющий вход производится начальная установка распределителя 9. На тактовый вход распределителя 9 поступает импульсная последовательность с генератора 8 импульсов, вызывающая поочередное появление импульсов на его первых выходах. Этими импульсами производится запись сигналов априорной вероятности, полученных в вычислитепьном блоке 12, в ячейки блока 10 аналоговых элементов памяти.

Получение сигналов априорной вероятности в вычислительном блоке 12 происходит следующим образом.

В конце каждого значаще о момента времени, т.е. в момент фиксации решения, в регистр 13 записывается комбинация с выхода блока 5 выбора максимального сигнала, состоящая из одной 1 и остальных О. По записанному коду на выходах шифратора 1Ч появлч ется соответствующая кодов-л комбинация в параллельном виде, которая пос тупает на одни адресные входы постоянного запоминающего блока 15. другие его адресные входы моступс от сигналы с распределителя 9, ги гвет- ствующие номерам подканале 5 приемни ка .

В постоянном запоминающем б юке 15 в цифровом коте записан информс. ция о значениях на тура ль -ten и логарифма априорных вероятностей появления сигналов Е подканалах, у итывающая статистическую зависимости между передаваемыми сигнчлам.

Параплельный ко/,, згки н и значение натуральнгго погаои;и - ной вероятности текущее псдка - па , преобразуется в cooTBeTc BVT nee напряжение цифроаналоговым .бгэз чэа- телем 16 и поступает ча вход блока 10 аналоговых ; ментоя памяти и записывается в соответствую щую ячейку блока 10 аналоговых элементов памяти. Обновление информации о логарифме априорной вероятности происходит во время гашения, вырабатываемого формирователем 7 регистрирующий импульсов с учетом текущего принятого реч ения.

Предлагаемый приемник может обеспечить существенный выигрыш в помехоустойчивости при наличии статистической зависимости между передаваемыми сигналами. Расчеты показывают что этот выигрыш может достигать одного порядка по сравнению с прототипом, в котором статистическая зависимость не учитывается.

Форму

изобретения

1.Приемник, многочастотных сигналов, содержащий последовательно соединенные входной усилитель и полосовой фильтр, блок фильтров-интеграторов, блок амплитудных детекторов, блок выбора максимального сигнала и последовательно соединенные элемент ИЛИ и формирователь регистрирующих импульсов, выход которого подключен к управляющему входу блока фильтров- интеграторов, сигнальный вход и выходы которого подключены соответственно к выходу полосового фильтра и входам блока амплитудных детекторов, причем входы элемента ИЛИ соединены с выходами блока выбора максимального сигнала, а вход входного усилителя является входом приемника, отличающийся тем, что, с целью почышения помехоустойчивости, введены последовательно соединенные генератор импульсов и распределитель, блок -.налоговых, элементов памяти, блок сумматоров и вычислительный блок, РЬ,ХОД которого соединен с сигнальным 4-одом блока аналоговых элементов

0

памяти, управляющие входы и выходы которого соединены с соответствующими первыми выходами распределителя и первыми входами блока сумматоров, вторые входы и выходы которого подключены соответственно к выходам блока амплитудных детекторов и входам блока выбора максимального сигнала, выходы которого подключены к информационным входам вычислительного блока, первый управляющий вход которого соединен с вторым выходом распределителя, управляющий вход которого соединен с 5 выходом формирователя регистрирующих импульсов и вторым управляющим входом вычислительного блока, при этом выходы блока выбора максимального сигнала являются выходами приемника.

0

2. Приемник по п.1, отличающий с я тем, что вычислительный блок содержит регистр сдвига, шифратор, постоянный запоминающий блок и

5 цифроаналоговый преобразователь, выход которого является выходом вычислительного блока, информационными входами которого являются информационные входы регистра сдвига, выходы

Q которого подключены к входам шифратора, выходы которого подключены к первым входам постоянного запоминающего блока, выходы которого соединены с входами цифроаналогового преобразователя, при этом второй вход постоянного

5 запоминающего блока и тактовый вход регистра сдвига являются соответственно первым и вторым управляющими входами вычислительного блока.

Фи.г

| название | год | авторы | номер документа |

|---|---|---|---|

| Приемник многочастотных сигналов | 1985 |

|

SU1284007A1 |

| Приемник многочастотных сигналов | 1988 |

|

SU1570032A2 |

| Устройство сбора телеметрической информации | 1988 |

|

SU1564672A1 |

| Устройство для приема многочастотных сигналов | 1987 |

|

SU1540031A1 |

| ЛИНИЯ ПЕРЕДАЧИ ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО ТРАКТАМ С ПЕРЕМЕННЫМИ ПАРАМЕТРАМИ | 1971 |

|

SU429546A1 |

| СИСТЕМА РАДИОВЕЩАНИЯ | 2008 |

|

RU2383103C1 |

| Устройство для приема двоичных сигналов | 1989 |

|

SU1709550A1 |

| УПРАВЛЯЮЩИЙ АППАРАТНО-ПРОГРАММНЫЙ КОМПЛЕКС ДЛЯ ОБРАБОТКИ РАДИОЛОКАЦИОННОЙ ИНФОРМАЦИИ | 2001 |

|

RU2222028C2 |

| Приемник многочастотных сигналов | 1991 |

|

SU1775874A1 |

| Способ выделения сигнала с модуляцией частотным сдвигом и компенсацией комбинационных составляющих | 2019 |

|

RU2723300C1 |

Изобретение относится к электросвязи. Цель изобретения - повышение помехоустойчивости. Приемник содержит усилитель 1, полосовой фильтр 2, блок фильтров-интеграторов 3-3м, блок амплитудных детекторов 4-4м, блок выбора 5 максимального сигнала, эл-т ИЛИ 6, формирователь 7 регистрирующих импульсов. Цель достигается введением г-ра 8 импульсов, распределителя 9, блока аналоговых эл-тов памяти 10-1°м, блока сумматоров 11-11м и вычислительного блока 12. При наличии статистической зависимости между передаваемыми сигналами достигается существенный выигрыш в помехоустойчивости. Приемник по п.2 ф-лы отличается выполнением вычислительного блока 12. 1 з.п.ф-лы, 2 ил.

| Авторское свилетельство СССР W | |||

| кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| ( ПРИЕМНИК МНОГОЧАСТОТНЫХ СИГНАЛОВ | |||

Авторы

Даты

1989-12-30—Публикация

1987-10-30—Подача