НэоОрегение относится к вычислительной технике.

Цель изобретения - повышение быстродействия .

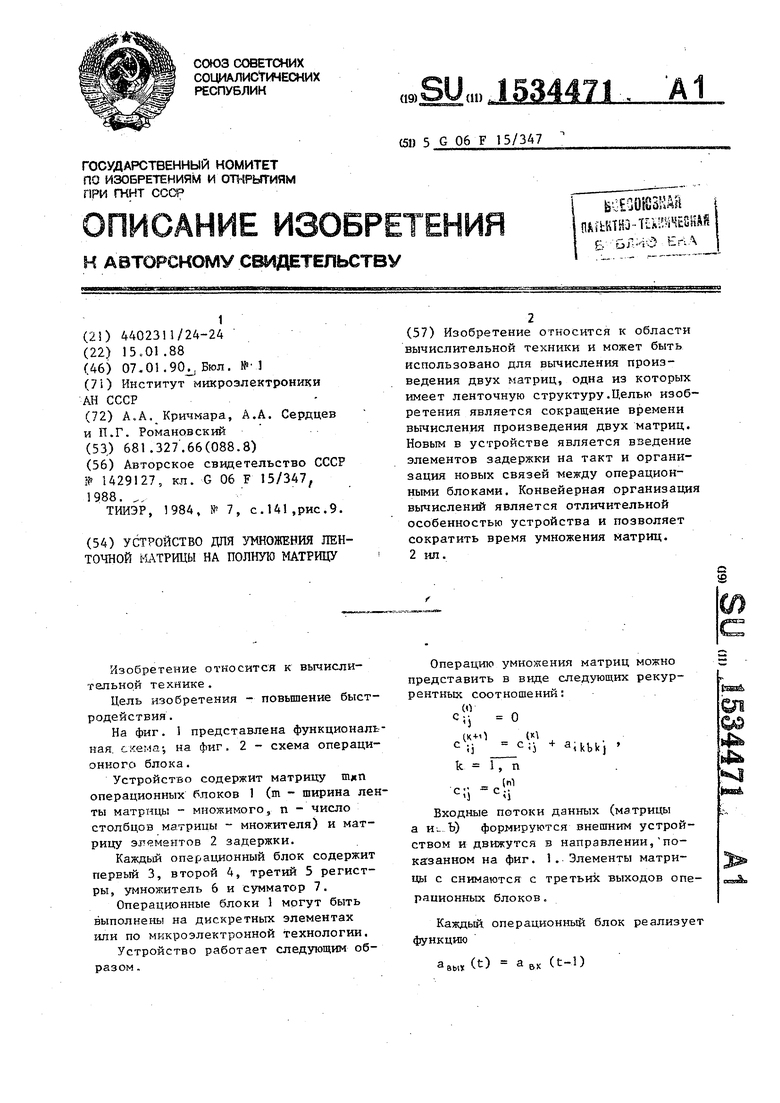

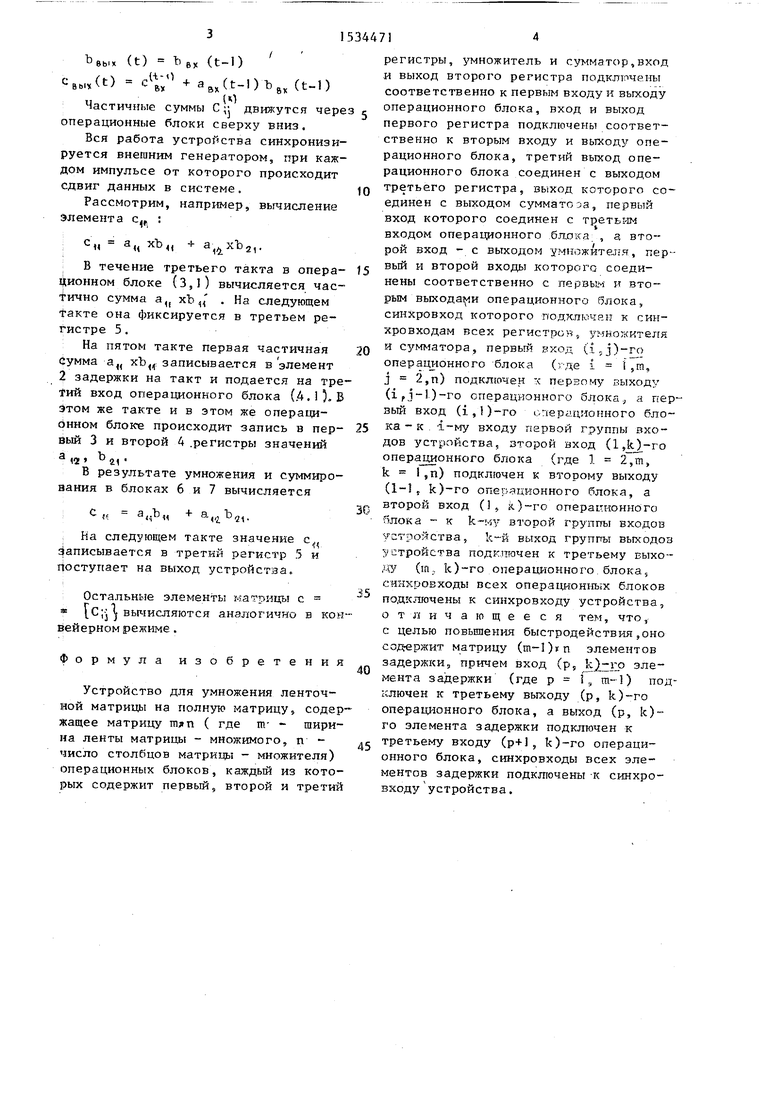

На фиг. 1 представлена функциональная чч-, ил фиг. 2 - схема операци- - нкого блока .

Устройство содержит матрицу операционных бпокоз 1 (т - ширина ленты магг ЩЫ миримого, п - число столбцов матрицы - множителя) и матрицу эр м°нгов 2 задержки.

Каждый операционный блок содержит первый 3, второй 4, третий 5 регистры, умножитель 6 и сумматор 7.

Операционные 1 могут быть выполнены на ди лретных элементах или по NU кроэлек гг С нной технологии.

Устройство работает следующим образом ,

Операцию умножения матриц можно представить в виде следующих рекуррентных соотношений: (О

)

О

( см

+ а.

kU

k 1 , n

(Ш г г CM М

Входные потоки данных (матрицы а и- Ъ) формируются внешним устройством и движутся в направлении, показанном на фиг. 1. Элементы матрицы с снимаются с третьих выходов операционных блоков .

Каждый операционный блок реализует функцию

СП

Од 4

HU

4

вы

(О аБХ (t-1)

с

вы

вы

(t)

(t) Ь

„И О

вх

(t-1)

в

+ aB,(t-l)bex(t-l)

Частичные суммы С;; движутся чере операционные блоки сверху вниз.

Вся работа устройства синхронизируется внешним генератором, при каждом импульсе от которого происходит сдвиг данных в системе.

Рассмотрим, например, вычисление элемента с,

с.,

ч

ац хЪ4,

а 4хЪ71.

В течение третьего такта в операционном блоке (3,1) вычисляется частично сумма а)( хЪ . На следующем такте она фиксируется в третьем регистре 5.

На пятом такте первая частичная сумма а)( записывается в элемент 2 задержки на такт и подается на третий вход операционного блока (.4 . 1 ). В этом же такте и в этом же операционном блоке происходит запись в первый 3 и второй 4 .регистры значений а,2, Ъ4, .

В результате умножения и суммирования в блоках 6 и 7

вычисляется

- а«Ъ„

а,,, Ъ,

ч

ha следующем такте значение с,( записывается в третий регистр 5 и поступает на выход устройства.

Остальные элементы матрицы с с;: вычисляются аналогично в конвейерном режиме .

Формула изобретения

Устройство для умножения ленточной матрицы на полную матрицу, содержащее матрицу тип ( где пт - ширина ленты матрицы - множимого, п - число столбцов матрицы - множителя) операционных блоков, каждый из которых содержит первый, второй и третий

5

0

5

С

0

третьим

вторегистры, умножитель и сумматор,вход и выход второго регистра подключены соответственно к первым входу и выходу операционного блока, вход и выход первого регистра подключены соответственно к вторым входу и выходу операционного блока, третий выход операционного блока соединен с выходом третьего регистра, выход которого соединен с выходом суммато я, первый вход которого соединен с входом операционного бллкл , а рой вход - с выходом умножителя, пер вый и второй входы которого соединены соответственно с первым и вторым выходами операционного блока, синхровход которого подключен к син- хровходам всех регистре;, умножителя и сумматора, первый вход U5j)-ro операционного блок л Оде i - 1 ,m, j 2,п) подключен ч перпому пыходу (i ,1-1)-го глтр.рац.мнного блока, ч первый вход (i,l)-ro -1ер; ционного бпо- ка - к г-му входу первой группы входов уст нства, второй вход (1, опера ционного блока (где 1 2,т, k l,n) подключен к второму выходу (1-1, k)-ro опег-я ионного блока, а второй вход (1, к)-го операционного лока - к k-чу второй группы входов усгюмства, k-и выход группы выходов у..тройства подключен к третьему ЕЫХО- ,uy (in k)-ro операционного блока, гннхровходы всех операционных блоков подключены к синхровходу устройства, отличающееся тем, что, с целью повышения быстродействия,оно содержит матрицу (m-)n элементов задержки, причем вход (р, k)-ro элемента задержки (где р 1, т-) подключен к третьему выходу (р, k)-ro операционного блока, а выход (р, k)- го элемента задержки подключен к дс третьему входу (р+1, k)-ro операционного блока, синхровходы всех элементов задержки подключены -к синхровходу устройства.

ffs fffjffftiOjf

- 051, a 1,3 Oj2 o21 о

-а33огга„ oo

-an 0000

1534471

IIII

IIII

ButBJIfafa

631Bn6130

62f6110 0

в„ООО

iAv

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения матриц | 1989 |

|

SU1677709A1 |

| Устройство для умножения матриц | 1987 |

|

SU1471201A1 |

| Устройство для умножения ленточной матрицы на вектор | 1988 |

|

SU1517039A1 |

| Устройство для умножения матриц | 1989 |

|

SU1619305A1 |

| Устройство для умножения матриц | 1990 |

|

SU1793446A1 |

| Устройство обращения матриц | 1987 |

|

SU1429126A1 |

| Устройство для умножения матрицы на вектор | 1990 |

|

SU1737463A1 |

| Устройство для умножения матриц | 1989 |

|

SU1619304A1 |

| Устройство для операций над матрицами | 1990 |

|

SU1735868A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1721612A1 |

Изобретение относится к области вычислительной техники и может быть использовано для вычисления произведения двух матриц, одна из которых имеет ленточную структуру. Целью изобретения является сокращение времени вычисления произведения двух матриц. Новым в устройстве является введение элементов задержки на такт и организация новых связей между операционными блоками. Конвейерная организация вычислений является отличительной особенностью устройства и позволяет сократить время умножения матриц. 2 ил.

| Устройство для матричных операций | 1987 |

|

SU1429127A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| , ТИИЭР, 1984, Я 7, с | |||

| Топливник с глухим подом | 1918 |

|

SU141A1 |

Авторы

Даты

1990-01-07—Публикация

1988-01-15—Подача