Изобретение относится к вычислительной технике и может использоваться для вычисления произведения ленточной матрицы на вектор при решении систем линейных уравнений, построении цифровых фильтров о

Целью изобретения является повышение быстродействия о

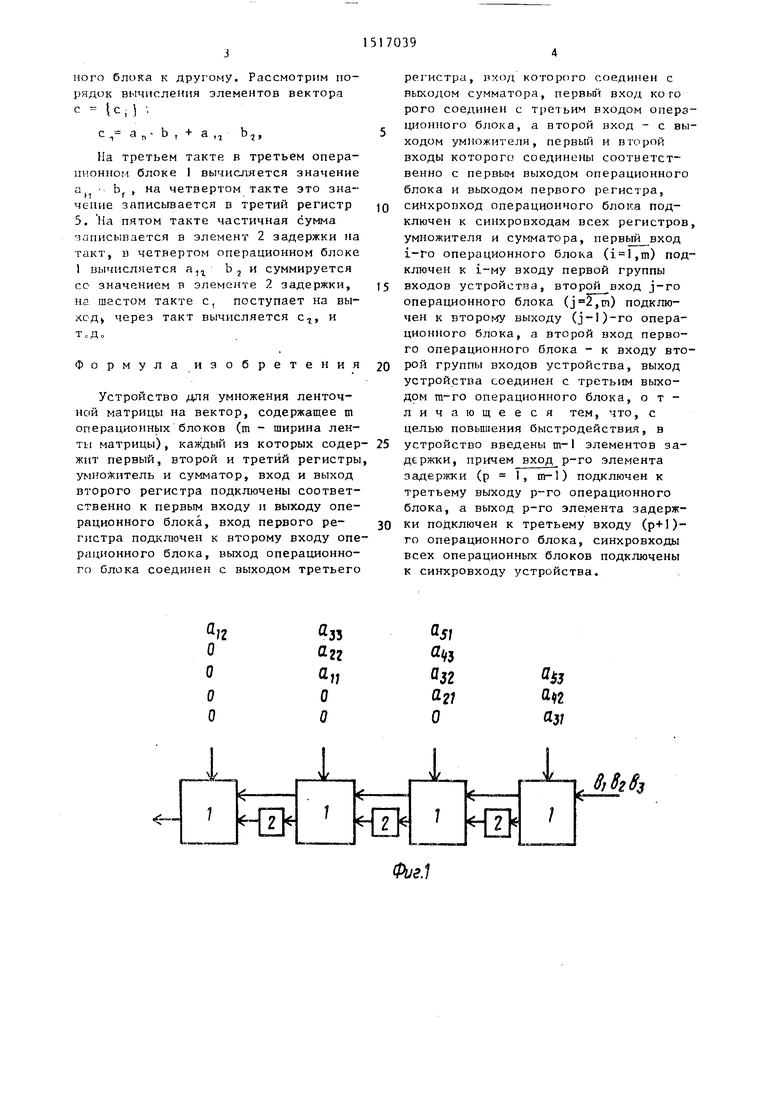

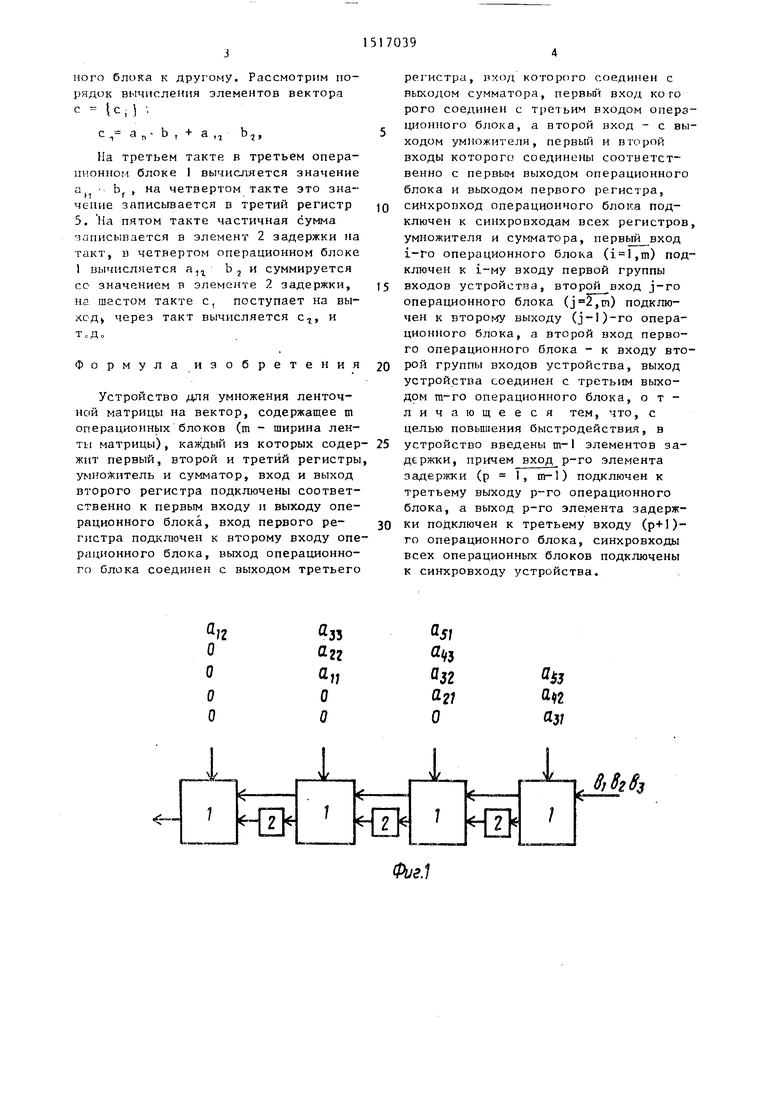

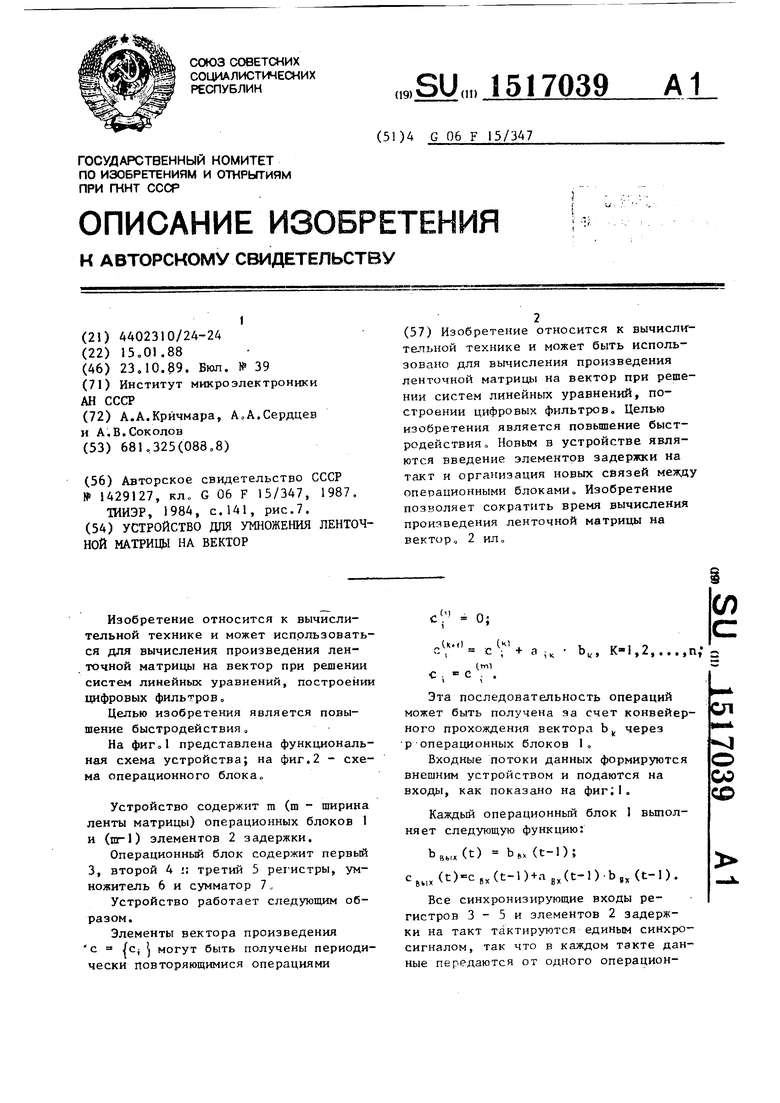

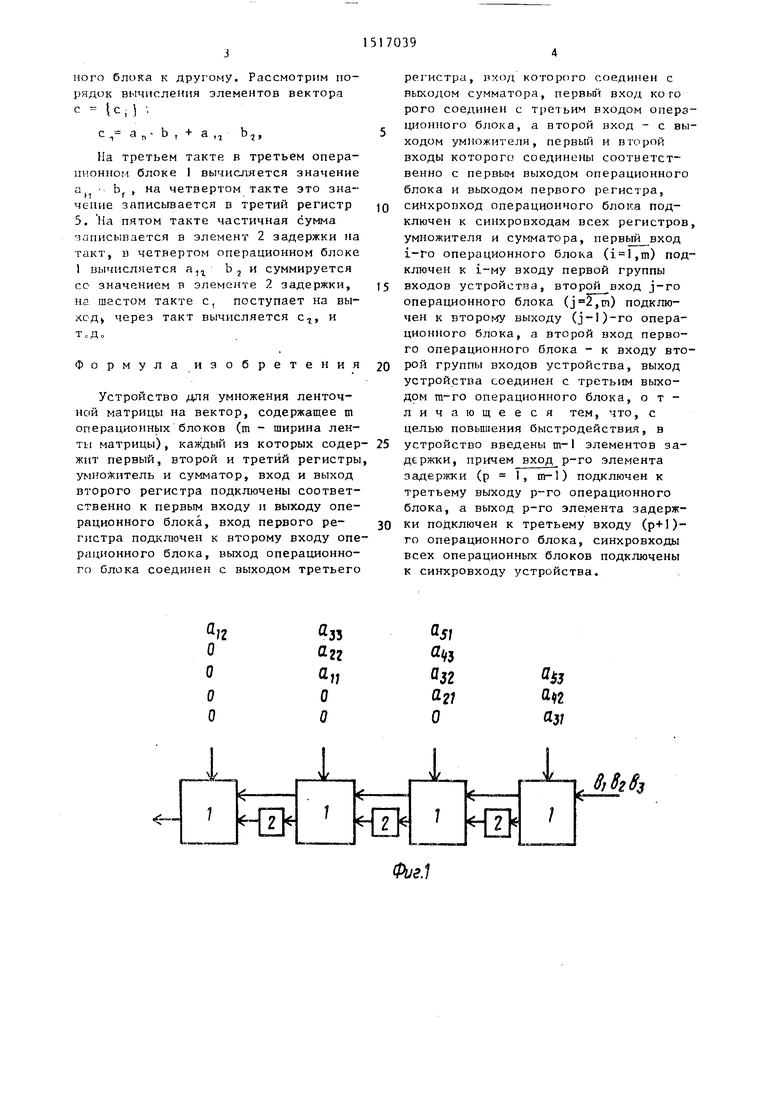

На фиго представлена функциональная схема устройства; на фиг,2 - схема операционного блока

Устройство содержит га (т - ширина ленты матрицы) операционных блоков 1 и (шгI) элементов 2 задержки.

Операционный блок содержит первый 3, второй 4 третий 5 рех истры, умножитель 6 и сумматор 7.

Устройство работает следующим образом.

Элементы вектора произведения с |cj могут быть получены периодически повторяющимися операциями

с ,

0;

(О

Дкм1

с : t а

ь, к-1,2,...,п; 2

с .

(ml

Эта последовательность операций может быть получена за счет конвейерного прохождения вектора Ь через р операционных блоков 1„

Входные потоки данных формируются внешним устройством и подаются на входы, как показано на фиг;1.

Каждый операционный блок 1 вьтол- няет следующую функцию:

b,,,,(t) b,,(t-l); c,,,(t)C8,(t-0+a,,(t-l)-b,,(t-l).

Все синхронизирующие входы регистров 3 - 5 и элементов 2 задержки на такт тактируются единым синхросигналом, так что в каждом такте данные передаются от одного операционсл

о

со

Horo блока к другому. Рассмотрим порядок вычисления элементов вектора

с ic,5 ,

с а „- b , + а , b.,,

На третьем такте в третьем операционном блоке I вычисляется значение а Ь , на четвертом такте это значение записьгаается в третий регистр 5. На пятом такте частичная сумма записывается в элемент 2 задержки на такт, 13 четвертом операционном блоке 1 вычисляется а, b-, и суммируется ее значением в элементе 2 задержки, на шестом такте с, поступает на вы- ход через такт вычисляется с, и

ТсД о

формула изобретения

Устройство для умножения ленточной матрицы на вектор, содержащее m операционных блоков (га - ширина ленты матрицы), каяддый из которых содер- жит первый, второй и третий регистры, 1но :итель и сумматор, вход и выход второго регистра подключены соответственно к первым входу и выходу операционного блока, вход первого ре- гистра подключен к второму входу операционного блока, выход операционного блока соединен с выходом третьего

регистра, РХ(5д которого соединен с выходом сумматора, первьп вход кого рого соединен с третьим входом операционного блока, а второй вход - с выходом умножителя, первый и второй входы которого соединены соответственно с первым выходом операционного блока и выходом первого регистра, синхровход операционного блока подключен к синхровходам всех регистров умножителя и сумматора, первый вход i-ro операционного блока (,т) под Kjm4eH к i-му входу первой группы входов устройства, второй вход j-ro операционного блока (,rn) подключен к второму выходу (j-I)-ro опера- цион)1ого блока, а второй вход первого операционного блока - к входу второй группы входов устройства, выход устройства соединен с третьим выходом га-го операционного блока, отличающееся тем, что, с целью повьш1ения быстродействия, в устройство введены т-1 элементов задержки, причем вход р-го элемента задержки (р 1, m-l) подключен к третьему выходу р-го операционного блока, а выход р-го элемента задержки подключен к третьему входу (р+1)- го операционного блока, синхровходы всех операционных блоков подключены к синхровходу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения ленточной матрицы на полную матрицу | 1988 |

|

SU1534471A1 |

| Устройство для умножения матриц | 1987 |

|

SU1471201A1 |

| Устройство для операции над матрицами | 1987 |

|

SU1534470A1 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1990 |

|

SU1751778A1 |

| Устройство для матричных операций | 1987 |

|

SU1429127A1 |

| Устройство для разложения теплицевых симметричных матриц | 1990 |

|

SU1755295A2 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

| Матричное устройство для вычисления свертки | 1986 |

|

SU1401477A1 |

| Устройство для обращения матриц | 1987 |

|

SU1527643A1 |

| Генератор функций Попенко-Турко | 1990 |

|

SU1753464A1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления произведения ленточной матрицы на вектор при решении систем линейных уравнений, построении цифровых фильтров. Целью изобретения является повышение быстродействия. Новым в устройстве являются введение элементов задержки на такт и организация новых связей между операционными блоками. Изобретение позволяет сократить время вычисления произведения ленточной матрицы на вектор. 2 ил.

33

сгг

О

о

1

%

0-чг яз;

CSbix г-

Шиг. 2

-

QBX

.4 л

5л

| Устройство для матричных операций | 1987 |

|

SU1429127A1 |

Авторы

Даты

1989-10-23—Публикация

1988-01-15—Подача