4

v|

N3

Изобретение относится к вычислтельной технике и может быть испозовано при построении специализирванных вычислительных систем, фунционирующих в реальном масштабе времени.;

Цель изобретения - повышение быстродействия.

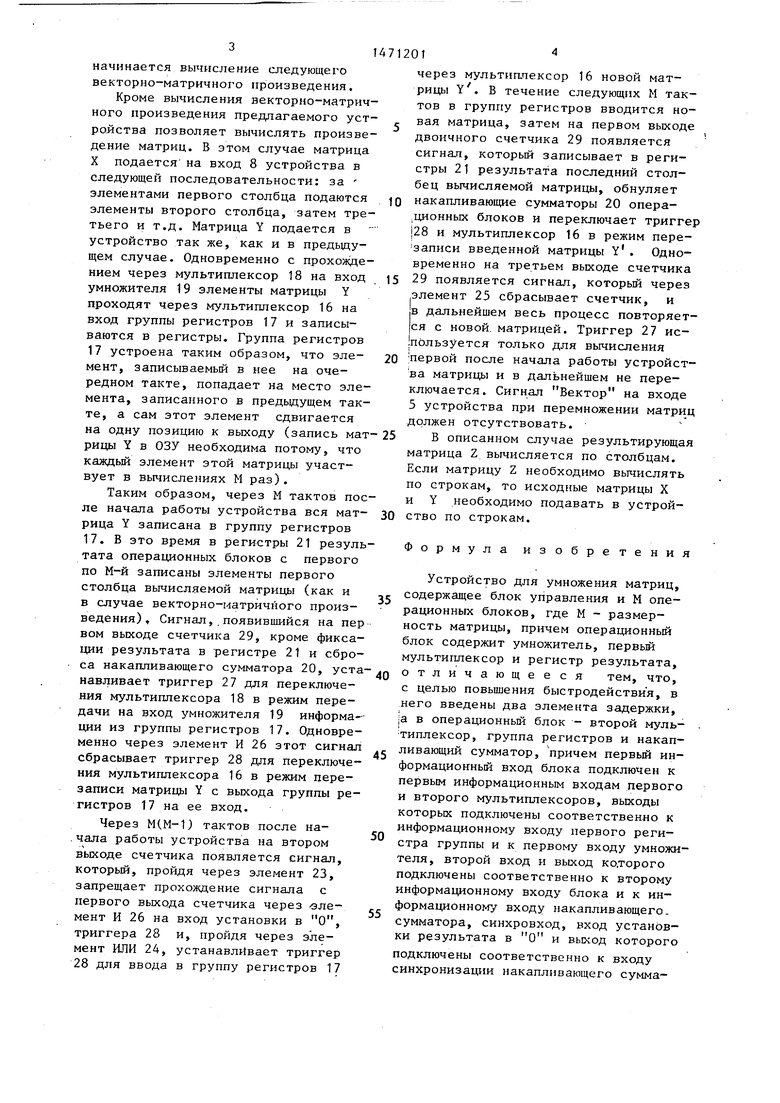

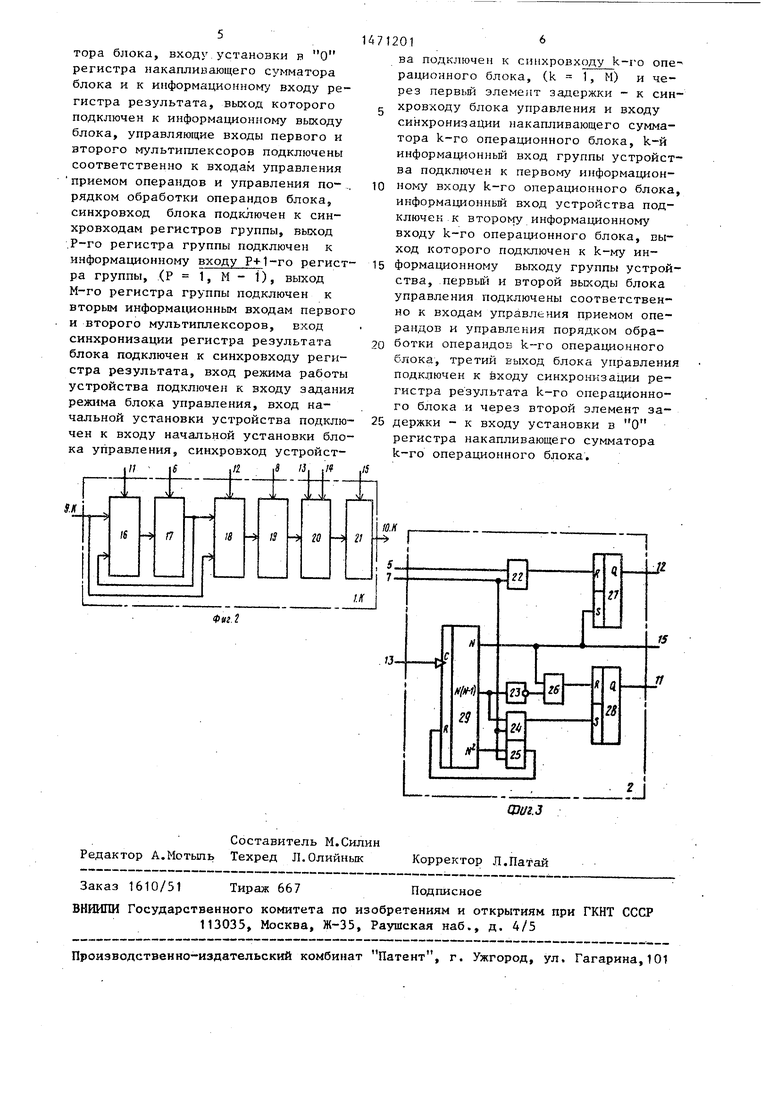

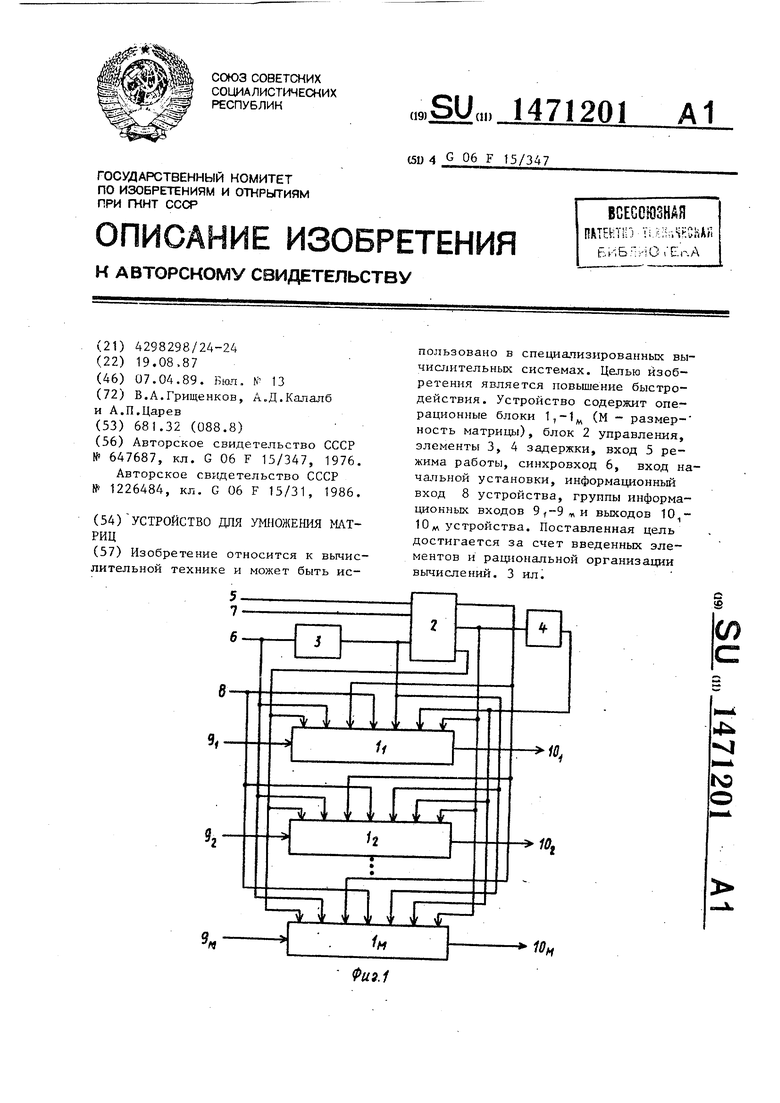

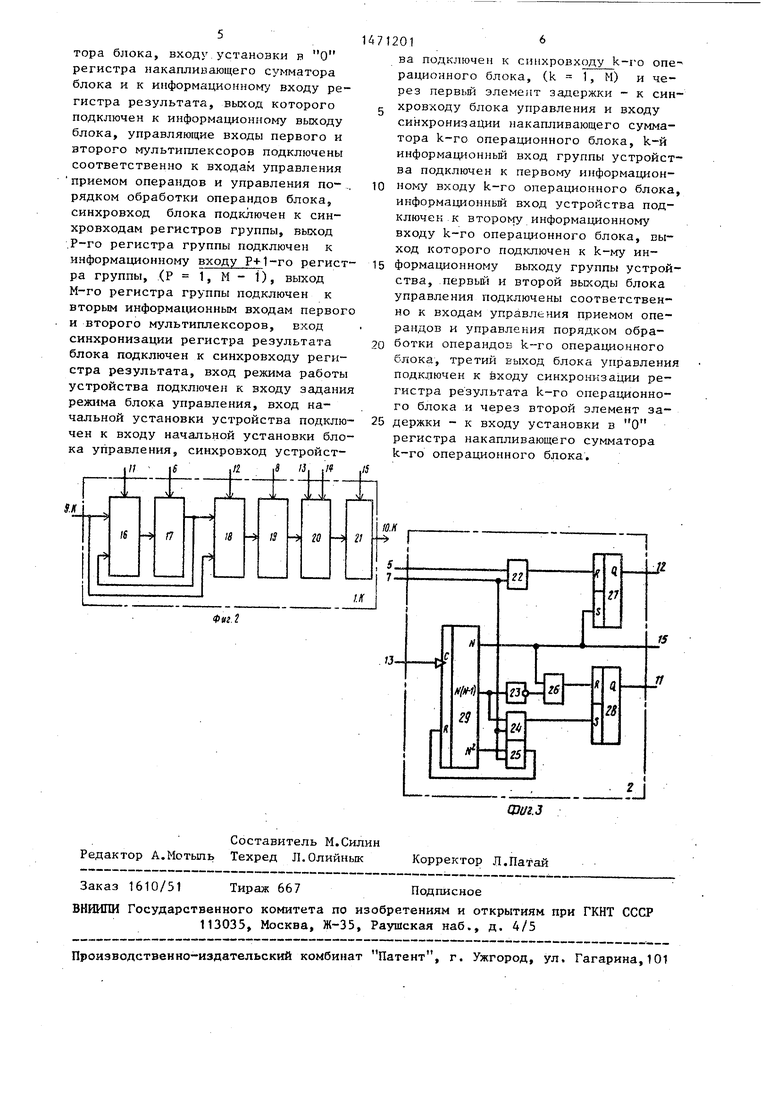

На фиг.1 представлена функциональная схема устройства; на фиг. функциональная схема операционног блока{ на фиг.З - функциональная схема блока управления.

Устройство содержит операционные блоки ,, где М - размернос матрицы, блок 2 управления, элементы 3 и 4 задержки, вход 5 режима рботы устройства, синхровход 6 устройства, вход 7 начальной установк устройства, информационньй вход 8 устройства, группу информационных входов 91-9„ устройства, группу информационных выходов устройства, входы 11 управления приемом операндов, 12 управления поряд обработки операндов ,13 синхронизации накапливающего сумматора, 14 установки в О регистра накаплива щего сумматора, 15 синхронизации регистра результата операционного блока, мультиплексор 16, группу регистров 17, мультиплексор 18, умножитель 19, накапливающий сумматор 20, регистр 21 результата, элемент ИЛИ 22, элемент НЕ 23, элементы ИЛИ 24 и 25, элемент И 26, триггеры 27 и 28, счетчик 29.

Устройство работает следующим образом.

При включении питания сигнал Сброс с входа 7 устройства проходит через элементы ИЛИ 22, 24 и 25, сбрасывает счетчик 29, триггер 27 и устанавливает триггер 28. При этом триггеры 27 и 28 включают мультиплексоры 16 и 18 таким образом, что информация, поступающая в операционный блок 1.К с входа 9.К проходит через мультиплексор 16 в группу регистров 17 и одновременно через мультиплексор 18 поступает н умножитель 19. При умножении вектора на матрицу на вход 5 устройства подается сигнал Вектор, имеющий уровень логической единицы. В отличие от сигнала Сброс, который подается импульсом, сигнал Вектор подается потенциалом и присутствуе

10

15

20

25

30

35

40

45

0

на входе 5 в течение всего процесса векторно-матричных вьпшслений. Вектор X поступает на вход 8 устройства поэлементно (в каждом такте по одному элементу). Матрица Y подается в устройство по столбцам - в каждом такте работы устройства в k-й опе- рационньй блок подается очередной элемент k-й строки матрицы Y.

Каждый элемент вектора X поступает на первые входы умножителей всех операционных блоков одновременно. На второй вход умножителя поступает соответствующий . элемент матрицы Y. Произведение этих элементов подается на вход накапливающего сумматора 20 и складывается с его содержимым. Алгоритм работы устройства в режиме умножения вектора на матрицу может быть описан следующим образом.

Элемент результирующего вектора с номером Р представляет собой скалярное произведение Р-й строки матрищ, на исходный вектор, , М-1.

Элемент 3 необходим для задержки сигнала синхронизации накапливающе- го сумматора на время, необходимое для умножения элементов вектора и матрицы. Через М тактов после начала работы устройства каддый элемент вектора X перемножается и суммируется в k-M операционном блоке с соответствующими элементами k-й строки матрицы У. В накапливающем сумматоре k-ro операционного блока оказывается k-й элемент вычисляемого вектора произведения: в первом операционном блоке - первьй элемент вычисляемого вектора, во втором - второй и т.д. В это время на первом выходе счетчика 29 появляется сигнал, который стро- бирует запись результата, находящегося к этому моменту времени в накапливающем сумматоре .20, в регистр 21 результата. Этот сигнал, пройдя через элемент 4 задержки, сбрасывает накапливающий сумматор в О, подготовив его тем самым к вычислению элементов следующего вектора. Элемент 4 необходим для задержки сигнала сброса накапливающего сумматора на время, необходимое для записи результата в регистр 21.

Таким образом, через М тактов после начала работы на выходе устройства появляется весь вычисляемьй вектор, а начиная с (М+О-го такта

T i71201

начинается вычисление следующего векторно-матричного произведения.

Кроме вычисления векторно-матричного произведения предлагаемого устройства позволяет вычислять произве- дение матриц, В этом случае матрица X подается на вход 8 устройства в следующей последовательности: за - элементами первого столбца подаются JQ элементы второго столбца, затем третьего и т.д. Матрица Y подается в - устройство так же, как и в предьщу- щем случае. Одновременно с прохождением через мультиплексор 18 на вход 15 умножителя 19 элементы матрицы Y проходят через мультиплексор 16 на вход группы регистров 17 и записываются в регистры. Группа регистров 17 устроена таким образом, что эле- 20 мент, записываемый в нее на очередном такте, попадает на место элемента, записанного в предыдущем такте, а сам этот элемент сдвигается на одну позицию к выходу (запись мат- 25 рицы Y в ОЗУ необходима потому, что каждьш элемент этой матрицы участвует в вычислениях М раз).

Таким образом, через М тактов после начала работы устройства вся мат- ЗО рица Y записана в группу регистров 17. В это время в регистры 21 резуль- Формул тата операционных блоков с первого по М-й записаны элементы первого столбца вычисляемой матрицы (как и в случае векторно-матричного произведения). Сигнал,.появившийся на пер вом выходе счетчика 29, кроме фиксации результата в регистре 21 и сбро- са накапливающего сумматора 20, уста- навливает триггер 27 для переключения мультиплексора 18 в режим передачи на вход умножителя 19 информа-- ции из группы регистров 17. Одновременно через элемент И 26 этот сигнал сбрасывает триггер 28 для переключения мультиплексора 16 в режим перезаписи матрицы Y с выхода группы регистров 17 на ее вход.

Через М(М-1) тактов после на- чала работы устройства на втором выходе счетчика появляется сигнал, который, пройдя через элемент 23, запрещает прохождение сигнала с первого выхода счетчика через -элемент И 26 на вход установки в О, триггера 28 и, пройдя через элеент ИЛИ 24, устанавливает триггер 8 для ввода в группу регистров 17

через муль рицы Y . В тов в груп вая матриц двоичного сигнал, ко стры 21 ре бец вычисля накапливающ .ционных бло J28 и мульти записи введ временно на 29 появляет .элемент 25 в дальнейше ся с новой- пользуется :первой посл ва матрицы ключается. 5 устройств должен отсу

В описан матрица Z вы Если матрицу по строкам, и Y необхо ство по стро

35

45

50

55

Устройств содержащее б рационных бл ность матриц блок содержи мультигшексо отлича с целью повы него введены |а в операцио типлексор, гр ливающий сумм формационньш первым информ и второго мул которых подкл информационно стра группы и теля, второй подключены со информационно формационному сумматора, си ки результата подключены со синхронизации

Формул

через мультиплексор 16 новой матрицы Y . В течение следующих М тактов в группу регистров вводится новая матрица, затем на первом выходе двоичного счетчика 29 появляется сигнал, который записывает в регистры 21 результата последний столбец вычисляемой матрицы, обнуляет накапливающие сумматоры 20 опера- .ционных блоков и переключает тригге J28 и мультиплексор 16 в режим пере- записи введенной матрицы Y . Одновременно на третьем выходе счетчика 29 появляется сигнал, который через .элемент 25 сбрасывает счетчик, и в дальнейшем весь процесс повторяется с новой- матрицей. Триггер 27 используется только для вычисления :первой после начала работы устройства матрицы и в дальнейшем не переключается. Сигнал Вектор на входе 5 устройства при перемножении матриц должен отсутствовать.

В описанном случае результирующая матрица Z вычисляется по столбцам. Если матрицу Z необходимо вычислять по строкам, то исходные матрицы X и Y необходимо подавать в устройство по строкам.

изобретения

ЗОФормул

35

45

50

5

Устройство для умножения матриц, содержащее блок управления и М операционных блоков, где М - размерность матрицы, причем операционный блок содержит умножитель, первьй мультигшексор и регистр результата, отличающееся тем, что с целью повышения быстродействия, в него введены два элемента задержки, |а в операционный блок - второй мультиплексор, группа регистров и накапливающий сумматор, причем первьй ин- формационньш вход блока подключен к первым информационным входам первого и второго мультиплексоров, выходы которых подключены соответственно к информационному входу первого регистра группы и к первому входу умножителя, второй вход и выход ко.торого подключены соответственно к второму информационному входу блока и к информационному входу накапливающего, сумматора, синхровход, вход установки результата в О и выход которого подключены соответственно к входу синхронизации накапливающего сумма П - ,в /Jj jtf ,15

i ИTi Г

Т-Г--Г

1/4/.чЬ.J;

11

S.K

фуг. 2

г

15

п

: 25

.fj

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения систем линейных алгебраических уравнений | 1988 |

|

SU1569846A1 |

| Устройство для обращения матриц | 1988 |

|

SU1575204A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1425706A1 |

| НЕЙРОПРОЦЕССОР, УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИЙ НАСЫЩЕНИЯ, ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО И СУММАТОР | 1998 |

|

RU2131145C1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| УСТРОЙСТВО ПОДСЧЕТА МИНИМАЛЬНОГО ЗНАЧЕНИЯ ИНТЕНСИВНОСТИ РАЗМЕЩЕНИЯ В СИСТЕМАХ С КОЛЬЦЕВОЙ ОРГАНИЗАЦИЕЙ | 2005 |

|

RU2297027C1 |

| Устройство для LU - разложения матриц | 1988 |

|

SU1661793A1 |

| Устройство для решения систем линейных алгебраических уравнений | 1986 |

|

SU1325508A1 |

| Вычислительное устройство | 1987 |

|

SU1432511A1 |

| Устройство для вычисления матрицы функций | 1987 |

|

SU1439617A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных системах. Целью изобретения является повышение быстродействия. Устройство содержит операционные блоки 11 - 1М (М - размерность матрицы), блок 2 управления, элементы 3,4 задержки, вход 5 режима работы, синхровход 6, вход начальной установки, информационный вход 8 устройства, группы информационных входов 91 - 9М и выходов 101 - 10М устройства. Поставленная цель достигается за счет введенных элементов и рациональной организации вычислений. 3 ил.

| Устройство для операций над матрицами | 1976 |

|

SU647687A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство умножения матрицы на вектор | 1984 |

|

SU1226484A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-04-07—Публикация

1987-08-19—Подача