ЕЫВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления трехфазным вентильным инвертором | 1988 |

|

SU1525845A1 |

| Устройство для управления регулируемым мостовым инвертором | 1987 |

|

SU1432699A1 |

| Устройство для управления автономным мостовым инвертором | 1987 |

|

SU1483575A1 |

| Устройство для управления автономным регулируемым инвертором | 1985 |

|

SU1272430A1 |

| Устройство для управления автономным регулируемым инвертором напряжения | 1986 |

|

SU1368949A1 |

| Устройство для управления автономным регулируемым инвертором | 1984 |

|

SU1257786A2 |

| Способ управления трехфазным регулируемым мостовым инвертором | 1987 |

|

SU1492434A1 |

| Устройство для управления автономным инвертором напряжения | 1987 |

|

SU1483574A1 |

| Устройство для управления инвертором с многоуровневым выходным напряжением | 1985 |

|

SU1304153A1 |

| Устройство для управления преобразователем с многоуровневым выходным напряжением для электропривода | 1986 |

|

SU1368948A1 |

Изобретение относится к электротехнике и может быть использовано при управлении преобразователями для систем асинхронного электропривода. Целью изобретения является уменьшение коммутационных потерь в инверторе в процессе связанного регулирования частоты и величины выходного напряжения. В инвертор введены усилитель 10 с коэффициентом передачи, равным двум, ключ 20, многовходовой сумматор 21, входы которого соединены со всеми выходами блока 15 обеспечения коммутационной устойчивости и с выходными клеммами ключей 17 и 20, двухвходовой интегратор 22, входы которого соединены с сумматором 21 и дополнительным источником 23, а выходы подключены к усилителю 10 и сумматору 8. Инвертор позволяет обеспечить связанное линейное регулирование частоты и величины среднего на полупериоде значения выходного напряжения, осуществляемое путем поэтапной вариации временного положения одного из фронтов (переднего или заднего) каждого из выходных импульсов, что снижает общее число коммутаций силовых вентилей особенно в диапазоне повышенных выходных частот преобразователя и приводит к уменьшению суммарной величины коммутационных потерь. 4 ил.

и

W

С

сп

со

Јь vl

31534

двум, ключ 20, многовходовой сумматор 219 входы которого соединены со все- и выходами блока 15 обеспечения ком- Мутационной устойчивости и с выходными клеммами ключей 17 и 20, двухвхо- довой интегратор 22, входы которого соединены с сумматором 21 и дополнительным источником 23, а выходы подключены к усилителю 10 и сумматору 8. Инвертор позволяет обеспечить связанное линейное регулирование частоты

Изобретение относится к электротехнике и может быть использовано для управления автономными трехфазны- Ии инверторами, входящими в состав -систем асинхронного электропривода. Целью изобретения является уменьшение коммутационных потерь в инверторе в процессе связанного регулиро- вания частоты и величины выходного напряжения, обеспечиваемое за счет снижения числа дополнительных коммутаций в силовой схеме преобразователя.

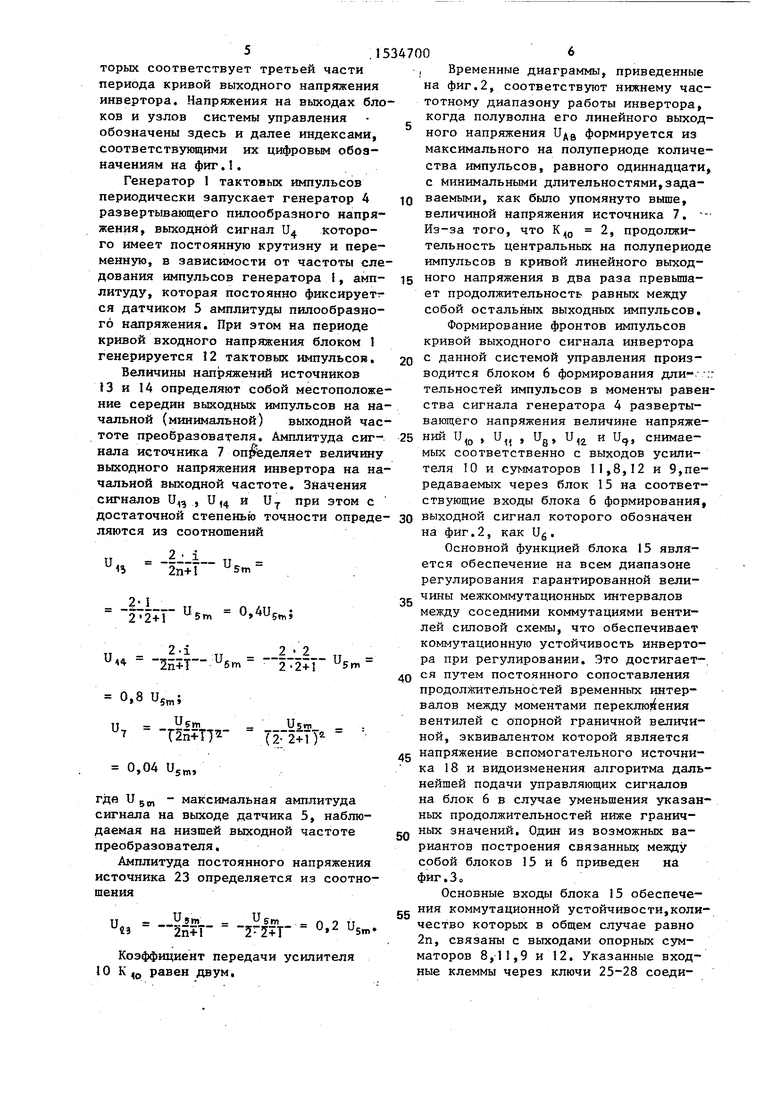

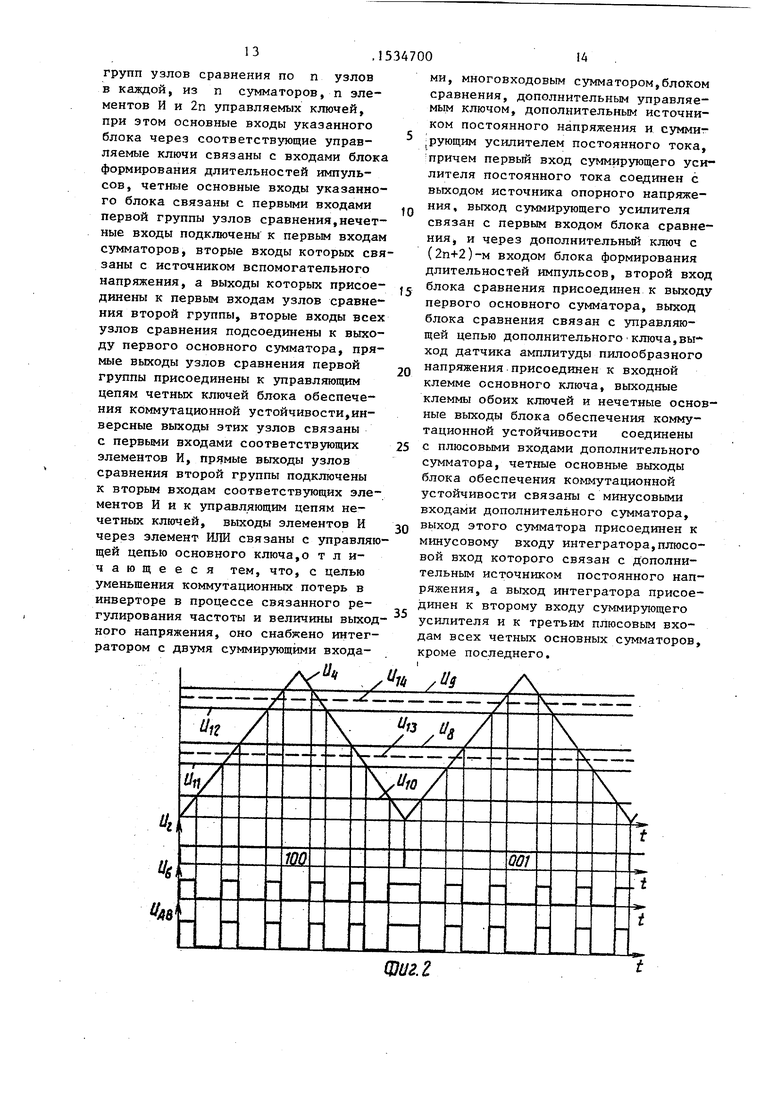

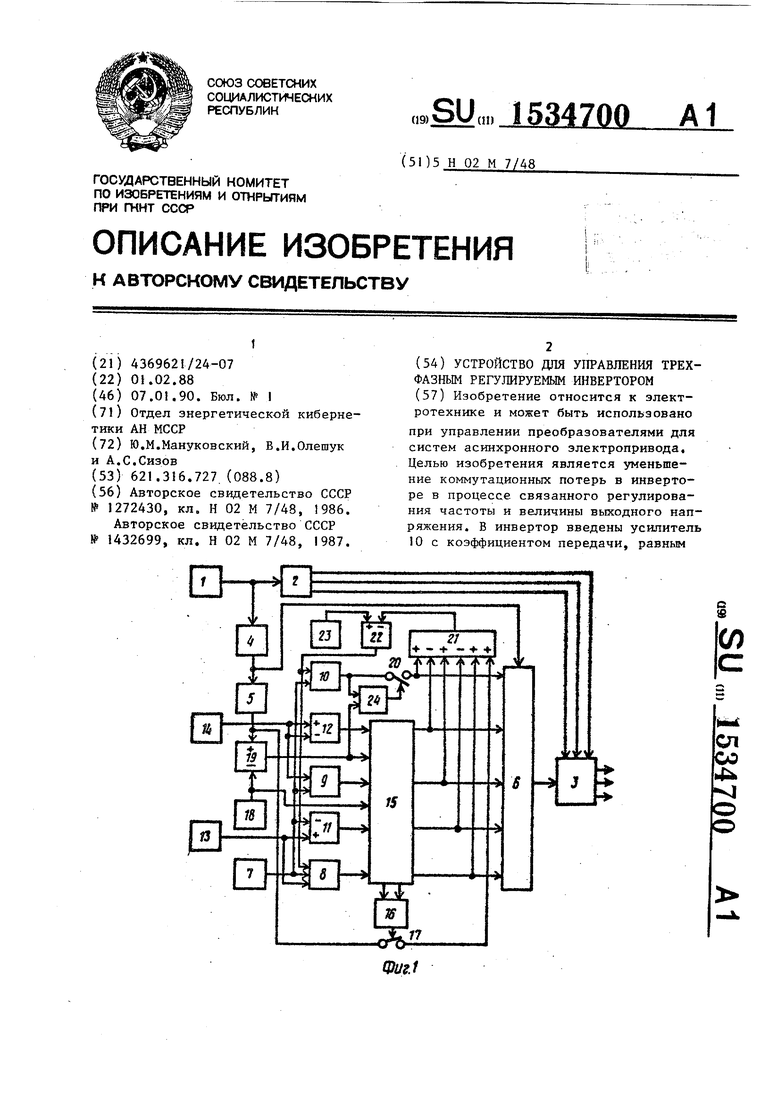

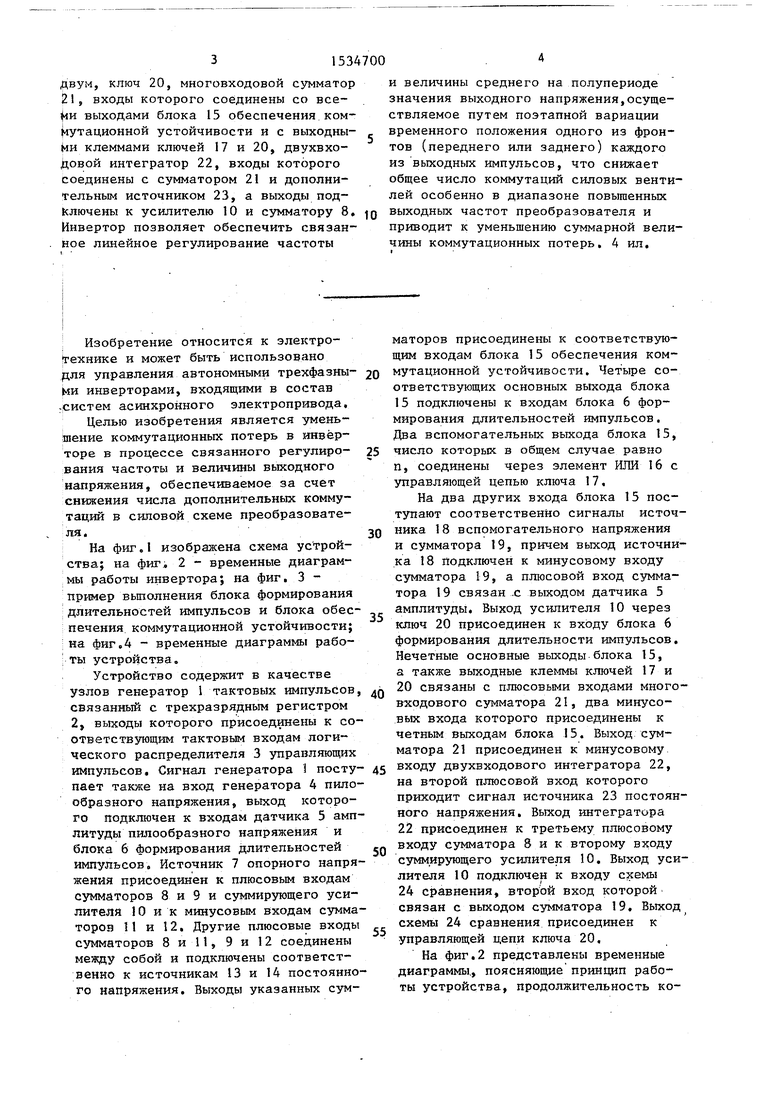

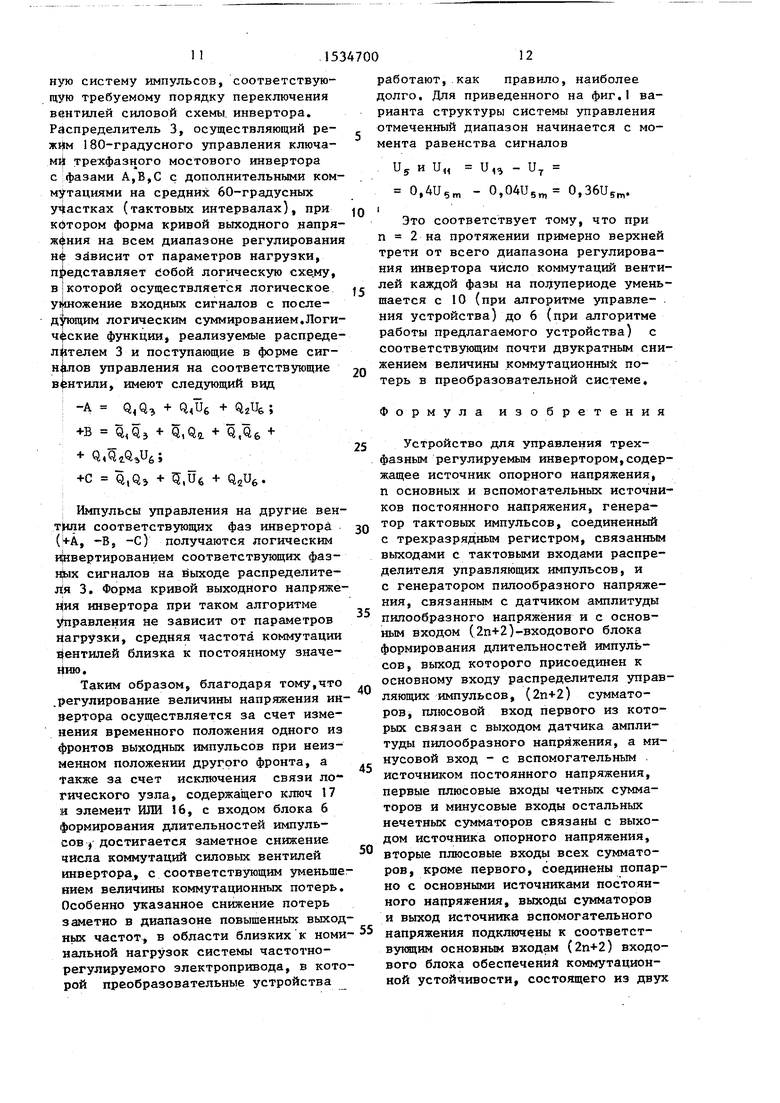

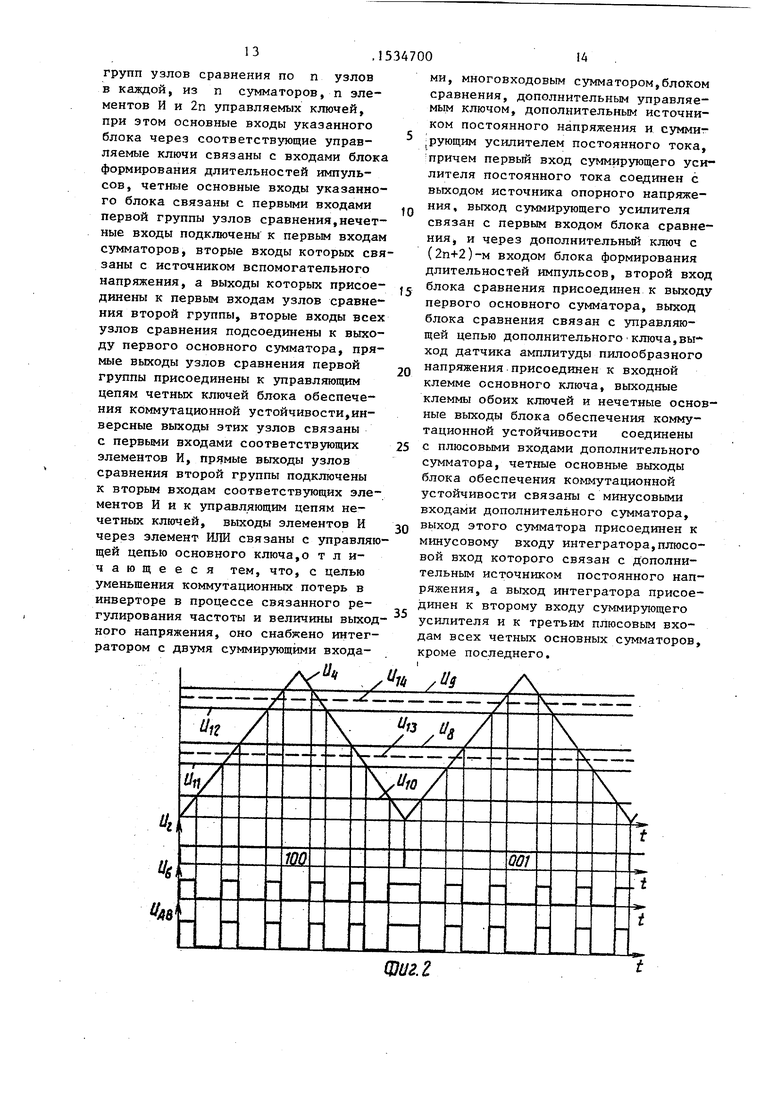

На фиг.I изображена схема устройства; на фиг, 2 - временные диаграммы работы инвертора; на фиг. 3 - пример выполнения блока формирования длительностей импульсов и блока обес- печения коммутационной устойчивости; на фиг,4 - временные диаграммы работы устройства.

Устройство содержит в качестве узлов генератор 1 тактовых импульсов, связанный с трехразрядным регистром 2, выходы которого присоединены к соответствующим тактовым входам логического распределителя 3 управляющих импульсов. Сигнал генератора i посту- пает также на вход генератора 4 пилообразного напряжения, выход которого подключен к входам датчика 5 амплитуды пилообразного напряжения и блока 6 формирования длительностей импульсов. Источник 7 опорного напряжения присоединен к плюсовым входам сумматоров 8 и 9 и суммирующего усилителя 10 и к минусовым входам сумма- тороа 11 и 12. Другие плюсовые входы сумматоров 8 и 11, 9 и 12 соединены между собой и подключены соответственно к источникам 13 и 14 постоянного напряжения. Выходы указанных суми величины среднего на полупериоде значения выходного напряжения,осуществляемое путем поэтапной вариации временного положения одного из фронтов (переднего или заднего) каждого из выходных импульсов, что снижает общее число коммутаций силовых вентилей особенно в диапазоне повышенных выходных частот преобразователя и приводит к уменьшению суммарной величины коммутационных потерь. 4 ил.

маторов присоединены к соответствующим входам блока 15 обеспечения коммутационной устойчивости. Четыре соответствующих основных выхода блока 15 подключены к входам блока 6 формирования длительностей импульсов. Два вспомогательных выхода блока 15, число которых в общем случае равно п, соединены через элемент ИЛИ 16 с управляющей цепью ключа 17,

На два других входа блока 15 поступают соответственно сигналы источника 18 вспомогательного напряжения и сумматора 19, причем выход источника 18 подключен к минусовому входу сумматора 19, а плюсовой вход сумматора 19 связан с выходом датчика 5 амплитуды, Выход усилителя 10 через ключ 20 присоединен к входу блока 6 формирования длительности импульсов. Нечетные основные выходы блока 15, а также выходные клеммы ключей 17 и 20 связаны с плюсовыми входами много входового сумматора 21, два минусовых входа которого присоединены к четным выходам блока 15. Выход сумматора 21 присоединен к минусовому входу двухвходового интегратора 22, на второй плюсовой вход которого приходит сигнал источника 23 постоянного напряжения. Выход интегратора 22 присоединен к третьему плюсовому входу сумматора 8 и к второму входу суммирующего усилителя 10. Выход усилителя 10 подключен к входу схемы 24 сравнения, второй вход которой связан с выходом сумматора 19, Выход схемы 24 сравнения присоединен к управляющей цепи ключа 20.

На фиг.2 представлены временные диаграммы, поясняющие принцип работы устройства, продолжительность которых соответствует третьей части периода кривой выходного напряжения инвертора. Напряжения на выходах блоков и узлов системы управления обозначены здесь и далее индексами, соответствующими их цифровым обозначениям на фиг.1.

Генератор 1 тактовых импульсов периодически запускает генератор 4 развертывающего пилообразного напряжения, выходной сигнал 114 которого имеет постоянную крутизну и переменную, в зависимости от частоты следования импульсов генератора f, амплитуду, которая постоянно фиксируетг- ся датчиком 5 амплитуды пилообразного напряжения. При этом на периоде кривой входного напряжения блоком 1 генерируется 12 тактовых импульсов.

Величины напряжений источников 13 и 14 определяют собой местоположение середин выходных импульсов на начальной (минимальной) выходной частоте преобразователя. Амплитуда сигнала источника 7 определяет величину выходного напряжения инвертора на начальной выходной частоте. Значения сигналов Vn , U ,4 и U7 при этом с достаточной степенью точности определяются из соотношений

2- i 2п+Т

U5m

2- I

2 2

-±-Ј- 2-2+1

Т2+Г U5m MU,;

U « U6m 0,8 U5m;

ит Т2п+п ггйТу

0,04 U

sms

где U 6m - максимальная амплитуда сигнала на выходе датчика 5, наблюдаемая на низшей выходной частоте преобразователя.

Амплитуда постоянного напряжения источника 23 определяется из соотношения

U

U

w зт 5т л 9 тт

2п+тгг г и5™

Коэффициент передачи усилителя 10 К,0 равен двум.

, Временные диаграммы, приведенные на фиг.2, соответствуют нижнему частотному диапазону работы инвертора, когда полуволна его линейного выходного напряжения UAa формируется из максимального на полупериоде количества импульсов, равного одиннадцати, с минимальными длительностями,задаваемыми, как было упомянуто выше, величиной напряжения источника 7. - Из-за того, что 2, продолжительность центральных на полупериоде импульсов в кривой линейного выход5 ного напряжения в два раза превышает продолжительность равных между собой остальных выходных импульсов.

Формирование фронтов импульсов кривой выходного сигнала инвертора

Q с данной системой управления производится блоком 6 формирования дли- ; тельностей импульсов в моменты равенства сигнала генератора 4 развертывающего напряжения величине напряже5 ний , U,, , U8, и,а и U9, снимаемых соответственно с выходов усилителя 10 и сумматоров 11,8,12 и 9,передаваемых через блок 15 на соответствующие входы блока 6 формирования,

0 выходной сигнал которого обозначен на фиг.2, как U6.

Основной функцией блока 15 является обеспечение на всем диапазоне регулирования гарантированной величины межкоммутационных интервалов между соседними коммутациями вентилей силовой схемы, что обеспечивает коммутационную устойчивость инвертора при регулировании. Это достигаетQ ся путем постоянного сопоставления продолжительностей временных интервалов между моментами переключения вентилей с опорной граничной величиной, эквивалентом которой является

5 напряжение вспомогательного источника 18 и видоизменения алгоритма дальнейшей подачи управляющих сигналов на блок 6 в случае уменьшения указанных продолжительностей ниже граничQ ных значений. Один из возможных вариантов построения связанных между собой блоков 15 и 6 приведен на фиг.3 о

Основные входы блока 15 обеспечес ния коммутационной устойчивости,количество которых в общем случае равно 2п, связаны с выходами опорных сумматоров 8,11,9 и 12. Указанные входные клеммы через ключи 25-28 соеди5

иены с соответствующими основными выходами блока 15. Выходы блока 15, к которым подсоединены выходы усилителей 8 и 9, связаны также с первыми входами схем 29 и 30 сравнения, два других основных входа присоединены к сумматорам 31 и 32, выходы которых, в свою очередь, подключены к йходам схем 33 и 34 сравнения. Выход Схемы 33 присоединен к управляющей цепи ключа 26, а также к входу элемента И 35, второй вход которого свя- фан с инверсным выходом блока 29 Сравнения. Выход схемы 34 сравнения йоединен с управляющей цепью ключа 8 и с входом элемента И 36,второй фход которого подключен к инверсному выходу схемы 30 сравнения. Прямые Йыходы схем 29 и 30 соединены с управляющими цепями ключей 25 и 27. На вторые входы всех схем сравнения блока 15 поступает сигнал с выхода сумматора 19. Вторые входы сумматоров 31 и 32 связаны с источником 18 вспомогательного напряжения.

Блок 6 формирования длительности импульсов включает в свой состав Входные компараторы 37-41 (число компараторов в общем случае равно (2п+ + 1), на выходе которых имеются формирователи коротких однополярных импульсов. Входы компараторов 37 - ДО при этом связаны с основными выходами блока 15, вход компаратора 41 присоединен к выходной клемме ключа 20. На другие входы компараторов 37-41 поступает сигнал U. генератора 4 развертывающего напряжения. Выходы компараторов 37-41 через элемент ИЛИ 42 подключены к входу счетного триггера 43, выходное напряжение которого является выходным сигналом блока 6 формирования. При этом продолжительность выходного сигнала Ц, блока 6, как показано на фиг.2, равна продолжительности импульсов кривой выходного напряжения инвертора на данном интервале.

Увеличение выходной частоты инвертора в процессе регулирования сопровождается последовательным уменьшением амплитуды развертывающего сигнала Uy, выделяемой датчиком 5 амплитуды. Сигнал датчика 5 за вычетом напряжения источника 18, пропорционального величине минимальной межкоммутационной паузы, постоянно сравнивается на входах схем 29-30 и 33-34

сравнения с выходными сигналами сумматоров 8-9 и 31-32, определяющими моменты формирования фронтов выходных импульсов. В случае равенства указанных сигналов, что наблюдается при повышении выходной частоты, во избежание срыва коммутации выходных импульсов, командные сигналы с выходов

схем 30,34,29 и 33 сравнения вызывают последовательное размыкание ключей 27,28,25 и 26, прекращающих подачу соответствующих сигналов на входы компараторов 37-40. С ростом вы5 ходной частоты в кривой выходного напряжения инвертора при этом наблюдается последовательное уменьшение количества импульсов.

Одновременно изменение сигналов

0 на выходах схем 29-30,33,34 сравнения приводит к прохождению сигналов на вспомогательные выходы блока 15 через элемент И 36 (что имеет место, когда U(, a ) или через

5 элемент И 35 (наблюдаемое при Ug c

0

5

14

U

31

и19).

Отмеченным режи0

5

0

5

мам работы соответствует формирование выходных импульсов в центральной части тактовых интервалов.

Указанные команды через элемент ИЛИ 16 поступают на управляющий вход ключа 20 и вызывают его периодическое замыкание, благодаря чему сигнал датчика 5 амплитуды пилообразного напряжения периодически поступает на плюсовой вход сумматора 21. На остальные входы сумматора 21 при этом приходят11 сигналы, снимаемые с основных выходов блока 15 (с выходных клемм ключей 25-28 блока 15) и с выходной клеммы ключа 20. Благодаря отмеченной полярности входов сумматора 21 на выходе его на всем диапазоне регулирования формируется сигнал, величина которого пропорциональна суммарной длительности импульсов на полупериоде выходного напряжения инвертора. Указанное напряжение U2 поступает на минусовой вход интегратора 22, плюсовой вход которого соединен с источником 23 постоянного напряжения, величина напряжения которого эквивалентна суммарной продолжительности выходных импульсов на полупериоде выходной кривой на начальной выходной частоте инвертора.

В связи с этим выходной сигнал интегратора 22 на начальной выходной частоте равен нулю. При увеличении

915

выходной частоты инвертора нулевой сигнал на выходе интегратора 22 сохраняется до момента исчезновения сигнала с первого из основных выходов блока 15 и соответственно первого замыкания ключа }7. Результирующий сигнал на выходе сумматора 21 после этого момента времени становится меньше напряжения источника 23,проинтегрированный положительный разностный сигнал поступает с выхода блока 22 на плюсовые входы сумматора 8 и усилителя 10, вызывая соответствующее увеличение продолжитель- ностей оставшихся в полуволне выходной кривой девяти выходных импульсов Данный поддиапазон регулирования характерен формированием выходных импульсов в центрах тактовых интервалов 60-градусных продолжительнос- тей, длительность которых уменьшается при повышении частоты, в связи с чем положительный сигнал с выхода интегратора 22 будет при росте частоты последовательно увеличивать продолжительность остальных импульсов выходной кривой. Поддержание постоянства величины суммарной длительности

выходных импульсов в полуволне линей- 30 амплитуда сигнала U10 не сравняетного выходного напряжения при изменении частоты и при неизменных амплитудах импульсов соответствует закону линейного изменения величины среднего на полупериоде значения выходного напряжения инвертора1, наиболее часто реализуемому в системах частотно-регулируемого электропривода. Основная гармоника выходного напряженияизменяется при этом также по закону,близкому к линейному. Наличие интегратора 22 в цепи обратной связи обеспечивает астатический характер процесса регулирования, повышая тем самым его точность.

Абсолютное значение положения фронтов выходных импульсов, задаваемых сигналами сумматоров И и 12, по отношению к началу тактовых интервалов в процессе регулирования остается неизменным, изменение продолжи- тельностей выходных импульсов происходит за счет смещения других фронтов, формируемых при помощи сигналов сумматора 8 и усилителя 10. Это свойство схемы позволяет значительно снизить количество дополнительных коммутаций силовых ключей инвертора в области повышенных частот, близких

0

700

5

0

5

10

к номинальной выходной частоте по сравнению с количеством коммутации при алгоритме управления, осуществляемом известным устройством, при котором регулирование величины выходного напряжения производится пропорциональным перемещением обоих фронтов выходных импульсов вплоть до верхней выходной частоты.

На фиг.4 изображены временные диаграммы, показывающие работу системы управления преобразователем в об- ласТи повышенных выходных частот, когда U5 « U . При этом на всех основных вспомогательных выходах блока 15 сигналы отсутствуют, полуволна выходного напряжения, как показано на фиг.4а, формируется из трех импульсов, фронты которых задаются неизменным по величине сигналом U10 с выхода усилителя 10. Разностный интегральный сигнал корректирующей цепи обратной связи с выхода блока

22 на этом поддиапазоне регулирования равен нулю.

Описанный алгоритм работы схемы сохраняется до тех пор, пока в процессе дальнейшего повышения частоты

5

0

5

0

5

ся с величиной напряжения U на выходе сумматора 19, после чего сигнал с выхода схемы 24 сравнения размыкает ключ 20. Указанному моменту (фиг.46) соответствует номинальное значение выходной частоты преобразователя, величина выходного напряжения при этом является максимальной и при дальнейшем повышении частоты остается на этом уровне. Сигналы на выходе блока 6 в этом режиме отсутствуют, лишь на тактовые входы распределителя 3 поступают сигналы с выходов регистра 2.

Трехразрядный регистр 2 системы управления, выполняющий функции пересчетной схемы, осуществляет деление частоты следования импульсов, поступающих от генератора 1 тактовых импульсов, и распределение сигналов во времени (фазовый сдвиг сигналов). В цифровой форме состояния выходов Qg Q Qf регистра 2, начиная со старшего разряда, за период выходного напряжения можно последовательно записать как 100, 00, 000, 101, ПО, 111 (сигнал U Ј на фиг.2).

Логический распределитель 3 управляющих импульсов формирует трехфазную систему импульсов, соответствующую требуемому порядку переключения вентилей силовой схемы инвертора. Распределитель 3, осуществляющий режим 180-градусного управления ключами трехфазного мостового инвертора с фазами А,В,С с дополнительными коммутациями на средних 60-градусных участках (тактовых интервалах), при котором форма кривой выходного напря- жфния на всем диапазоне регулирования ни зависит от параметров нагрузки, представляет собой логическую схему, вiкоторой осуществляется логическое уложение входных сигналов с последующим логическим суммированием.Логи- чфские функции, реализуемые распределителем 3 и поступающие в форме сигналов управления на соответствующие вентили, имеют следующий вид

-А « Q4Q3 + Q4U6 + Q2U6; +В Q,Q3 + Q,QU + Q,Q6 -f + Q«QaQ U6; +C QjQj + §,UC + Q2U6.

Импульсы управления на другие вен- соответствующих фаз инвертора (+А, -В, -С) получаются логическим инвертированием соответствующих фазных сигналов на выходе распределите- 3. Форма кривой выходного напряжения инвертора при таком алгоритме Управления не зависит от параметров йагрузки, средняя частота коммутации вентилей близка к постоянному значению.

Таким образом, благодаря тому,что .регулирование величины напряжения инвертора осуществляется за счет изменения временного положения одного из фронтов выходных импульсов при неизменном положении другого фронта, а также за счет исключения связи ло гического узла, содержащего ключ 17 и элемент ИЛИ 16, с входом блока 6 формирования длительностей импульсов j достигается заметное снижение числа коммутаций силовых вентилей инвертора, с соответствующим уменьшением величины коммутационных потерь. Особенно указанное снижение потерь заметно в диапазоне повышенных выходных частот, в области близких к номи- нальной нагрузок системы частотно- регулируемого электропривода, в которой преобразовательные устройства

0

5

0

5

о

5

45

работают, как правило, наиболее долго. Для приведенного на фиг.1 варианта структуры системы управления отмеченный диапазон начинается с момента равенства сигналов

U5 и U,, U,5 - UT

0,4U6m - 0,04U5rn 0,36U5m. i

Это соответствует тому, что при п 2 на протяжении примерно верхней трети от всего диапазона регулирования инвертора число коммутаций вентилей каждой фазы на полупериоде уменьшается с 10 (при алгоритме управления устройства) до 6 (при алгоритме работы предлагаемого устройства) с соответствующим почти двукратным снижением величины коммутационных потерь в преобразовательной системе.

Формула изобретения

Устройство для управления трехфазным регулируемым инвертором,содержащее источник опорного напряжения, п основных и вспомогательных источников постоянного напряжения, генератор тактовых импульсов, соединенный с трехразрядным регистром, связанным выходами с тактовыми входами распределителя управляющих импульсов, и с генератором пилообразного напряжения, связанным с датчиком амплитуды пилообразного напряжения и с основным входом (2п+2)-входового блока формирования длительностей импульсов, выход которого присоединен к основному входу распределителя управляющих импульсов, (2п+2) сумматоров, плюсовой вход первого из которых связан с выходом датчика амплитуды пилообразного напряжения, а минусовой вход - с вспомогательным источником постоянного напряжения, первые плюсовые входы четных сумматоров и минусовые входы остальных нечетных сумматоров связаны с выходом источника опорного напряжения, вторые плюсовые входы всех сумматоров, кроме первого, соединены попарно с основными источниками постоянного напряжения, выходы сумматоров и выход источника вспомогательного напряжения подключены к соответствующим основным входам (2п+2) входо- вого блока обеспечения коммутационной устойчивости, состоящего из двух

групп узлов сравнения по п узлов в каждой, из п сумматоров, п элементов И и 2п управляемых ключей, при этом основные входы указанного блока через соответствующие управляемые ключи связаны с входами блока формирования длительностей импульсов, четные основные входы указанного блока связаны с первыми входами первой группы узлов сравнения,нечетные входы подключены к первым входам сумматоров, вторые входы которых связаны с источником вспомогательного напряжения, а выходы которых присоединены к первым входам узлов сравнения второй группы, вторые входы всех узлов сравнения подсоединены к выходу первого основного сумматора, прямые выходы узлов сравнения первой группы присоединены к управляющим цепям четных ключей блока обеспечения коммутационной устойчивости,инверсные выходы этих узлов связаны с первыми входами соответствующих элементов И, прямые выходы узлов сравнения второй группы подключены к вторым входам соответствующих элементов Ник управляющим цепям нечетных ключей, выходы элементов И через элемент ИЛИ связаны с управляющей цепью основного ключа,о т л и- чающееся тем, что, с целью уменьшения коммутационных потерь в инверторе в процессе связанного регулирования частоты и величины выходного напряжения, оно снабжено интегратором с двумя суммирующими входа% %

0

5

0

5

0

5

ми, многовходовым сумматором,блоком сравнения, дополнительным управляемым ключом, дополнительным источником постоянного напряжения и суммирующим усилителем постоянного тока, причем первый вход суммирующего усилителя постоянного тока соединен с выходом источника опорного напряжения, выход суммирующего усилителя связан с первым входом блока сравнения, и через дополнительный ключ с (2п+2)-м входом блока формирования длительностей импульсов, второй вход блока сравнения присоединен к выходу первого основного сумматора, выход блока сравнения связан с управляющей цепью дополнительного ключа,выход датчика амплитуды пилообразного напряжения присоединен к входной клемме основного ключа, выходные клеммы обоих ключей и нечетные основные выходы блока обеспечения коммутационной устойчивости соединены с плюсовыми входами дополнительного сумматора, четные основные выходы блока обеспечения коммутационной устойчивости связаны с минусовыми входами дополнительного сумматора, выход этого сумматора присоединен к минусовому входу интегратора,плюсовой вход которого связан с дополнительным источником постоянного напряжения, а выход интегратора присоединен к второму входу суммирующего усилителя и к третьим плюсовым входам всех четных основных сумматоров, кроме последнего.

Фиг. г

м„

/V

НагЮтЮОт

О Q

Фиг.4

| Устройство для управления автономным регулируемым инвертором | 1985 |

|

SU1272430A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для управления регулируемым мостовым инвертором | 1987 |

|

SU1432699A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-01-07—Публикация

1988-02-01—Подача