Предлагаемое изобретение относится к способам детектирования (демодуляции) сигналов с магнитных носителей внешних запоминающих устройств и детекторам для их осуществления.

В настоящее время внешние запоминающие устройства на магнитных носителях широко используются в компьютерах, регистраторах данных, информационно-поисковых системах, суперкомпьютерах (накопители на магнитных дисках, накопители на магнитных лентах). Несмотря на повышение параметров твердотельных накопителей информации и запоминающих устройств на иных физических принципах неэлектромеханического типа, выполняющих функциональную роль внешних запоминающих устройств, электромеханические устройства, использующие магнитные носители информации, будут занимать свой сектор рынка ввиду присущих им преимуществ: высокой поверхностной плотности информации, низкой стоимости хранения информации, устойчивости к внешним воздействиям.

В течение длительного времени во внешних запоминающих устройствах широко использовалось пиковое детектирование, обеспечивая высокую достоверность воспроизведения данных и относительную простоту аппаратных решений. Суть пикового детектирования состоит в том, что воспроизводимый отклик на перепад намагниченности, имеющий колоколообразную форму положительной или отрицательной полярности с одним экстремумом на интервале одного бита, аналогово дифференцируется, а в продифференцированном сигнале определяется переход через ноль (точнее через небольшой порог в несколько процентов от амплитуды продифференцированного сигнала). Наличие перехода через ноль интерпретируется как единица в данном бите. При номинальных значениях параметров тракта воспроизведения и относительно низком уровне межсимвольной интерференции выходной сформированный импульс находится в центре бита, что важно, как в многоканальных, так и одноканальных внешних запоминающих устройствах. С целью упрощения устройства отклики положительной и отрицательной полярности перед аналоговым дифференцированием предварительно выпрямляются. Такой способ и устройство рассмотрены в статье Шувалов Л.Н. «Модернизация накопителя на магнитной ленте машины. М. - 220 - М:, Вопросы технической эксплуатации вычислительных машин, Вып. III вычислительный центр АН СССР, 1973» (с. 43-53), принятые за аналог предлагаемого детектора. Детектор содержит усилитель, вход которого связан с выходом магнитной головки воспроизведения, выход усилителя связан со входом фазоинвертора, парафазные выходы которого связаны со входом дифференцирующего каскада, выход которого связан со входом формирующего каскада, выход которого связан с устройством управления накопителя на магнитной ленте.

Недостатком пикового детектирования с аналоговым дифференцированием является формирование ложных переходов через ноль вследствие сложения аддитивного шума с суперпозицией откликов на участках с медленным изменением сигнала. Типовым, средством против этого являлось формирование строба из самого отклика на таком его уровне, что изменения сигнала достаточно быстрые и строб занимает некоторый интервал в центре бита, а в качестве единицы воспринимаются те переходы через ноль, которые попадают в строб «Shang X. Wang, Alex M. Taratorin Magnetic information storage technology. - Academic Press, 525 В Street, Suite 1900, San Diego, California 92101- 4495, USA, 1998. - 536p,: ISBN 0-12-734570-1» (c.346, 381), принятое также за аналог предлагаемого детектора. Детектор содержит усилитель, вход которого связан с выходом магнитной головки воспроизведения, выход усилителя связан со входом выпрямителя, выход которого связан со входом формирователя строба и параллельно со входом дифференцирующего каскада, выход которого связан со входом двухвходовой схемы совпадения, второй вход которой связан с выходом формирователя строба, выход двухвходовой схемы совпадения связан с контроллером внешнего запоминающего устройства. Такой подход обеспечивает достоверность 108 при относительной продольной плотности PW50/T, равной 1,33 (плотность пользователя). Однако он имеет тот недостаток, что при действии мультипликативной помехи (ухудшении номинальных параметров тракта воспроизведения) строб исчезает, что ведет к пропаданию «единицы».

Мешающими факторами в аналогах являются линейный сдвиг позиции экстремумов из-за межсимвольной интерференции, мультипликативной и аддитивной помех и неидеальной самосинхронизации.

В современных внешних запоминающих устройствах общепринятым способом детектирования является PRML (Partial Response Maximum Likelihood) «Shang X. Wang, Alex M. Taratorin Magnetic information storage technology. - Academic Press, 525 В Street, Suite 1900, San Diego, California 92101 - 4495, USA,1998. - 536p,:ISBN 0-12-734570-1» (c.362), принятый в качестве прототипа. PRML учитывает изменение отсчета в центре некоторого бита за счет интерференции с некоторыми соседними откликами в предположении, что основные параметры тракта воспроизведения неизменны, т.е. вклад учитываемых интерферирующих откликов наперед известен. Такой подход позволяет повысить относительную продольную плотность примерно на 30 процентов по сравнению с пиковым детектированием «Shang X. Wang, Alex M. Taratorin Magnetic information storage technology. - Academic Press, 525 В Street, Suite 1900, San Diego, California 92101 - 4495, USA,1998. - 536p,:ISBN 0-12-734570-1» (c.381). В PRML для поиска наиболее правдоподобных канальных кодов используется детектор Витерби, представляющий из себя специализированный процессор и реализуемый на чипе со сверхбольшой степенью интеграции. В детекторе Витерби используются абсолютные отсчеты для определения состояний в решетчатой диаграмме, отражающей разрешенные канальные коды и их связь с идеальными отсчетами. Таким образом, PRML хорошо работает при высоком уровне межсимвольной интерференции, но не отрабатывает мультипликативную помеху, связанную с микродефектами запоминающего слоя, износом последнего, попаданием чужеродных частиц между головкой и носителем. Мультипликативная помеха вызывает пакетную ошибку, т.е. нежелательные изменения сигнала в серии последовательных бит. Пакетная ошибка локализуется и исправляется с помощью кодов Рида-Соломона в пределах корректирующей мощности кода, что существенно увеличивает время считывания.

PRML детектор, принятый в качестве прототипа предлагаемого детектора, содержит усилитель, вход которого связан с выходом магнитной головки воспроизведения, выход усилителя связан со входом эквалайзера (фильтра, сужающего входной отклик), и параллельно связан со входом формирователя синхроимпульсов, выход эквалайзера связан со входом аналого-цифрового преобразователя (АЦП), вход АЦП, определяющий момент квантования, связан с выходом формирователя синхроимпульсов, выход АЦП связан со входом детектора Витерби, содержащего блок вычисления метрик ветвей, блок суммирования метрик, сравнения с эталонными, выбора наиболее правдоподобных состояний, блок хранения эталонных данных решетчатой диаграммы и текущих данных.

Основными недостатками прототипа способа и прототипа детектора является низкая помехоустойчивость при действии мультипликативной помехи и высокая вычислительная мощность, требуемая для работы.

Решаемая техническая задача в способе детектирования сигналов с магнитного носителя информации, записанных RLL кодами и детекторе для его осуществления, заключается в повышении помехоустойчивости при действии мультипликативной помехи и снижении требуемой вычислительной мощности, путем упрощения алгоритма обработки сигнала, при несущественном падении помехоустойчивости при действии аддитивной помехи.

Технический результат предлагаемого способа детектирования сигналов с магнитного носителя информации, записанных RLL кодами и детекторе для его осуществления, заключается в более высокой помехоустойчивости при действии мультипликативной помехи и меньшей требуемой вычислительной мощности по сравнению с прототипом, при незначительном ухудшении помехоустойчивости при действии аддитивной помехи.

Технический результат предлагаемого способа детектирования сигналов с магнитного носителя информации, записанных RLL кодами, включающем усиление сигнала, воспроизведенного с магнитного носителя информации с помощью магнитной головки воспроизведения, на усилителе, формирование из усиленного сигнала синхроимпульсов в моменты времени соответствующие центрам бит канального кода, параллельно формированию синхроимпульсов выравнивание усиленного сигнала на эквалайзере, преобразование усиленного сигнала на АЦП заданной разрядности в цифровые отсчеты в моменты времени, определяемые синхроимпульсами, достигается тем, что синхроимпульсы сразу после формирования подают на вход блока синхронизации, в котором с приходом каждого синхроимпульса формируют временной цикл работы детектора, состоящий из заданного числа импульсов, отстоящих друг от друга на период, по крайней мере, на порядок меньший, чем период синхроимпульсов, цифровые отсчеты с выхода АЦП параллельно подают на блок сравнения отсчетов, на котором производят вычитание предыдущего отсчета из текущего и восстановление текущего отсчета после передачи знака результата вычитания, сигналом с единичного выхода триггера знака результата вычитания блока сравнения отсчетов, пропущенным через двухвходовую схему совпадения, устанавливают в «1» триггер «больше», сигналом с нулевого выхода триггера знака результата вычитания блока сравнения отсчетов, пропущенным через двухвходовую схему совпадения, устанавливают в «1» триггер «меньше», на вторые входы двухвходовых схем совпадения подается соответствующий импульс временного цикла работы детектора с блока синхронизации, сигналы с единичного выхода триггера «больше» подают последовательно после каждого вычитания на входной триггер первого сдвигового регистра разрядностью (d+1), где d есть d-ограничение RLL кода и может принимать значения от 0 до 4, сигналы с единичного выхода триггера «меньше» подают последовательно после каждого вычитания на входной триггер второго сдвигового регистра разрядностью (d+1), предварительно соответствующим импульсом временного цикла работы детектора с блока синхронизации производят сдвиг содержимого первого и второго сдвиговых регистров разрядностью (d+1) на один в сторону старших разрядов, единичные выходы триггеров первого сдвигового регистра разрядностью (d+1) подают на соответствующие входы первой схемы совпадения с (d+2) входами, на (d+2) вход которой подают соответствующий импульс временного цикла работы детектора с блока синхронизации, выход первой схемы совпадения с (d+2) входами подают на установку в «1» триггера «все больше», единичные выходы триггеров второго сдвигового регистра разрядностью (d+1) подают на соответствующие входы второй схемы совпадения на (d+2) входов, на (d+2) вход которой подают соответствующий импульс временного цикла работы детектора с блока синхронизации, выход второй схемы совпадения на (d+2) входов подают на установку в «1» триггера «все меньше», сигнал с единичного выхода триггера «все больше» подают на первую трехвходовую схему совпадения, на второй вход которой подают сигнал с нулевого выхода триггера «все меньше раньше», а на третий вход подают соответствующий импульс временного цикла работы детектора с блока синхронизации, сигналом с выхода первой трехвходовой схемы совпадения устанавливают в состояние «1» триггер «все больше раньше», сигнал с единичного выхода триггера «все меньше» подают на вторую трехвходовую схему совпадения, на второй вход которой подают сигнал с нулевого выхода триггера «все больше раньше», а на третий вход подают соответствующий импульс временного цикла работы детектора с блока синхронизации, сигналом с выхода второй трехвходовой схемы совпадения устанавливают в состояние «1» триггер «все меньше раньше», сигнал «1» канального кода вырабатывают на третьей трехвходовой схеме совпадения, на один вход которой подают сигнал с единичного выхода триггера «все больше», на второй вход подают сигнал с единичного выхода триггера «все меньше раньше», а на третий вход подают соответствующий импульс временного цикла работы детектора с блока синхронизации, сигнал «1» канального кода вырабатывают также на четвертой трехвходовой схеме совпадения, на один вход которой подают сигнал с единичного выхода триггера «все меньше» на второй вход подают сигнал с единичного выхода триггера «все больше раньше», а на третий вход подают соответствующий импульс временного цикла работы детектора с блока синхронизации, сигналом с выхода третьей трехвходовой схемы совпадения сбрасывают в «0» второй сдвиговый регистр разрядностью (d+1), триггер «все больше» и триггер «все меньше раньше», сигналом с выхода четвертой трехвходовой схемы совпадения сбрасывают в «0» первый сдвиговый регистр разрядностью (d+1), триггер «все меньше» и триггер «все больше раньше», сигналы «1» канального кода с выхода третьей трехвходовой схемы совпадения и с выхода четвертой трехвходовой схемы совпадения объединяют на двухвходовой схеме «ИЛИ», выходной сигнал «1» канального кода которой подают через двухвходовую схему совпадения, на второй вход которой подают сигнал с нулевого выхода триггера «короткий цикл», на установку в «1» триггера выходного сдвигового регистра разрядностью L, где L - число бит в канальном коде и может принимать значения от 10 до 4097, расположенного на позиции (d+1) относительно младшего разряда выходного сдвигового регистра разрядностью L, код на котором сдвигают на один сторону старших разрядов с приходом соответствующего импульса каждого временного цикла работы детектора с блока синхронизации, синхроимпульсы с выхода формирователя синхроимпульсов подают на счетчик числа импульсов канального кода до L через двухвходовую схему совпадения, на второй вход которой подают сигнал с единичного выхода триггера «разрешение счета числа канальных импульсов», на вход установки в «1» последнего подают сигнал «начало сектора», а на вход сброса в «0» подают сигнал «конец сектора» с контроллера внешнего запоминающего устройства, синхроимпульсы с выхода формирователя синхроимпульсов подают на первый счетчик числа импульсов канального кода до (d+1) через двухвходовую схему совпадения, на второй вход которой подают сигнал с единичного выхода триггера «короткий цикл», на установку в «1» которого подают выход счетчика числа импульсов канального кода до L, а на установку в «0» выходной сигнал первого счетчика числа импульсов канального кода до (d+1), задержанный на двух последовательных инверторах, синхроимпульсы с выхода формирователя синхроимпульсов подают на второй счетчик числа импульсов канального кода до (d+1) через двухвходовую схему совпадения на второй вход которой подают сигнал с единичного выхода триггера «счет позиции «1»» на установку в «1», которого подают выход счетчика числа импульсов канального кода до L, а на установку в «0» выходной сигнал двухвходовой схемы «ИЛИ» «1» канального кода, единичный выход триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) подают на один из входов первой схемы совпадения с (d+1) входами, на другие (d-1) входов подают соответствующие нулевые выходы триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), а на (d+1) вход подают выходной сигнал первого счетчика числа импульсов канального кода до (d+1), выходной сигнал первой схемы совпадения с (d+1) входами подают на установку в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на d позиций относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, нулевой выход триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) подают на один из входов второй схемы совпадения с (d+1) входами, единичный выход триггера следующего за младшим разряда второго счетчика числа импульсов канального кода до (d+1) подают на один из входов второй схемы совпадения с (d+1) входами на другие (d-2) входов подают соответствующие нулевые выходы триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), а на (d+1) вход подают выходной сигнал первого счетчика числа импульсов канального кода до (d+1), выходной сигнал второй схемы совпадения с (d+1) входами подают на установку в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на (d-1) позицию относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, единичные выходы триггеров младшего разряда и следующего за ним разряда второго счетчика числа импульсов канального кода до (d+1) подают на соответствующие входы третьей схемы совпадения с (d+1) входами, на другие (d-2) входов подают соответствующие нулевые выходы триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), а на (d+1) вход подают выходной сигнал первого счетчика числа импульсов канального кода до (d+1), выходной сигнал третьей схемы совпадения с (d+1) входами подают на установку в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на (d-2) позиции относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, выходной сигнал двухвходовой схемы «ИЛИ» «1» канального кода подают также на вход М-разрядного счетчика веса канального кода, где M соответствует максимально возможному весу данного RLL кода и может принимать значения от 2 до 32, выходной сигнал первого счетчика числа импульсов канального кода до (d+1), задержанный на двух последовательных инверторах подают на один из входов L выходных двухвходовых схем совпадения, на вторые входы которых подают сигналы с единичных выходов соответствующих триггеров выходного сдвигового регистра разрядностью L, выходная кодовая комбинация с выходов указанных двухвходовых схем совпадения подается на контроллер внешнего запоминающего устройства, сигналы с единичных и нулевых выходов триггеров М-разрядного счетчика веса канального кода подают на первый из входов M соответствующих двухвходовых схем совпадения в соответствии со всеми недопустимыми значениями веса канального кода, на вторые из входов которых подают выходной сигнал первого счетчика числа импульсов канального кода до (d+1), задержанный на двух последовательных инверторах, выходные сигналы указанных выше M двухвходовых схем совпадения объединяют на М-входовой схеме «ИЛИ», выходной сигнал которой подают на установку в «1» триггера «стертый», который сбрасывают в «0» выходным сигналом первого счетчика числа импульсов канального кода до (d+1), задержанным на двух последовательных инверторах, выходной сигнал триггера «стертый» подается на вход контроллера внешнего запоминающего устройства, сигнализирующий о стертости текущего канального кода.

Технический результат в детекторе сигналов с магнитного носителя информации, записанных RLL кодами, содержащем усилитель, вход которого соединен с выходом магнитной головки воспроизведения, выход усилителя соединен со входом формирователя синхроимпульсов, и со входом эквалайзера, выход эквалайзера соединен со входом АЦП, вход которого, определяющий частоту квантования, соединен с выходом формирователя синхроимпульсов, достигается тем, что выходы АЦП соединены со входами блока сравнения отсчетов, другой вход которого соединен с соответствующим выходом блока синхронизации, прямой выход знакового разряда блока сравнения отсчетов соединен со входом двухвходовой схемы совпадения, второй вход которой соединен с соответствующим выходом блока синхронизации, выход двухвходовой схемы совпадения соединен со входом установки в «1» триггера «больше», инверсный выход знакового разряда блока сравнения отсчетов соединен со входом двухвходовой схемы совпадения, второй вход которой соединен с соответствующим выходом блока синхронизации, выход двухвходовой схемы совпадения соединен со входом установки в «1» триггера «меньше», единичный выход триггера «больше» соединен со входом установки в «1» триггера первого сдвигового регистра разрядностью (d+1), где d есть d-ограничение RLL кода и может принимать значения от 0 до 4, единичный выход триггера «меньше» соединен со входом второго сдвигового регистра разрядностью (d+1), входы управления цепями сдвига на 1 к старшим разрядам первого и второго сдвиговых регистров разрядностью (d+1) соединены с соответствующим выходом блока синхронизации, единичные выходы триггеров первого сдвигового регистра разрядностью (d+1) соединены с соответствующими входами первой схемы совпадения с (d+2) входами, (d+2) вход которой соединен с соответствующим выходом блока синхронизации, выход первой схемы совпадения с (d+2) входами соединен со входом установки в «1» триггера «все больше», единичные выходы триггеров второго сдвигового регистра разрядностью (d+1) соединены с соответствующими входами второй схемы совпадения с (d+2) входами, (d+2) вход которой соединен с соответствующим выходом блока синхронизации, выход второй схемы совпадения с (d+2) входами соединен со входом установки в «1» триггера «все меньше», единичный выход триггера «все больше» соединен со входом первой трехвходовой схемы совпадения, второй вход которой соединен с нулевым выходом триггера «все меньше раньше», а третий вход соединен с соответствующим выходом блока синхронизации, выход первой трехвходовой схемы совпадения соединен со входом установки в «1» триггера «все больше раньше», единичный выход триггера «все меньше» соединен со входом второй трехвходовой схемы совпадения, второй вход которой соединен с нулевым выходом триггера «все больше раньше», третий вход соединен с соответствующим выходом блока синхронизации, выход второй трехвходовой схемы совпадения соединен со входом установки в «1» триггера «все меньше раньше», единичный выход триггера «все больше» соединен со входом третьей трехвходовой схемы совпадения, второй вход которой соединен с единичным выходом триггера «все меньше раньше», а третий вход соединен с соответствующим выходом блока синхронизации, единичный выход триггера «все меньше» соединен со входом четвертой трехвходовой схемы совпадения, второй вход которой соединен с единичным выходом триггера «все больше раньше», а третий вход соединен с соответствующим выходом блока синхронизации, выход третьей трехвходовой схем совпадения соединен со входом установки в «0» второго сдвигового регистра разрядностью (d+1), триггера «все больше» и триггера «все меньше раньше», выход четвертой трехвходовой схемы совпадения соединен со входом сброса в «0» первого сдвигового регистра разрядностью (d+1), триггера «все меньше» и триггера «все больше раньше», выходы третьей и четвертой трехвходовой схем совпадения соединены со входами двухвходовой схемы «ИЛИ», выход которой «1 канального кода» соединен со входом двухвходовой схемы совпадения, второй вход которой соединен с нулевым выходом триггера «короткий цикл», выход двухвходовой схемы совпадения соединен со входом установки в «1» триггера выходного сдвигового регистра разрядностью L, где L - число бит в канальном коде и может принимать значения от 10 до 4097, сдвинутого на (d+1) разрядов относительно младшего разряда, вход управления цепями сдвига на 1 к старшим разрядам выходного сдвигового регистра разрядностью L соединены с соответствующим выходом блока синхронизации, выход формирователя синхроимпульсов соединен со входом счетчика числа импульсов канального кода до L через двухвходовую схему совпадения, второй вход которой соединен с единичным выходом триггера «разрешение счета числа канальных импульсов», вход установки в «1» которого является входом подачи сигнала «начало сектора» с контроллера внешнего запоминающего устройства, а вход сброса в «0» является входом подачи сигнала «конец сектора» с контроллера внешнего запоминающего устройства, выход формирователя синхроимпульсов соединен со входом первого счетчика числа импульсов канального кода до (d+1) через двухвходовую схему совпадения, второй вход которой соединен с единичным выходом триггера «короткий цикл», вход установки в «1» которого соединен с выходом счетчика числа импульсов канального кода до L, а вход установки в «0» которого соединен с выходом двух последовательных инверторов, вход первого из них соединен с выходом первого счетчика числа импульсов канального кода до (d+1), выход формирователя синхроимпульсов соединен со входом второго счетчика числа импульсов канального кода до (d+1), через двухвходовую схему совпадения, второй вход которой соединен с единичным выходом триггера «счет позиции «1»», вход установки в «1» которого соединен с выходом счетчика числа импульсов канального кода до L, а вход сброса в «0» которого соединен с выходом двухвходовой схемы «ИЛИ» «1» канального кода, единичный выход триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) соединен с одним из входов первой схемы совпадения с (d+1) входами, другие (d-1) входов соединены с соответствующими нулевыми выходами триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), a (d+1) вход соединен с выходом первого счетчика числа импульсов канального кода до (d+1), выходной сигнал первой схемы совпадения с (d+1) входами соединен со входом установки в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на d позиций относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, нулевой выход триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) соединен с одним из входов второй схемы совпадения с (d+1) входами, единичный выход триггера следующего за младшим разряда второго счетчика числа импульсов канального кода до (d+1) соединен с другим входом второй схемы совпадения с (d+1) входами, другие (d-2) входов соединены с соответствующими нулевыми выходами триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), a (d+1) вход соединен с выходом первого счетчика числа импульсов канального кода до (d+1), выход второй схемы совпадения с (d+1) входами соединен со входом установки в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на (d-1) позицию относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, единичные выходы триггеров младшего разряда и следующего за ним разряда второго счетчика числа импульсов канального кода до (d+1) соединены с соответствующими входами третьей схемы совпадения с (d+1) входами, другие (d-2) входов соединены с соответствующими нулевыми выходами триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), a (d+1) вход соединен с выходом первого счетчика числа импульсов канального кода до (d+1), выходной сигнал третьей схемы совпадения с (d+1) входами соединен со входом установки в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на (d-2) позиции относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, выход «1» канального кода двухвходовой схемы «ИЛИ» соединен со входом М-разрядного счетчика веса канального кода, где M соответствует максимально возможному весу данного RLL кода и может принимать значения от 2 до 32, выход первого счетчика числа импульсов канального кода до (d+1), задержанный на двух последовательных инверторах, соединен с одним из входов L выходных двухвходовых схем совпадения, второй вход каждой из них соединен с единичным выходом триггера соответствующего разряда выходного сдвигового регистра разрядностью L, выходы указанных двухвходовых схем совпадения являются выходами подачи выходной кодовой комбинации на контроллер внешнего запоминающего устройства, единичные и нулевые выходы триггеров М-разрядного счетчика веса канального кода соединены с первыми входами M соответствующих двухвходовых схем совпадения в соответствии с недопустимыми весами канального кода, вторые входы указанных M двухвходовых схем совпадения соединены с выходом первого счетчика числа импульсов канального кода до (d+1), задержанный на двух последовательных инверторах, выходы указанных M схем совпадения соединены с соответствующими входами М-входовой схемы «ИЛИ», выход М-входовой схемы «ИЛИ» соединен со входом установки в «1» триггера «стертый», вход сброса в «0» которого соединен с задержанным на двух инверторах выходом первого счетчика числа импульсов канального кода до (d+1), выход триггера «стертый» является выходом подачи на контроллер внешнего запоминающего устройства сигнала о стертости текущего канального кода. Триггеры «больше», «меньше», «все меньше», «все больше», «все меньше раньше», «все больше раньше», «счет позиции «1»», «короткий цикл» и «стертый» являются стандартными триггерами, а данные названия введены для удобства понимания их функции в устройстве.

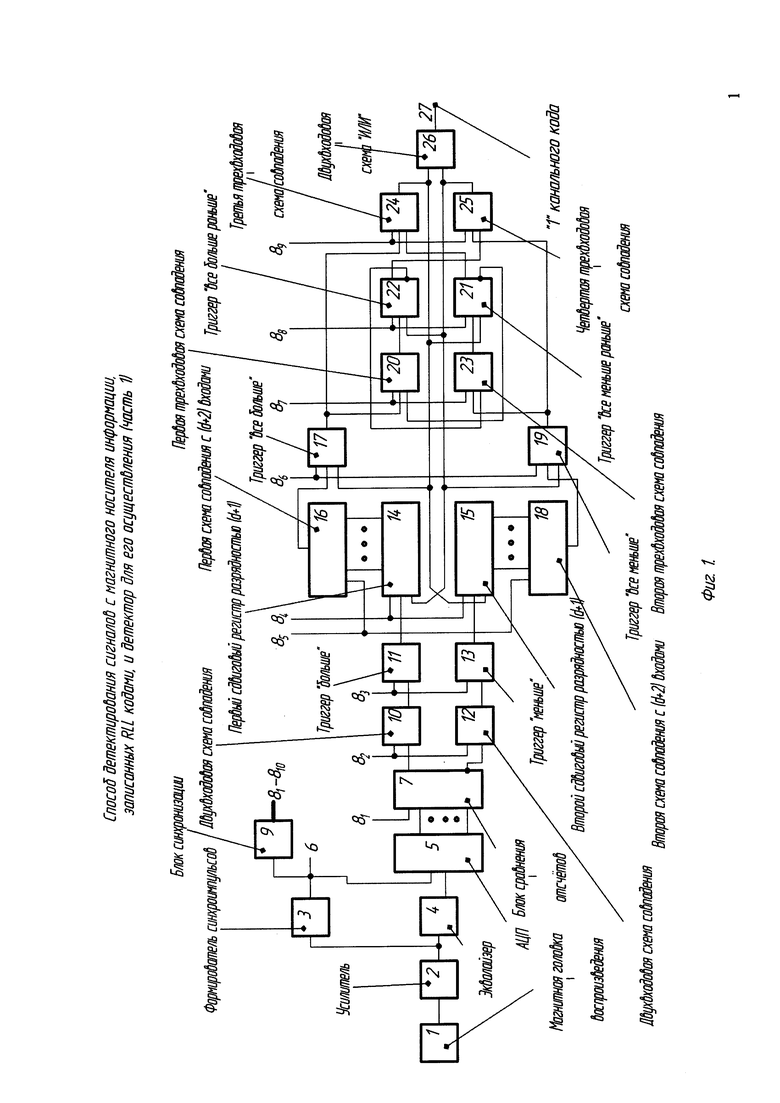

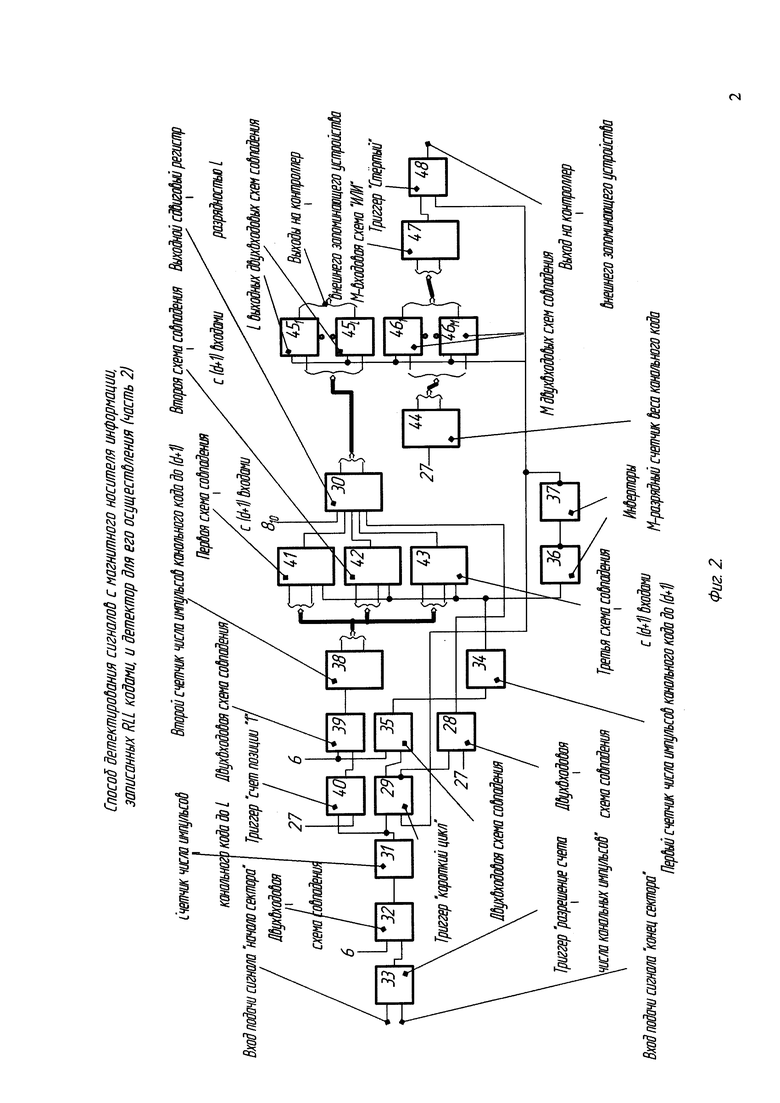

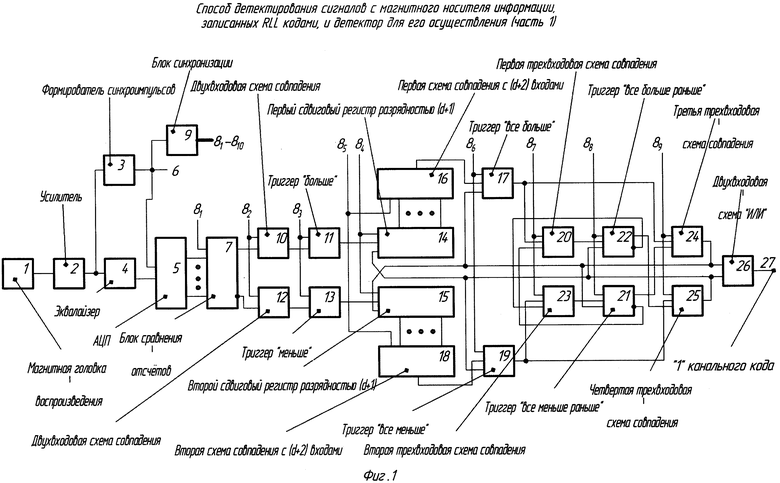

Схема детектора сигналов с магнитного носителя информации, записанных RLL кодами, разделена на две части, которые представлены на фиг. 1 и фиг. 2. Детектор, схема которого представлена на фиг. 1 и фиг. 2, содержит магнитную головку воспроизведения 1, выход магнитной головки воспроизведения 1 соединен со входом усилителя 2, выход усилителя 2, соединен со входом формирователя синхроимпульсов 3, и со входом эквалайзера 4, выход эквалайзера 4 соединен со входом АЦП 5, вход, определяющий частоту квантования которого, соединен с выходом 6 формирователя синхроимпульсов 3, выходы АЦП 5 соединены со входами блока сравнения отсчетов 7, другой вход которого соединен с выходом 81 блока синхронизации 9, вход которого соединен с выходом формирователя синхроимпульсов 3, прямой выход знакового разряда блока сравнения отсчетов 7 соединен со входом двухвходовой схемы совпадения 10, второй вход которой соединен с выходом 82 блока синхронизации 9, выход двухвходовой схемы совпадения 10 соединен со входом установки в «1» триггера «больше» 11, вход стробирования которого соединен с выходом 83 блока синхронизации 9, инверсный выход знакового разряда блока сравнения отсчетов 7 соединен со входом двухвходовой схемы совпадения 12, второй вход которой соединен с выходом 82 блока синхронизации 9, выход двухвходовой схемы совпадения 12 соединен со входом установки в «1» триггера «меньше» 13, вход стробирования которого соединен с выходом 83 блока синхронизации 9, единичный выход триггера «больше» 11 соединен со входом установки в «1» триггера первого сдвигового регистра разрядностью (d+1) 14, где d есть d-ограничение RLL кода и может принимать значения от 0 до 4 единичный выход триггера «меньше» 13 соединен со входом второго сдвигового регистра разрядностью (d+1) 15, входы управления цепями сдвига на 1 к старшим разрядам первого и второго сдвиговых регистров разрядностью (d+1) 14 15 соединены с выходом 84 блока синхронизации 9, единичные выходы триггеров первого сдвигового регистра разрядностью (d+1) 14 соединены с соответствующими входами первой схемы совпадения с (d+2) входами 16, (d+2) вход которой соединен с выходом 85 блока синхронизации 9, выход первой схемы совпадения с (d+2) входами 16 соединен со входом установки в «1» триггера «все больше» 17, вход стробирования которого соединен с выходом 86 блока синхронизации 9, единичные выходы триггеров второго сдвигового регистра разрядностью (d+1) 15 соединены с соответствующими входами второй схемы совпадения с (d+2) входами 18, (d+2) вход которой соединен с выходом 85 блока синхронизации 9, выход второй схемы совпадения с (d+2) входами 18 соединен со входом установки в «1» триггера «все меньше» 19, вход стробирования которого соединен с выходом 86 блока синхронизации 9, единичный выход триггера «все больше» 17 соединен со входом первой трехвходовой схемы совпадения 20, второй вход которой соединен с нулевым выходом триггера «все меньше раньше» 21, а третий вход соединен с выходом 87 блока синхронизации 9, выход первой трехвходовой схемы совпадения 20 соединен со входом установки в «1» триггера «все больше раньше» 22, вход стробирования которого соединен с выходом 88 блока синхронизации 9, единичный выход триггера «все меньше» 19 соединен со входом второй трехвходовой схемы совпадения 23, второй вход которой соединен с нулевым выходом триггера «все больше раньше» 22, третий вход соединен с выходом 87 блока синхронизации 9, выход второй трехвходовой схемы совпадения 23 соединен со входом установки в «1» триггера «все меньше раньше» 21, вход стробирования которого соединен с выходом 88 блока синхронизации 9, единичный выход триггера «все больше» 17 соединен со входом третьей трехвходовой схемы совпадения 24, второй вход которой соединен с единичным выходом триггера «все меньше раньше» 21, а третий вход соединен с выходом 89 блока синхронизации 9, единичный выход триггера «все меньше» 19 соединен со входом четвертой трехвходовой схемы совпадения 25, второй вход которой соединен с единичным выходом триггера «все больше раньше» 22, а третий вход соединен с выходом 89 блока синхронизации 9, выход третьей трехвходовой схемы совпадения 24 соединен со входом установки в «0» второго сдвигового регистра разрядностью (d+1) 15, триггера «все больше» 17 и триггера «все меньше раньше» 21, выход четвертой трехвходовой схемы совпадения 25 соединен со входом установки в «0» первого сдвигового регистра разрядностью (d+1) 14, триггера «все меньше» 19 и триггера «все больше раньше» 22, выходы третьей и четвертой трехвходовых схем совпадения 24 25 соединены со входами двухвходовой схемы «ИЛИ» 26, выход которой ««1» канального кода» 27 соединен со входом двухвходовой схемы совпадения 28, второй вход которой соединен с нулевым выходом триггера «короткий цикл» 29, выход двухвходовой схемы совпадения 28 соединен со входом установки в «1» триггера выходного сдвигового регистра разрядностью L 30, где L - число бит в канальном коде и может принимать значения от 10 до 4097, сдвинутого на (d+1) разрядов относительно младшего разряда, вход управления цепями сдвига на 1 к старшим разрядам выходного сдвигового регистра разрядностью L 30 соединены с выходом 810 блока синхронизации 9, выход 6 формирователя синхроимпульсов 3 соединен со входом счетчика числа импульсов канального кода до L 31, через двухвходовую схему совпадения 32, второй вход которой соединен с единичным выходом триггера «разрешение счета числа канальных импульсов» 33, последний имеет вход установки в «1», который является входом подачи сигнала «начало сектора» с контроллера внешнего запоминающего устройства, и вход сброса в «0», который является входом подачи сигнала «конец сектора» с контроллера внешнего запоминающего устройства, выход 6 формирователя синхроимпульсов 3 соединен со входом первого счетчика числа импульсов канального кода до (d+1) 34 через двухвходовую схему совпадения 35, второй вход которой соединен с единичным выходом триггера «короткий цикл» 29, вход установки в «1» которого соединен с выходом счетчика числа импульсов канального кода до L 31, а вход установки в «0» соединен с выходом двух последовательных инверторов 36 37, вход первого из них соединен с выходом первого счетчика числа импульсов канального кода до (d+1) 34, выход 6 формирователя синхроимпульсов 3 соединен со входом второго счетчика числа импульсов канального кода до (d+1) 38, через двухвходовую схему совпадения 39, второй вход которой соединен с единичным выходом триггера «счет позиции «1»» 40, вход установки в «1» которого соединен с выходом счетчика числа импульсов канального кода до L 31, а вход установки в «0» которого соединен с выходом ««1» канального кода» 27 двухвходовой схемы «ИЛИ» 26, единичный выход триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) 38 соединен с одним из входов первой схемы совпадения с (d+1) входами 41, другие (d-1) входов соединены с соответствующими нулевыми выходами триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1) 38, а (d+1) вход соединен выходом первого счетчика числа импульсов канального кода до (d+1) 34, выходной сигнал первой схемы совпадения с (d+1) входами 41 соединен со входом установки в «1» триггера выходного сдвигового регистра разрядностью L 30, расположенного в разряде, смещенном на d позиций относительно младшего разряда выходного сдвигового регистра разрядностью L 30 в сторону старших разрядов, нулевой выход триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) 38 соединен с одним из входов второй схемы совпадения с (d+1) входами 42, единичный выход триггера следующего за младшим разряда второго счетчика числа импульсов канального кода до (d+1) 38 соединен с другим входом второй схемы совпадения с (d+1) входами 42, другие (d-2) входов соединены с соответствующими нулевыми выходами триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1) 38, a (d+1) вход соединен с выходом первого счетчика числа импульсов канального кода до (d+1) 34, выход второй схемы совпадения с (d+1) входами 42 соединен со входом установки в «1» триггера выходного сдвигового регистра разрядностью L 30, расположенного в разряде, смещенном на (d-1) позицию относительно младшего разряда выходного сдвигового регистра разрядностью L 30 в сторону старших разрядов, единичные выходы триггеров младшего разряда и следующего за ним разряда второго счетчика числа импульсов канального кода до (d+1) 38 соединены с отдельными входами третьей схемы совпадения с (d+1) входами 43, другие (d-2) входов соединены с соответствующими нулевыми выходами триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1) 38, a (d+1) вход соединен с выходом первого счетчика числа импульсов канального кода до (d+1) 34, выходной сигнал третьей схемы совпадения с (d+1) входами 43 соединен со входом установки в «1» триггера выходного сдвигового регистра разрядностью L 30, расположенного в разряде, смещенном на (d-2) позиции относительно младшего разряда выходного сдвигового регистра разрядностью L 30 в сторону старших разрядов, выход «1» канального кода 27 двухвходовой схемы «ИЛИ» 26 соединен со входом М-разрядного счетчика веса канального кода 44, где M соответствует максимально возможному весу данного RLL кода, и может принимать значения от 2 до 32, выход первого счетчика числа импульсов канального кода до (d+1) 34, задержанный на двух последовательных инверторах 36 37, соединен с одним из входов L выходных двухвходовых схем совпадения 451-45L, второй вход каждой из них соединен с единичным выходом триггера соответствующего разряда выходного сдвигового регистра разрядностью L 30, выходы L выходных двухвходовых схем совпадения 451-45L являются выходами подачи выходной кодовой комбинации на контроллер внешнего запоминающего устройства, единичные и нулевые выходы триггеров М-разрядного счетчика веса канального кода 44 соединены со входами соответствующих M двухвходовых схем совпадения 461-46M в соответствии с недопустимыми весами канального кода, один из входов указанных схем совпадения 461-46M соединен с выходом первого счетчика числа импульсов канального кода до (d+1) 34, задержанный на двух последовательных инверторах 36 37, выходы указанных схем совпадения 461-46M соединены с соответствующими входами М-входовой схемы «ИЛИ» 47, выход М-входовой схемы «ИЛИ» 47 соединен со входом установки в «1» триггера «стертый» 48, вход установки в «0» которого соединен с задержанным на двух инверторах 36 37 выходом первого счетчика числа импульсов канального до (d+1) 34, выход триггера «стертый» 48 является выходом подачи сигнала о стертости текущего канального кода на контроллер внешнего запоминающего устройства. На схеме соединения между вторым счетчиком числа импульсов канального кода до (d+1) 38, первым, вторым и третьим схемами совпадения с (d+1) входами 41 42 43 представлены в виде шины в целях незагромождения фигуры 2. С этой же целью в виде шины представлены соединения между выходным сдвиговым регистром разрядностью L 30, L выходных двухвходовых схем совпадения 441-44L, М-разрядным счетчиком веса канального кода 44 и M двухвходовых схем совпадения 461-46M, так же в виде шины 8 представлены выходы блока синхронизации 9. Ответвление от выхода формирователя синхроимпульсов 3 обозначен отдельным номером 6, для удобства приведения ссылок на этот выход из фигуры 2. С этой же целью отдельным номером 27 обозначен выход двухвходовой схемы «ИЛИ» 26. Все блоки, упомянутые выше, общеизвестны и могут быть выполнены по стандартным схемам. Устройство имеет электропитание, которое не показано на схеме.

Рассмотрим осуществление способа детектирования сигналов с магнитного носителя информации, записанных RLL кодами, и работу детектора для его осуществления. На детектор подаем питание, магнитный носитель приводится в движение, контроллер находит нужный сектор и с начала данных пользователя, записанных RLL кодами, сигнал, воспроизведенный с магнитного носителя информации магнитной головкой воспроизведенния 1, усиливается на усилителе 2, из усиленного сигнала формируются синхроимпульсы в моменты времени соответствующие центрам бит канального кода на формирователе синхроимпульсов 3, параллельно формированию синхроимпульсов усиленный сигнал выравнивается на эквалайзере 4, сигнал с выхода эквалайзера 4 преобразуется на АЦП 5 заданной разрядности в цифровые отсчеты в моменты времени, определяемые синхроимпульсами с выхода формирователя синхроимпульсов 3, синхроимпульсы с выхода формирователя синхроимпульсов 3 сразу после формирования подаются на вход блока синхронизации 9, в котором с приходом каждого синхроимпульса формируется временной цикл работы детектора, состоящий из заданного числа импульсов, отстоящих друг от друга на период, по крайней мере, на порядок меньший, чем период синхроимпульсов, цифровые отсчеты с выхода АЦП 5 параллельно подаются на блок сравнения отсчетов 7, на котором производится вычитание предыдущего отсчета из текущего и восстановление текущего отсчета после передачи знака результата вычитания с приходом соответствующего импульса временного цикла работы детектора с выхода 81 блока синхронизации 9, сигнал с прямого выхода триггера знака результата вычитания блока сравнения отсчетов 7 подается на двухвходовую схему совпадения 10, на второй вход которой подается соответствующий импульс временного цикла работы детектора с выхода 82 блока синхронизации 9, сигнал с инверсного выхода триггера знака результата вычитания блока сравнения отсчетов 7 подается на двухвходовую схему совпадения 12, на второй вход которой подается соответствующий импульс временного цикла работа детектора с выхода 82 блока синхронизации 9, сигналом с выхода двухвходовой схемы совпадения 10 устанавливается в «1» триггер «больше» 11, сигналом с выхода двухвходовой схемы совпадения 12 устанавливается в «1» триггер «меньше» 13, на вход стробирования триггера «больше» 11 и триггера «меньше» 13 подается соответствующий импульс временного цикла работы детектора с выхода 83 блока синхронизации 9, сигналы с единичного выхода триггера «больше» 11 подаются последовательно после каждого вычитания на входной триггер первого сдвигового регистра разрядностью (d+1) 14, где d есть d-ограничение RLL кода и может принимать значения от 0 до 4, сигналы с единичного выхода триггера «меньше» 13 подаются последовательно после каждого вычитания на входной триггер второго сдвигового регистра разрядностью (d+1) 15, предварительно соответствующим импульсом временного цикла работы детектора с выхода 84 блока синхронизации 9 производится сдвиг содержимого первого 14 и второго 15 сдвиговых регистров разрядностью (d+1) на один в сторону старших разрядов, сигналы с единичных выходов триггеров первого сдвигового регистра разрядностью (d+1) 14 подаются на соответствующие входы первой схемы совпадения с (d+2) входами 16, на (d+2) вход которой подается соответствующий импульс временного цикла работы детектора с выхода 85 блока синхронизации 9, сигнал с выхода первой схемы совпадения с (d+2) входами 16 подается на установку в «1» триггера «все больше» 17, на вход стробирования которого подается соответствующий импульс временного цикла работы детектора с выхода 86 блока синхронизации 9,сигналы с единичных выходов триггеров второго сдвигового регистра разрядностью (d+1) 15 подаются на соответствующие входы второй схемы совпадения с (d+2) входами 18, на (d+2) вход которой подается соответствующий импульс временного цикла работы детектора с выхода 85 блока синхронизации 9, сигнал с выхода второй схемы совпадения с (d+2) входами 18 подается на установку в «1» триггера «все меньше» 19, на вход стробирования которого подается соответствующий импульс временного цикла работы детектора с выхода 86 блока синхронизации 9, сигнал с единичного выхода триггера «все больше» 17 подается на первую трехвходовую схему совпадения 20, на второй вход которой подается сигнал с нулевого выхода триггера «все меньше раньше» 21, а на третий вход подается соответствующий импульс временного цикла работы детектора с выхода 87 блока синхронизации 9, сигналом с выхода первой трехвходовой схемы совпадения 20 устанавливается в состояние «1» триггер «все больше раньше» 22, на вход стробирования которого подается соответствующий импульс временного цикла работы детектора с выхода 88 блока синхронизации 9, сигнал с единичного выхода триггера «все меньше» 19 подается на вторую трехвходовую схему совпадения 23, на второй вход которой подается сигнал с нулевого выхода триггера «все больше раньше» 22, а на третий вход подается соответствующий импульс временного цикла работы детектора с выхода 87 блока синхронизации 9, сигналом с выхода второй трехвходовой схемы совпадения 23 устанавливается в состояние «1» триггер «все меньше раньше» 21, на вход стробирования которого подается соответствующий импульс временного цикла работы детектора с выхода 88 блока синхронизации 9, сигнал «1» канального кода вырабатывается на третьей трехвходовой схеме совпадения 24, на один вход которой подается сигнал с единичного выхода триггера «все больше» 17, на второй вход подается сигнал с единичного выхода триггера «все меньше раньше» 21, а на третий вход подается соответствующий импульс временного цикла работы детектора с выход 89 блока синхронизации 9, сигнал «1» канального кода вырабатывается также на четвертой трехвходовой схеме совпадения 25, на один вход которой подается сигнал с единичного выхода триггера «все меньше» 19, на второй вход подается сигнал с единичного выхода триггера «все больше раньше» 22, а на третий вход подается соответствующий импульс временного цикла работы детектора с выхода 89 блока синхронизации 9, сигналом с выхода третьей трехвходовой схемы совпадения 24 сбрасывается в «0» второй сдвиговый регистр разрядностью (d+1) 15, триггер «все больше» 17 и триггер «все меньше раньше» 21, сигналом с выхода четвертой трехвходовой схемы совпадения 25 сбрасывается в «0» первый сдвиговый регистр разрядностью (d+1) 14, триггер «все меньше» 19 и триггер «все больше раньше» 22, сигналы «1» канального кода с выхода третьей трехвходовой схемы совпадения 24 и с выхода четвертой трехвходовой схемы совпадения 25 объединяются на двухвходовой схеме «ИЛИ» 26, выходной сигнал «1» канального кода которой подается через двухвходовую схему совпадения 28, на второй вход которой подается сигнал с нулевого выхода триггера «короткий цикл» 29, на установку в «1» триггера выходного сдвигового регистра разрядностью L 30, где L - число бит в канальном коде и может принимать значения от 0 до 4097, расположенного на позиции (d+1) относительно младшего разряда выходного сдвигового регистра разрядностью L 30, код на котором сдвигается на один в сторону старших разрядов с приходом соответствующего импульса временного цикла работы детектора с выхода 810 блока синхронизации 9, синхроимпульсы с выхода формирователя синхроимпульсов 3 подаются на счетчик числа импульсов канального кода до L 31 через двухвходовую схему совпадения 32, на второй вход которой подается сигнал с единичного выхода триггера «разрешение счета числа канальных импульсов» 33, на вход установки в «1» последнего подается сигнал «начало сектора» с контроллера внешнего запоминающего устройства, а на вход сброса в «0» подается импульс «конец сектора» с контроллера внешнего запоминающего устройства, синхроимпульсы с выхода формирователя синхроимпульсов 3 подаются на первый счетчик числа импульсов канального кода до (d+1) 34 через двухвходовую схему совпадения 35, на второй вход которой подается сигнал с единичного выхода триггера «короткий цикл» 29, на установку в «1» которого подается сигнал с выхода счетчика числа импульсов канального кода до L 31, а на установку в «0» подается выходной сигнал первого счетчика числа импульсов канального кода до (d+1) 34, задержанный на двух последовательных инверторах 36 37, синхроимпульсы с выхода формирователя синхроимпульсов 3 подаются на второй счетчик числа импульсов канального кода до (d+1) 38 через двухвходовую схему совпадения 39, на второй вход которой подается сигнал с единичного выхода триггера «счет позиции «1»» 40 на установку в «1» которого подается сигнал с выхода счетчика числа импульсов канального кода до L 31, а на установку в «0» подается выходной сигнал «1» канального кода двухвходовой схемы «ИЛИ» 26, сигнал с единичного выхода триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) 38 подается на один из входов первой схемы совпадения с (d+1) входами 41, на другие (d-1) входов подаются сигналы с соответствующих нулевых выходов триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1) 38, а на (d+1) вход подается выходной сигнал первого счетчика числа импульсов канального кода до (d+1) 34, выходной сигнал первой схемы совпадения с (d+1) входами 41 подается на установку в «1» триггера выходного сдвигового регистра разрядностью L 30, расположенного в разряде, смещенном на d позиций относительно младшего разряда выходного сдвигового регистра разрядностью L 30 в сторону старших разрядов, сигнал с нулевого выхода триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) 38 подается на один из входов второй схемы совпадения с (d+1) входами 42, сигнал с единичного выхода триггера следующего за младшим разряда второго счетчика числа импульсов канального кода до (d+1) 38 подается на другой из входов второй схемы совпадения с (d+1) входами 42, на другие (d-2) входов подаются сигналы с соответствующих нулевых выходов триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1) 38, а на (d+1) вход подается выходной сигнал первого счетчика числа импульсов канального кода до (d+1) 34, выходной сигнал второй схемы совпадения с (d+1) входами 42 подается на установку в «1» триггера выходного сдвигового регистра разрядностью L 30, расположенного в разряде, смещенном на (d-1) позицию относительно младшего разряда выходного сдвигового регистра разрядностью L 30 в сторону старших разрядов, сигналы с единичных выходов триггеров младшего разряда и следующего за ним разряда второго счетчика числа импульсов канального кода до (d+1) 38 подаются на соответствующие входы третьей схемы совпадения с (d+1) входами 43, на другие (d-2) входов подаются сигналы с соответствующих нулевых выходов триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1) 38, а на (d+1) вход подается выходной сигнал первого счетчика числа импульсов канального кода до (d+1) 34, выходной сигнал третьей схемы совпадения с (d+1) входами 43 подается на установку в «1» триггера выходного сдвигового регистра разрядностью L 30, расположенного в разряде, смещенном на (d-2) позиции относительно младшего разряда выходного сдвигового регистра разрядностью L 30 в сторону старших разрядов, сигнал «1» канального кода двухвходовой схемы «ИЛИ» 26 подается также на вход М-разрядного счетчика веса канального кода 44, где M соответствует максимально возможному весу данного RLL кода и может принимать значения от 2 до 32, выходной сигнал первого счетчика числа импульсов канального кода до (d+1) 34, задержанный на двух последовательных инверторах 36 37 подается на один из входов L выходных двухвходовых схем совпадения 451-45L, на вторые входы которых подаются сигналы с единичных выходов соответствующих триггеров выходного сдвигового регистра разрядностью L 30, выходная кодовая комбинация с выходов указанных выходных двухвходовых схем совпадения 451-45L подается на контроллер внешнего запоминающего устройства, сигналы с единичных и нулевых выходов триггеров счетчика веса канального кода 44 подаются на один из входов M соответствующих схем совпадения 461-46M в соответствии со всеми недопустимыми значениями веса канального кода, на другой из входов которых подается выходной сигнал первого счетчика числа импульсов канального кода до (d+1) 34, задержанный на двух последовательных инверторах 36 37, выходные сигналы указанных выше схем совпадения объединяются на М-входовой схеме «ИЛИ» 47, выходной сигнал которой подается на установку в «1» триггера «стертый» 48, который устанавливается в «0» выходным сигналом первого счетчика числа импульсов канального кода до (d+1) 34, задержанным на двух последовательных инверторах 36 37, выходной сигнал триггера «стертый» 48 подается на вход контроллера внешнего запоминающего устройства, сигнализирующий о стертости текущего канального кода.

Работа детектора в динамике происходит следующим образом. При движении магнитного носителя информации сигналы, записанные RLL кодами и воспроизведенные магнитной головкой, представляют из себя суперпозицию колоколообразных откликов разной полярности, следующих друг за другом, причем экстремумы последовательных откликов в определенном диапазоне межсимвольной интерференции отстоят друг от друга минимум на (d+1) битовых интервалов. Детектор определяет наличие экстремума на данном битовом интервале с помощью цифровых отсчетов в центре битовых интервалов. В случае, если на (d+1) битовых интервалах отсчеты последовательно увеличиваются, а на последующих (d+1) битовых интервалах отсчеты последовательно уменьшаются, то детектор фиксирует наличие экстремума и заносит «1» канального кода в разряд выходного регистра, сдвинутый на (d+1) разрядов в сторону старших разрядов относительно младшего разряда выходного сдвигового регистра. Аналогично, в случае, если на (d+1) битовых интервалах отсчеты последовательно уменьшаются, а на последующих (d+1) битовых интервалах отсчеты последовательно увеличиваются, то детектор фиксирует наличие экстремума и заносит «1» канального кода в разряд выходного регистра, сдвинутый на (d+1) разрядов в сторону старших разрядов относительно младшего разряда выходного регистра. Сдвиг на (d+1) связан с запаздыванием решения детектора о наличии экстремума относительно действительного положения экстремума. После окончания текущего канального кода решение о значениях его младших разрядах еще не принято, поэтому параллельно с началом следующего канального кода формируют два коротких цикла на двух счетчиках до (d+1). Один счетчик отсчитывает (d+1) синхроимпульсов, а второй «замораживается» с приходом «1» канального кода, т.е. определяет позицию «1» в младших разрядах предыдущего канального кода, после чего «1» заносят в соответствующий младший разряд выходного регистра и его содержимое выдают в контроллер.

Таким образом, по сравнению с прототипом, предлагаемые способ детектирования сигналов с магнитного носителя информации, записанных RLL кодами, и детектор для его осуществления более помехоустойчивы при действии мультипликативной помехи за счет решений, использующих особенности тракта магнитной записи-воспроизведения. К таким решениям относятся запись по двум уровням и, соответственно, чередование направлений последовательных перепадов намагниченности, учет d-ограничения RLL кодов, и использование знака разности между последовательными отсчетами в центрах бит, который не меняется (без учета аддитивного шума) при действии мультипликативной помехи, в отличие от PRML, в котором используются абсолютные величины последовательных откликов. Упрощение алгоритма обработки сигнала и, как следствие, снижение требуемой вычислительной мощности достигается за счет того, что предлагаемые способ и детектор, в отличие от прототипа, не производят сравнение выживших кодовых последовательностей по принципу максимального правдоподобия. Вышеописанная особенность на приемлемом уровне снижает помехоустойчивость при действии аддитивной помехи, но существенно упрощает детектор аппаратно.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с переменным коэффициентом деления | 2021 |

|

RU2762529C1 |

| УСТРОЙСТВО ДЛЯ ПНЕВМОМАССАЖА | 1993 |

|

RU2061456C1 |

| Устройство контроля ошибок многоканальной аппаратуры магнитной записи | 1987 |

|

SU1529285A1 |

| Устройство для построения сейсмических разрезов | 1985 |

|

SU1291917A1 |

| Детектор @ -зубца электрокардиосигнала | 1984 |

|

SU1260004A1 |

| Программное устройство для фиксации и документирования времени | 1989 |

|

SU1677691A1 |

| Способ озвучивания кинофильмов и устройство для его осуществления | 1989 |

|

SU1705793A1 |

| Генератор псевдослучайных кодов | 1983 |

|

SU1167710A1 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Избирательное устройство для управления тиристорными регуляторами | 1980 |

|

SU888293A1 |

Изобретение относится к способам детектирования сигналов с магнитных носителей внешних запоминающих устройств и детекторам для их осуществления. Технический результат заключается в повышении помехоустойчивости. Технический результат достигается за счет использования таких особенностей тракта магнитной записи и воспроизведения, как запись по двум уровням и, соответственно, чередование направлений последовательных перепадов намагниченности, учет d-ограничения RLL кодов, и использование знака разности между последовательными отсчетами в центрах бит, который не меняется (без учета аддитивного шума) при действии мультипликативной помехи. Детектор определяет наличие экстремума на данном битовом интервале с помощью цифровых отсчетов в центре битовых интервалов. В случае, если на (d+1) битовых интервалах отсчеты последовательно увеличиваются, а на последующих (d+1) битовых интервалах отсчеты последовательно уменьшаются, то детектор фиксирует наличие экстремума и заносит «1» канального кода в разряд выходного регистра, сдвинутый на (d+1) разрядов в сторону старших разрядов относительно младшего разряда выходного сдвигового регистра. Аналогично, в случае, если на (d+1) битовых интервалах отсчеты последовательно уменьшаются, а на последующих (d+1) битовых интервалах отсчеты последовательно увеличиваются, то детектор фиксирует наличие экстремума и заносит «1» канального кода в разряд выходного регистра, сдвинутый на (d+1) разрядов в сторону старших разрядов относительно младшего разряда выходного регистра. Сдвиг на (d+1) связан с запаздыванием решения детектора о наличии экстремума относительно действительного положения экстремума. После окончания текущего канального кода решение о значениях его младших разрядах еще не принято, поэтому параллельно с началом следующего канального кода формируют два коротких цикла на двух счетчиках до (d+1). Один счетчик отсчитывает (d+1) синхроимпульсов, а второй «замораживается» с приходом «1» канального кода, т.е. определяет позицию «1» в младших разрядах предыдущего канального кода, после чего «1» заносят в соответствующий младший разряд выходного регистра и его содержимое выдают в контроллер. 2 н.п. ф-лы, 2 ил.

1. Способ детектирования сигналов с магнитного носителя информации, записанных RLL кодами, включающий усиление сигнала, воспроизведенного с магнитного носителя информации с помощью магнитной головки воспроизведения, на усилителе, формирование из усиленного сигнала синхроимпульсов в моменты времени, соответствующие центрам бит канального кода, параллельно формированию синхроимпульсов выравнивание усиленного сигнала на эквалайзере, преобразование усиленного сигнала на АЦП заданной разрядности в цифровые отсчеты в моменты времени, определяемые синхроимпульсами, отличающийся тем, что синхроимпульсы сразу после формирования подают на вход блока синхронизации, в котором с приходом каждого синхроимпульса формируют временной цикл работы детектора, состоящий из заданного числа импульсов, отстоящих друг от друга на период, по крайней мере, на порядок меньший, чем период синхроимпульсов, цифровые отсчеты с выхода АЦП параллельно подают на блок сравнения отсчетов, на котором производят вычитание предыдущего отсчета из текущего и восстановление текущего отсчета после передачи знака результата вычитания, сигналом с единичного выхода триггера знака результата вычитания блока сравнения отсчетов, пропущенным через двухвходовую схему совпадения, устанавливают в «1» триггер «больше», сигналом с нулевого выхода триггера знака результата вычитания блока сравнения отсчетов, пропущенным через двухвходовую схему совпадения, устанавливают в «1» триггер «меньше», на вторые входы двухвходовых схем совпадения подается соответствующий импульс временного цикла работы детектора с блока синхронизации, сигналы с единичного выхода триггера «больше» подают последовательно после каждого вычитания на входной триггер первого сдвигового регистра разрядностью (d+1), где d есть d-ограничение RLL кода и может принимать значения от 0 до 4, сигналы с единичного выхода триггера «меньше» подают последовательно после каждого вычитания на входной триггер второго сдвигового регистра разрядностью (d+1), предварительно соответствующим импульсом временного цикла работы детектора с блока синхронизации производят сдвиг содержимого первого и второго сдвиговых регистров разрядностью (d+1) на один в сторону старших разрядов, единичные выходы триггеров первого сдвигового регистра разрядностью (d+1) подают на соответствующие входы первой схемы совпадения с (d+2) входами, на (d+2) вход которой подают соответствующий импульс временного цикла работы детектора с блока синхронизации, выход первой схемы совпадения с (d+2) входами подают на установку в «1» триггера «все больше», единичные выходы триггеров второго сдвигового регистра разрядностью (d+1) подают на соответствующие входы второй схемы совпадения на (d+2) входов, на (d+2) вход которой подают соответствующий импульс временного цикла работы детектора с блока синхронизации, выход второй схемы совпадения на (d+2) входов подают на установку в «1» триггера «все меньше», сигнал с единичного выхода триггера «все больше» подают на первую трехвходовую схему совпадения, на второй вход которой подают сигнал с нулевого выхода триггера «все меньше раньше», а на третий вход подают соответствующий импульс временного цикла работы детектора с блока синхронизации, сигналом с выхода первой трехвходовой схемы совпадения устанавливают в состояние «1» триггер «все больше раньше», сигнал с единичного выхода триггера «все меньше» подают на вторую трехвходовую схему совпадения, на второй вход которой подают сигнал с нулевого выхода триггера «все больше раньше», а на третий вход подают соответствующий импульс временного цикла работы детектора с блока синхронизации, сигналом с выхода второй трехвходовой схемы совпадения устанавливают в состояние «1» триггер «все меньше раньше», сигнал «1» канального кода вырабатывают на третьей трехвходовой схеме совпадения, на один вход которой подают сигнал с единичного выхода триггера «все больше», на второй вход подают сигнал с единичного выхода триггера «все меньше раньше», а на третий вход подают соответствующий импульс временного цикла работы детектора с блока синхронизации, сигнал «1» канального кода вырабатывают также на четвертой трехвходовой схеме совпадения, на один вход которой подают сигнал с единичного выхода триггера «все меньше», на второй вход подают сигнал с единичного выхода триггера «все больше раньше», а на третий вход подают соответствующий импульс временного цикла работы детектора с блока синхронизации, сигналом с выхода третьей трехвходовой схемы совпадения сбрасывают в «0» второй сдвиговый регистр разрядностью (d+1), триггер «все больше» и триггер «все меньше раньше», сигналом с выхода четвертой трехвходовой схемы совпадения сбрасывают в «0» первый сдвиговый регистр разрядностью (d+1), триггер «все меньше» и триггер «все больше раньше», сигналы «1» канального кода с выхода третьей трехвходовой схемы совпадения и с выхода четвертой трехвходовой схемы совпадения объединяют на двухвходовой схеме «ИЛИ», выходной сигнал «1» канального кода которой подают через двухвходовую схему совпадения, на второй вход которой подают сигнал с нулевого выхода триггера «короткий цикл», на установку в «1» триггера выходного сдвигового регистра разрядностью L, где L - число бит в канальном коде и может принимать значения от 10 до 4097, расположенного на позиции (d+1) относительно младшего разряда выходного сдвигового регистра разрядностью L, код на котором сдвигают на один сторону старших разрядов с приходом соответствующего импульса каждого временного цикла работы детектора с блока синхронизации, синхроимпульсы с выхода формирователя синхроимпульсов подают на счетчик числа импульсов канального кода до L через двухвходовую схему совпадения, на второй вход которой подают сигнал с единичного выхода триггера «разрешение счета числа канальных импульсов», на вход установки в «1» последнего подают сигнал «начало сектора», а на вход сброса в «0» подают сигнал «конец сектора» с контроллера внешнего запоминающего устройства, синхроимпульсы с выхода формирователя синхроимпульсов подают на первый счетчик числа импульсов канального кода до (d+1) через двухвходовую схему совпадения, на второй вход которой подают сигнал с единичного выхода триггера «короткий цикл», на установку в «1» которого подают выход счетчика числа импульсов канального кода до L, а на установку в «0» выходной сигнал первого счетчика числа импульсов канального кода до (d+1), задержанный на двух последовательных инверторах, синхроимпульсы с выхода формирователя синхроимпульсов подают на второй счетчик числа импульсов канального кода до (d+1) через двухвходовую схему совпадения, на второй вход которой подают сигнал с единичного выхода триггера «счет позиции «1»» на установку в «1», которого подают выход счетчика числа импульсов канального кода до L, а на установку в «0» выходной сигнал двухвходовой схемы «ИЛИ» «1» канального кода, единичный выход триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) подают на один из входов первой схемы совпадения с (d+1) входами, на другие (d-1) входов подают соответствующие нулевые выходы триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), а на (d+1) вход подают выходной сигнал первого счетчика числа импульсов канального кода до (d+1), выходной сигнал первой схемы совпадения с (d+1) входами подают на установку в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на d позиций относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, нулевой выход триггера младшего разряда второго счетчика числа импульсов канального кода до (d+1) подают на один из входов второй схемы совпадения с (d+1) входами, единичный выход триггера, следующего за младшим разряда второго счетчика числа импульсов канального кода до (d+1), подают на один из входов второй схемы совпадения с (d+1) входами на другие (d-2) входов подают соответствующие нулевые выходы триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), а на (d+1) вход подают выходной сигнал первого счетчика числа импульсов канального кода до (d+1), выходной сигнал второй схемы совпадения с (d+1) входами подают на установку в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на (d-1) позицию относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, единичные выходы триггеров младшего разряда и следующего за ним разряда второго счетчика числа импульсов канального кода до (d+1) подают на соответствующие входы третьей схемы совпадения с (d+1) входами, на другие (d-2) входов подают соответствующие нулевые выходы триггеров следующих старших разрядов второго счетчика числа импульсов канального кода до (d+1), а на (d+1) вход подают выходной сигнал первого счетчика числа импульсов канального кода до (d+1), выходной сигнал третьей схемы совпадения с (d+1) входами подают на установку в «1» триггера выходного сдвигового регистра разрядностью L, расположенного в разряде, смещенном на (d-2) позиции относительно младшего разряда выходного сдвигового регистра разрядностью L в сторону старших разрядов, выходной сигнал двухвходовой схемы «ИЛИ» «1» канального кода подают также на вход М-разрядного счетчика веса канального кода, где М соответствует максимально возможному весу данного RLL кода и может принимать значения от 2 до 32, выходной сигнал первого счетчика числа импульсов канального кода до (d+1), задержанный на двух последовательных инверторах подают на один из входов L выходных двухвходовых схем совпадения, на вторые входы которых подают сигналы с единичных выходов соответствующих триггеров выходного сдвигового регистра разрядностью L, выходная кодовая комбинация с выходов указанных двухвходовых схем совпадения подается на контроллер внешнего запоминающего устройства, сигналы с единичных и нулевых выходов триггеров М-разрядного счетчика веса канального кода подают на первый из входов М соответствующих двухвходовых схем совпадения в соответствии со всеми недопустимыми значениями веса канального кода, на вторые из входов которых подают выходной сигнал первого счетчика числа импульсов канального кода до (d+1), задержанный на двух последовательных инверторах, выходные сигналы указанных выше М двухвходовых схем совпадения объединяют на М-входовой схеме «ИЛИ», выходной сигнал которой подают на установку в «1» триггера «стертый», который сбрасывают в «0» выходным сигналом первого счетчика числа импульсов канального кода до (d+1), задержанным на двух последовательных инверторах, выходной сигнал триггера «стертый» подается на вход контроллера внешнего запоминающего устройства, сигнализирующий о стертости текущего канального кода.