(54) ДВУХКАНАЛЬНЫЙ ФАЗОВЫЙ КОМПАРАТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Двухканальный фазовый компаратор | 1988 |

|

SU1538144A1 |

| Двухканальный фазовый компаратор | 1980 |

|

SU900214A1 |

| Компаратор фазового сдвига | 1988 |

|

SU1628007A1 |

| Цифровой фазометр | 1981 |

|

SU970258A1 |

| Способ измерения фазового сдвига между двумя гармоническими сигналами и устройство для его осуществления | 1988 |

|

SU1596272A1 |

| Цифровой фазометр | 1981 |

|

SU1029100A1 |

| Цифровой фазометр | 1976 |

|

SU636558A1 |

| Генератор-калибратор временных интервалов | 1985 |

|

SU1367139A1 |

| Цифровой фазометр | 1982 |

|

SU1027638A2 |

| Способ дискретного задания фазового сдвига и устройство для его осуществления | 1986 |

|

SU1337818A1 |

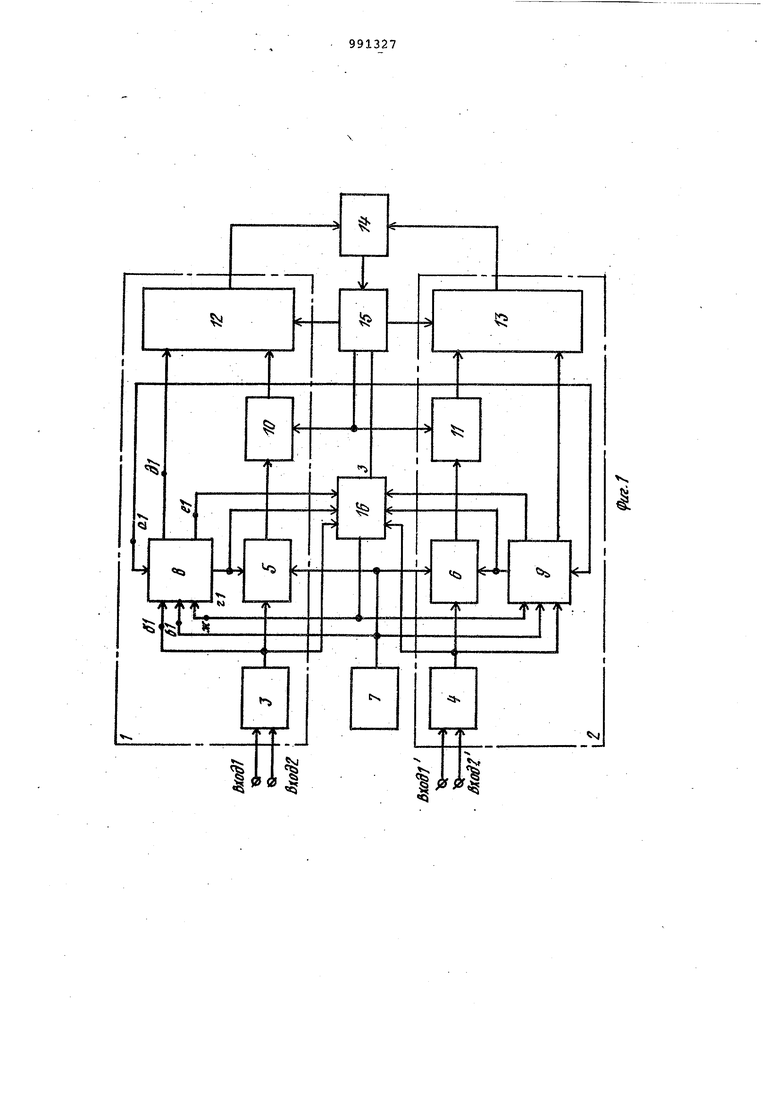

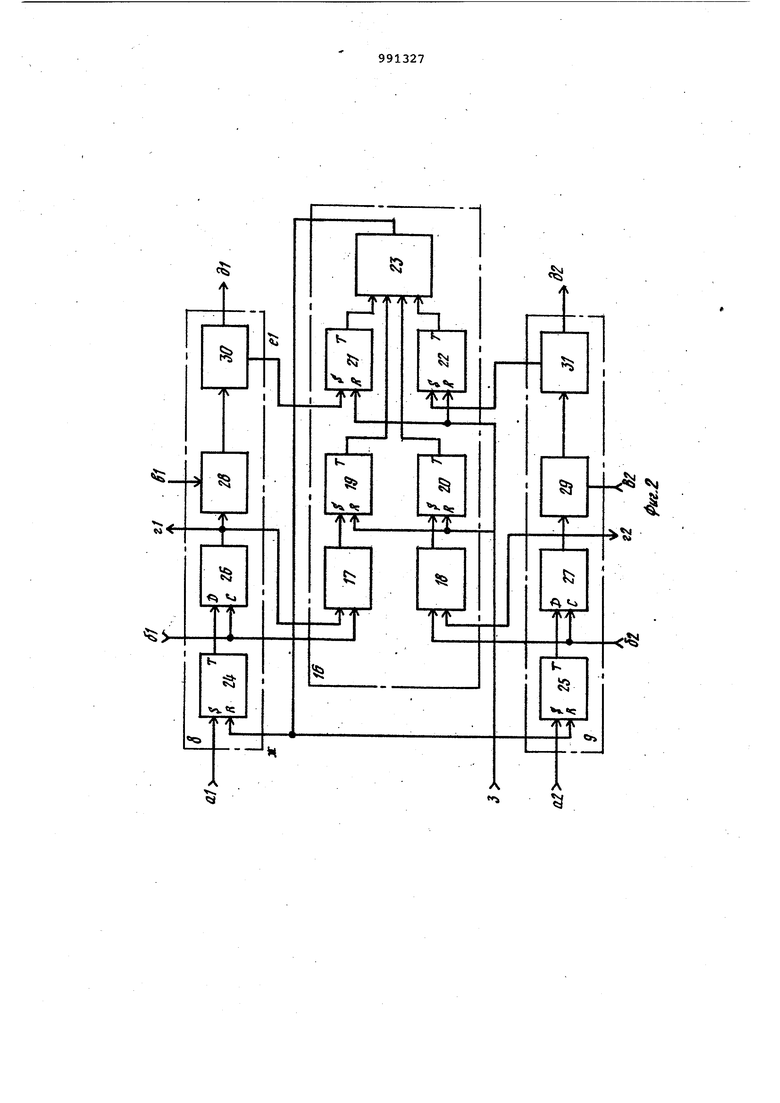

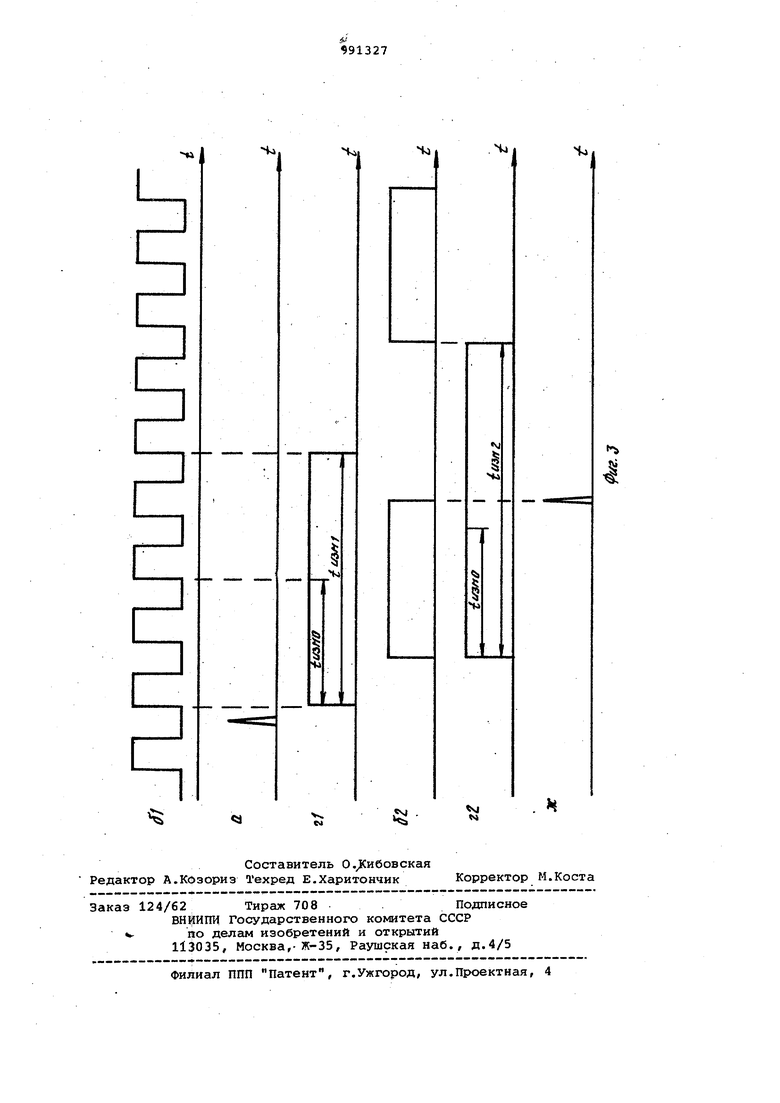

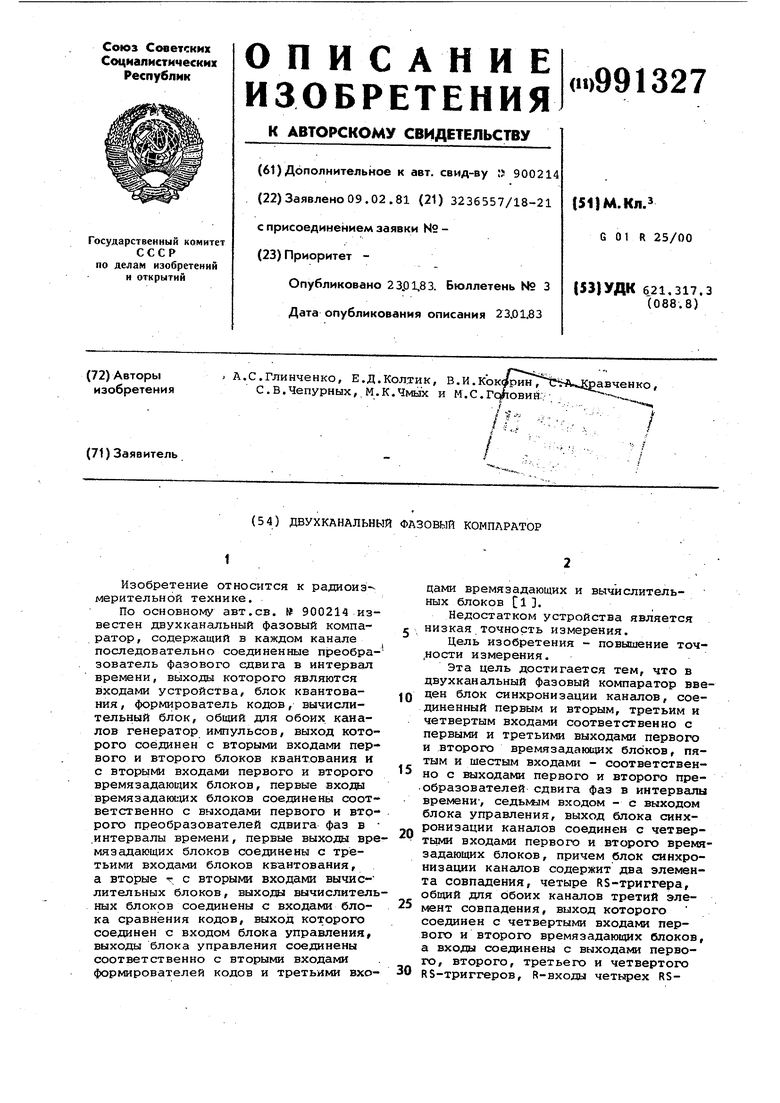

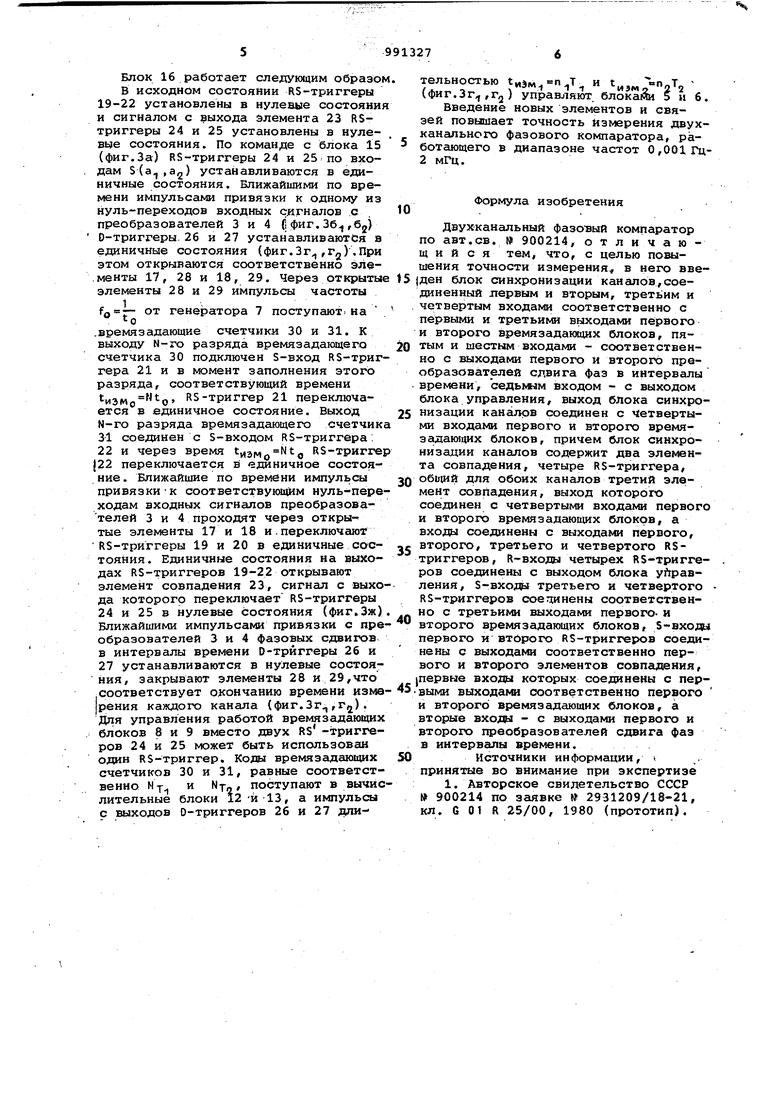

Изобретение относится к радиоиэ мерительной технике. По основному авт.св. № 900214 известен двухканальный фазовый компаратор, содержащий в каждом канале последовательно соединенные преобразователь фазового сдвига в интервал времени, выходы которого являются входами устройства, блок квантования , формирователь кодов, вычислительный блок, общий для обоих каналов генератор импульсов, выход которого соединен с вторыми входами первого и второго блоков квантования и с вторыми входами первого и второго времязадающих блоков, первые входаа времязадающих блоков соединены соответственно с выходами первого и второго преобразователей сдвига фаз в .интервалы времени, первые выходы вре мязадающих блоков соединены с третьими входами блоков квантования, а вторые т, с вторыми входами вычислительных блоков, выходы вычислитель ных блоков соединены с входами блока сравнения кодов, выход которого соедщнен с входом блока управления, выходы блока управления соединены соответственно с вторыми входами формирователей кодов и третьими входами времязадающих и вычислительных блоков 1 . Недостатком устройства является низкая точность измерения. Цель изобретения - повышение точ,ности измерения. Эта цель достигается тем, что в двухканальный фазовый компаратор введен блок синхронизации каналов, соединенный первым и вторым, третьим и четвертым входами соответственно с первыми и третьими выходами первого и второго времязадаю1цих блоков, пятым и щестым входами - соответственно с выходами первого и второго преобразователей сдвига фаз в интервалы времени-, седычлм входом - с выходом блока управления, выход блока синхронизации каналов соединен с четверть1ми входами первого и второго времязадающих блоков, причем блок синхронизации каналов содержит два элемента совпадения, четыре RS-триггера, общий для обоих каналов третий элемент совпадения, выход которого соединен с четвертыми входами первого и второго времязадающих блоков, а входы соединены с выходами первого, второго, третьего и четвертого RS-триггеров, R-входы четырех RSтриггеров соединены с выходом блока управления, S-входы третьего и чет,вертого RS-TpHFrepoB соединены соот ветственно с Т Ьетьими выxoдa /IИ первого и второго времязадаюь Ц1Х блоков S-входы первого и второго RS-тригге ров соединены с выходами соответственно первого и второго элементов совпадения, первые входы которых со единены с первыми выходами соответственно первого и второго времязада ЦИХ блоков, а вторые входы - с выходами первого и второго преобразо вателей сдвига фаз в интервалы времени . На фиг.1 приведена структурная схема компаратора фазы/ на фиг.2 структурная схема блока синхронизации каналов, связанного с времязадающими блоками; на фиг.З - временные диаграммы, иллюстрирующие работ компаратора фазы. Структурная схема компаратора фа зы (фиг.1) содержит два измерительных канала 1 и 2, содержащих последовательно соединенные преобразователи 3 и 4 сдвига фаз в интервалы времени, блоки 5 и б квантования с подключенным к ним генератором 7 им пульсов, времязадающие блоки 8 и 9, формирователи 10 и 11 кодов, вычислительные блоки 12 и 13, связанный ни№1 блок 14 сравнения кодов, блок 15 управления, связанный с блоками 8-14, 16, блок 16 синхронизации каналов преобразователями 3 и 4 и соединенный с блоками 8 и 9. Структурная схема блока 16 (фиг.2 содержит два элемента 17 и 18 совпадения, четыре RS-триггера 19-22, общий элемент 23 совпадения, входы которого соединены с выходами четырех .RS-триггеров. Блок 16 связан с идентичными блоками 8 и 9, которые выпол нены по структурным схемам, описанны в известном устройстве, и содержат последовательно соединенные соответственно RS-триггеры 24 и 25, D-триггеры 26 и 27, элементы 28 и 29, времязадающие счетчики 30 и 31. Компаратор фазы работает следующим образом. На входы канала 1 поступают два сигнала с частотой F и заданным сдвигом фаз V., , на входы канала 2 поступают сигналы с частотой р2 и фазовым сдвигом: , которые нужно сравнить. Преобразователи 3 и 4 формируют эквивалентные временные интер валы (фиг.З 5, ) ,которые, в блоках 5 и 6 заполняются счетнымиимпульс ми частоты генератора 7. Образующиеся импульсов регистрируются формирЬвателями 10 и 11. Времязадающие блоки 8 и 9 и блок 16 формируют для каждого канала время измерения, равное целому числу периодов сигнала. В диапазоне частотг р 1 1 2°тГ t О мзмо время измерения для каждого канала определяется из условия: t,.,... ftu / пЬт L /тЗ-Т+Т -пТ, где Т - период сигнала, часть отношения « измо/Т. На частотах выше F измерения изменяется в пределах +Т, для частот ИЭМ ИЗM(, время измерения определяется периодом сигнала Т (фиг.3.г2). Если период входного сигнала одного канала меньше базового времени измерения, например ,, (фиг.ЗБ), а период входного сигнала другого . канала больше базового времени измере.:ия, например t,з„.(фиг. 36g) , тогда время измерения для каждого канала определяется из условий: 1и5„ СТ2/2Т Тт+Т (фиг.3г), Т2 (фиг.ЗГд), где lTfj/2T j - целая часть отношения Т2/2Т. При этом на частотах выше F ; время измерения одного канала изменяется в пределах t изм ч , 2 йзм иэм2 Благодаря увеличению времени измерения одного канала, уменьшается погрешность дискретного преобразования в области верхних частот, повышается точность сравнения измеряемых фазовых сдвигов без увеличения измерительного цикла компаратора фазы. За время измерения в дЛэрмирователг 10.и 11 формируются кодыМи, 1 Hit VI lAiH- i, I-t, .Q BO времязадающих 141 21 блоках 8 и 9 формируются коды / i( ,5 . «ТГ-Ш .,-К-; данные коды вводятся в вычислительные блоки 12 и 13, где выполняется деление Ni;™ дов г-- и г- и их умножение на маач г TZ табный множитель 360. Результаты вычислений соответствуют сдвигам фаз в градусах: блоке 14 сравнения кодов проис-ходит вычитание кодов Ч-, и , полученный код дf: соответствует отклонению сравниваемого сдвига фаз от заданного. Блок 15 обеспечивает функционирование отдельных блоков компаратора фазы. 59913 Блок 16 работает следующим образом. В исходном состоянии RS-триггеры 19-22 установлены в нулевые состояния и сигналом с выхода элемента 23 RSтриггеры 24 и 25 установлены в нуле- . вце состояния. По команде с блока 155 (фиг.За) RS-триггеры 24 и 25 по входам S(a .а) устанавливаются в единичные состояния. Ближайшими по времени импульсами привязки к одному из нуль-переходов входных сигналов с .Ю преобразователей 3 и 4 {фиг.36,62) D-триггеры. 26 и 27 устанавливаются в единичные состояния (фиг.Зг jr) .При этом открываются соответственно элементы 17, 28 и 18, 29. Через открытые15 элементы 28 и 29 импульсы частоты f,, от генератора 7 поступают, на to .времязадающие счетчики 30 и 31. К выходу N-ro разряда времязадающего 20 счетчика 30 подключен S-вход RS-триггера 21 и в момент заполнения этого разряда, соответствующий времени tn3Mo Nto RS-триггер 21 переключается в единичное состояние. Выход 25 N-ro разряда времязадающего счетчика 31 соединен с S-входом RS-триггера: 22 и через время иэмо° о RS-триггер J22 переключается в единичное состояние. Ближайшие по времени импульсы JQ привязкиК соответствукядам нуль-переходам входных сигналов преобразователей 3 и 4 проходят через откры тые элементы 17 и 18 и.переключают RS-триггеры 19 и 20 в единичные сое- « тояния. Единичные состояния на выходах RS-триггеров 19-22 открывают элемент совпадения 23, сигнал с выхода которого переключает RS-триггеры 24 и 25 в нулевые состояния (фиг.Зж). .. Ближайшими импульсами привязки с пре- образователей 3 и 4 фазовых сдвигов в интервалы времени D-трйггеры 26 и 27 устанавливаются в нулевые состояния, закрывают элементы 28 и 29,что соответствует окончанию времени измв- 45 рения каждого канала (фиг.Зг,Г2). Для управления работой времязадающих блоков 8 и 9 вместо двух RS -триггеров 24 и 25 может быть использован один RS-триггер. Коды врёмязадающих 50 счетчиков 30 и 31, равные соответственно NT и N-fn, поступают в вычислительные блоки 12 -и 13, а импульсы с выходов 0-триггеров 26 и 27 дцш276тельностью t, п Т и t Т (фиг.Зг,,Г2) управляют блйка § и 6. Введение новых элементов и связей повышает точность измерения двухканального фазового компаратора, работающего в диапазоне частот 0,001Гц2 мГц. Формула изобретения . . Двухкаиальный фазовый компаратор по авт.св. 900214, отличающ и и с я тем, что, с целью повышения точности измерения., в него введен блок синхронизации канапов,соединенный лервым и вторым, третьим и четвертым входами соответственно с первыми и третьими выходами первого и второго времязадающих блоков, пятым и шестым входами - соответственно с выходами первого и второго преобразователей сдвига фаз в интервалы времени, седьмым входом - с выходом блока управления, выход блока синхронизации каналов соединен с четвертыми входами первого и второго времязадакицих блоков, причем блок синхронизадии каналов содержит два элемента совпадения, четыре RS-триггера, оби1Ий для обоих каналов третий элемент совпадения, выход которого соединен с четвертыми входами первого и второго времязадающих блоков, а входы соединены с выходами первого, второго, третьего и четвертого RSтриггеров, R-входы четырех RS-триггеров соединены с выходом блока уйравления, S-входы третьего и четвертого RS-триггеров соединены соответственно с третьими выходами первогчэ-и второго времязадающих блоков, Б-входа первого и второго RS-триггеров соединеиы с выходами соответственно первого и второго элементов совпадения, |первые входы которых соединены с пердыми выходами сюответственно первого и второго времязадающих блоков, а вторые входы - с выходами первого и второго преобразователей сдвига фаз в интервалы времени, Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР 900214 по заявке № 2931209/18-21, кл. G 01 R 25/00, 1980 (прототип).

N

Sj

На

Авторы

Даты

1983-01-23—Публикация

1981-02-09—Подача