Изобретение относится к микроэлектронике, а именно к производству интегральных схем.

Цель изобретения - повышение достоверности и уменьшение времени отбраковки микросхем с дефектами.

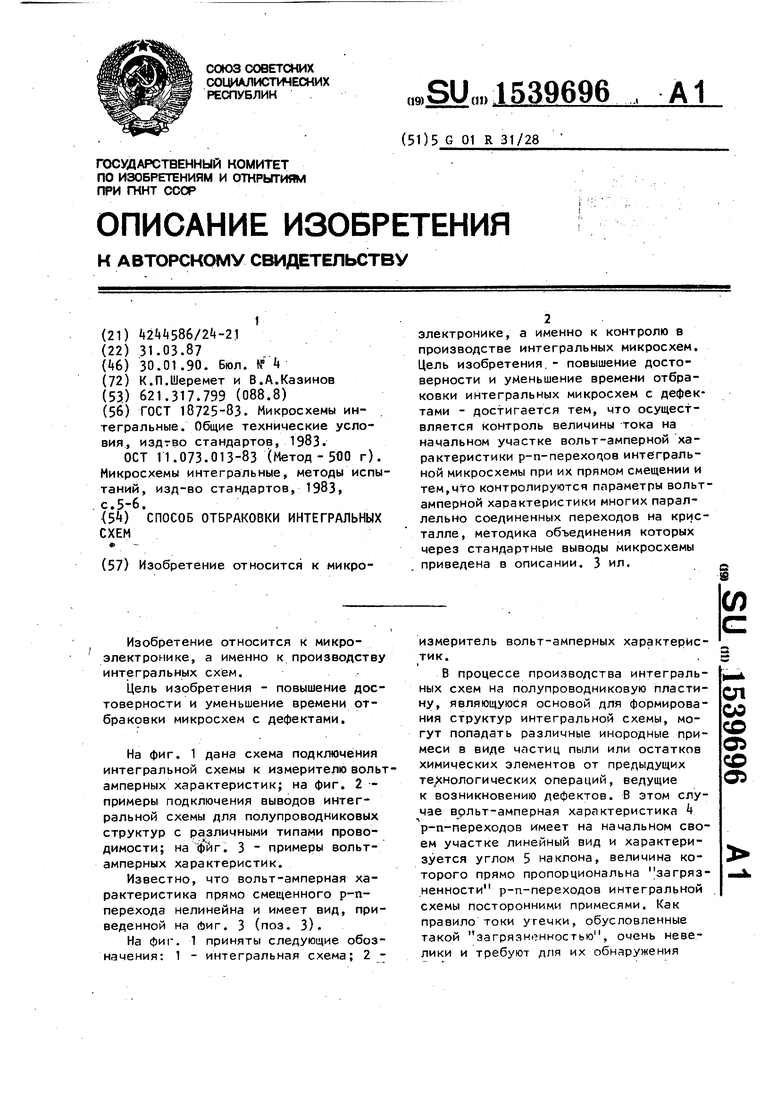

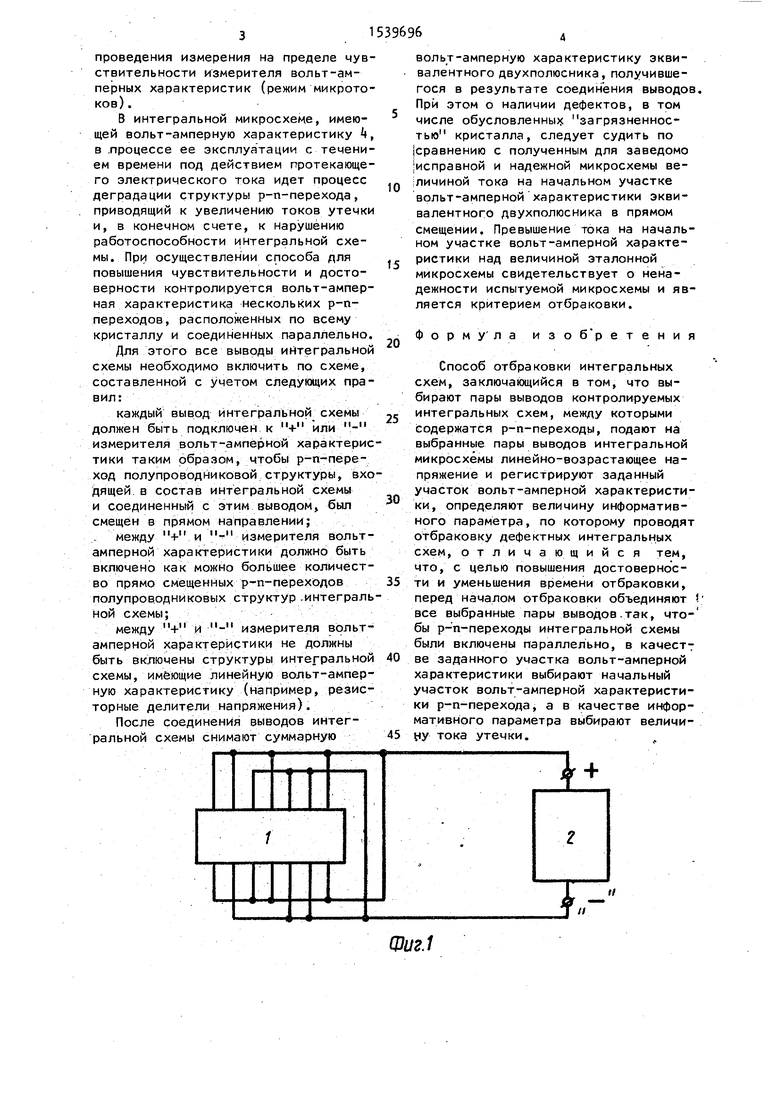

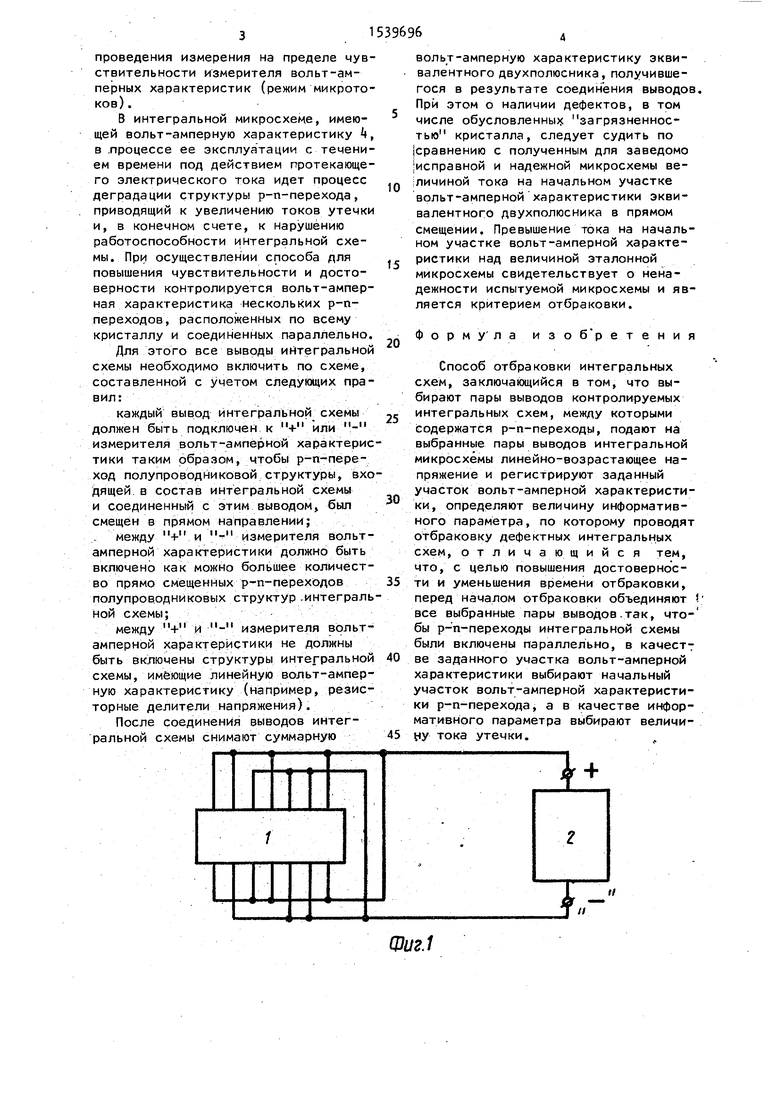

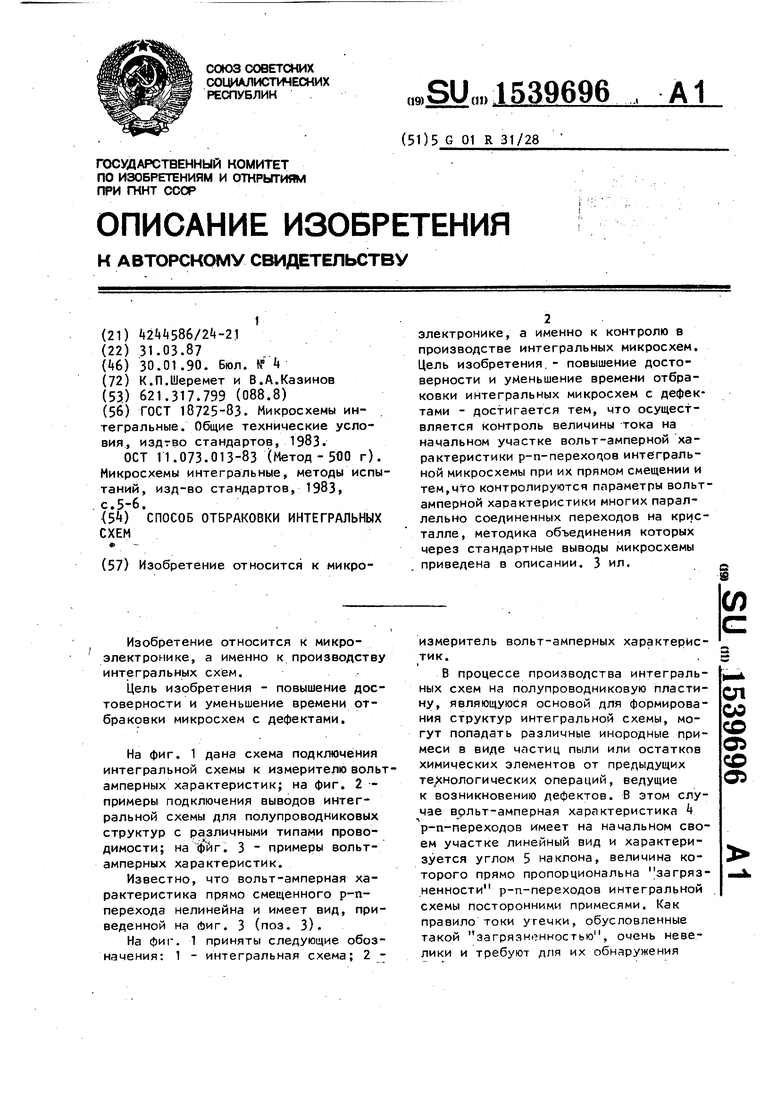

На фиг. 1 дана схема подключения интегральной схемы к измерителю вольт- амперных характеристик; на фиг. 2- примеры подключения выводов интегральной схемы для полупроводниковых структур с различными типами проводимости; на фиг. 3 - примеры вольт- амперных характеристик.

Известно, что вольт-амперная характеристика прямо смещенного р-п- перехода нелинейна и имеет вид, приведенной на йиг. 3 (поз. 3).

На фиг. 1 приняты следующие обозначения: 1 - интегральная схема; 2 измеритель вольт-амперных характеристик.

В процессе производства интегральных схем на полупроводниковую пластину, являющуюся основой для формирования структур интегральной схемы, могут попадать различные инородные примеси в виде частиц пыли или остатков химических элементов от предыдущих технологических операций, ведущие к возникновению дефектов. В этом случае врльт-амперная характеристика k. p-n-переходов имеет на начальном своем участке линейный вид и характеризуется углом 5 наклона, величина которого прямо пропорциональна загрязненности p-n-переходов интегральной схемы посторонними примесями. Как правило токи утечки, обусловленные такой загрязненностью, очень невелики и требуют для их обнаружения

сл

03

со

СЭ СО

оэ

проведения измерения на пределе чувствительности измерителя вольт-амперных характеристик (режим микротоков) .

В интегральной микросхеме, имеющей вольт-амперную характеристику , в процессе ее эксплуатации с течением времени под действием протекающего электрического тока идет процесс деградации структуры р-n-перехода, приводящий к увеличению токов утечки и, в конечном счете, к нарушению работоспособности интегральной схемы. При осуществлении способа для повышения чувствительности и достоверности контролируется вольт-амперная характеристика нескольких р-п- переходов, расположенных по всему кристаллу и соединенных параллельно.

Для этого все выводы интегральной схемы необходимо включить по схеме, составленной с учетом следующих правил:

каждый вывод интегральной схемы должен быть подключен к + или - измерителя вольт-амперной характеристики таким образом, чтобы р-п-пере- ход полупроводниковой структуры, входящей в состав интегральной схемы и соединенный с этим выводом, был смещен в прямом направлении;

между + и - измерителя вольт- амперной характеристики должно быть включено как можно большее количество прямо смещенных р-п-переходов полупроводниковых структур .интегральной схемы;

между + и - измерителя вольт- амперной характеристики не должны быть включены структуры интегральной схемы, имеющие линейную вольт-амперную характеристику (например, резис- торные делители напряжения).

После соединения выводов интегральной схемы снимают суммарную

.;

10

15

2о

25

30

35

40

45

вольт-амперную характеристику эквивалентного двухполюсника, получившегося в результате соединения выводов. При этом о наличии дефектов, в том числе обусловленные загрязненностью кристалла, следует судить по Сравнению с полученным для заведомо исправной и надежной микросхемы величиной тока на начальном участке вольт-амперной характеристики эквивалентного двухполюсника в прямом

смещении. Превышение тока на начальном участке вольт-амперной характеристики над величиной эталонной микросхемы свидетельствует о ненадежности испытуемой микросхемы и является критерием отбраковки.

Формула изоб ретения

Способ отбраковки интегральных схем, заключающийся в том, что выбирают пары выводов контролируемых интегральных схем, между которыми содержатся p-n-переходы, подают на выбранные пары выводов интегральной микросхемы линейно-возрастающее напряжение и регистрируют заданный участок вольт-амперной характеристики, определяют величину информативного параметра, по которому проводят отбраковку дефектных интегральных схем, отличающийся тем, что, с целью повышения достоверности и уменьшения времени отбраковки, перед началом отбраковки объединяют все выбранные пары выводов.так, что- бы p-n-переходы интегральной схемы были включены параллельно, в качестт ве заданного участка вольт-амперной характеристики выбирают начальный участок вольт-амперной характеристики р-п-перехода, а в качестве информативного параметра выбирают величину тока утечки.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ РАЗБРАКОВКИ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 2003 |

|

RU2253168C1 |

| СПОСОБ ОТБРАКОВОЧНЫХ ИСПЫТАНИЙ ПОДЛОЖКИ ИЗ ДИЭЛЕКТРИКА ИЛИ ПОЛУПРОВОДНИКА С ТОПОЛОГИЕЙ, ИЗДЕЛИЙ ЭЛЕКТРОННОЙ ТЕХНИКИ НА СТОЙКОСТЬ К ВНЕШНИМ ВОЗДЕЙСТВУЮЩИМ ФАКТОРАМ | 1998 |

|

RU2138830C1 |

| Способ контроля зарядовой стабильности структур диэлектрик-полупроводник с приповерхностным @ - @ -переходом | 1990 |

|

SU1755218A1 |

| СПОСОБ ОТБРАКОВКИ ПОЛУПРОВОДНИКОВЫХ ИЗДЕЛИЙ | 2008 |

|

RU2357263C1 |

| Способ разбраковки структур с @ - @ -переходом по чувствительности к импульсным электрическим перегрузкам | 1990 |

|

SU1785053A1 |

| СПОСОБ ОТБРАКОВКИ ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ | 1991 |

|

RU2010004C1 |

| Способ определения стойкости к радиационным и температурным воздействиям наноэлектронного резонансно-туннельного диода (РТД) на основе многослойных AlGaAs (алюминий, галлий, арсеникум) полупроводниковых гетероструктур | 2015 |

|

RU2606174C1 |

| СПОСОБ ПЕРЕСТРОЙКИ РЕЗОНАНСНОЙ ЧАСТОТЫ ЭКВИВАЛЕНТА КОЛЕБАТЕЛЬНОГО КОНТУРА НА ЭЛЕМЕНТЕ С ВОЛЬТ-АМПЕРНОЙ ХАРАКТЕРИСТИКОЙ S-ТИПА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1993 |

|

RU2099860C1 |

| СПОСОБ РАЗБРАКОВКИ ПОЛУПРОВОДНИКОВЫХ ИЗДЕЛИЙ НА ПЛАСТИНЕ | 2006 |

|

RU2316013C1 |

| СПОСОБ ИЗГОТОВЛЕНИЯ ОГРАНИЧИТЕЛЕЙ НАПРЯЖЕНИЯ | 2017 |

|

RU2651624C1 |

Изобретение относится к микроэлектронике, а именно к контролю в производстве интегральных микросхем. Цель изобретения - повышение достоверности и уменьшение времени отбраковки интегральных микросхем с дефектами-достигается тем, что осуществляется контроль величины тока на начальном участке вольт-амперной характеристики P-H-переходов интегральной микросхемы при их прямом смещении и тем, что контролируются параметры вольт-амперной характеристики многих параллельно соединенных переходов на кристалле, методика объединения которых через стандартные выводы микросхемы приведена в описании. 3 ил.

1±

ТгФиг.1

--

Фиг-t

фиг.З

и

| Бумагосшиватель | 1929 |

|

SU18725A1 |

| Микросхемы ин- | |||

| тегральные | |||

| Общие технические условия, издтво стандартов, 1983 | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Микросхемы интегральные, методы испытаний, изд-во стандартов, 1983, с.5-6 | |||

Авторы

Даты

1990-01-30—Публикация

1987-03-31—Подача