Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при создании запоминающих устройств с встроенной коррекцией ошибок в интегральном исполнении.

Целью изобретения является повышение надежности устройства.

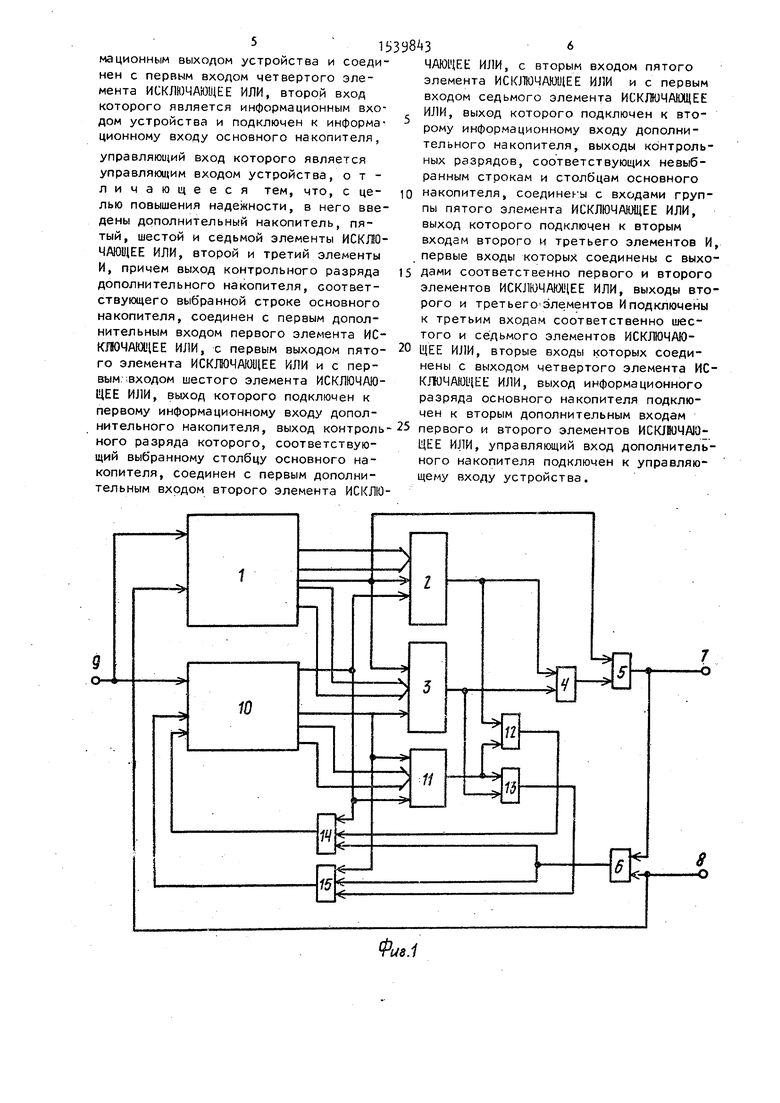

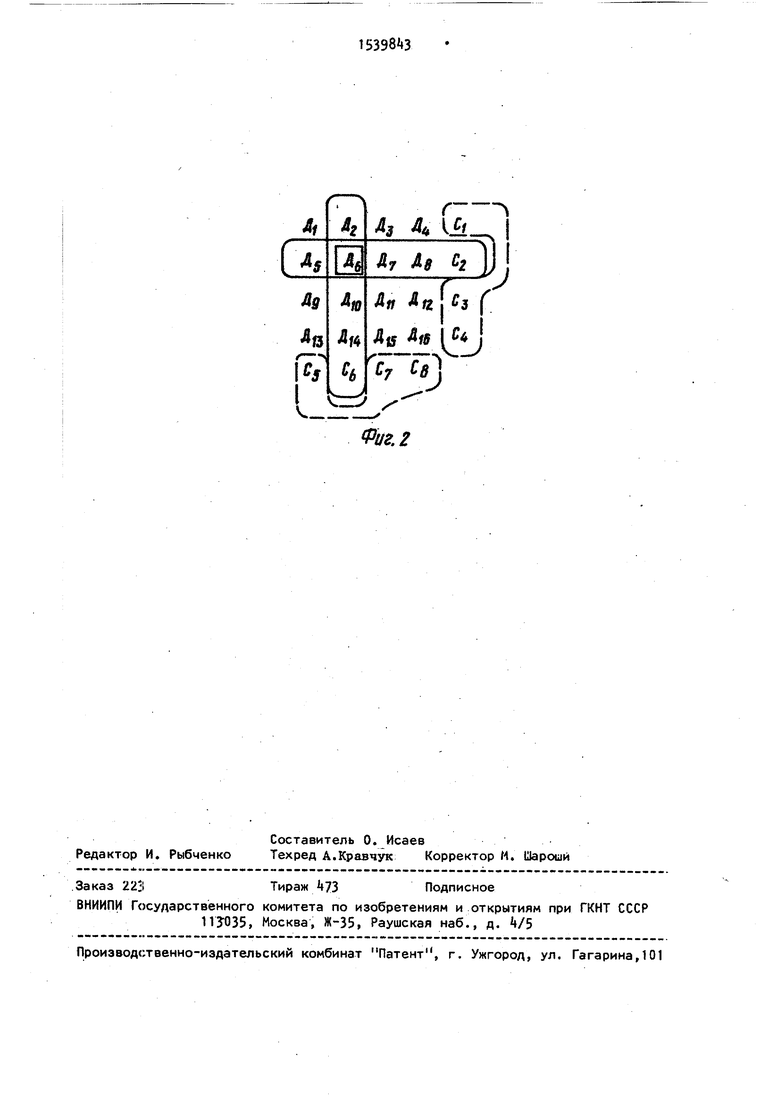

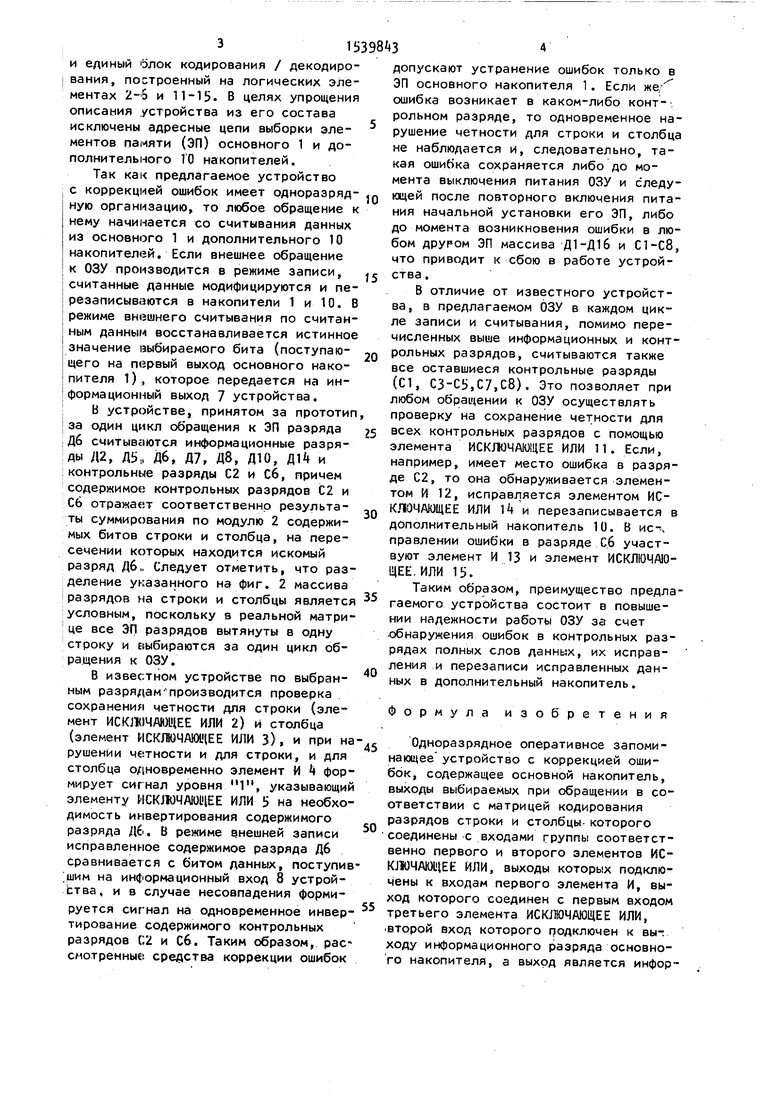

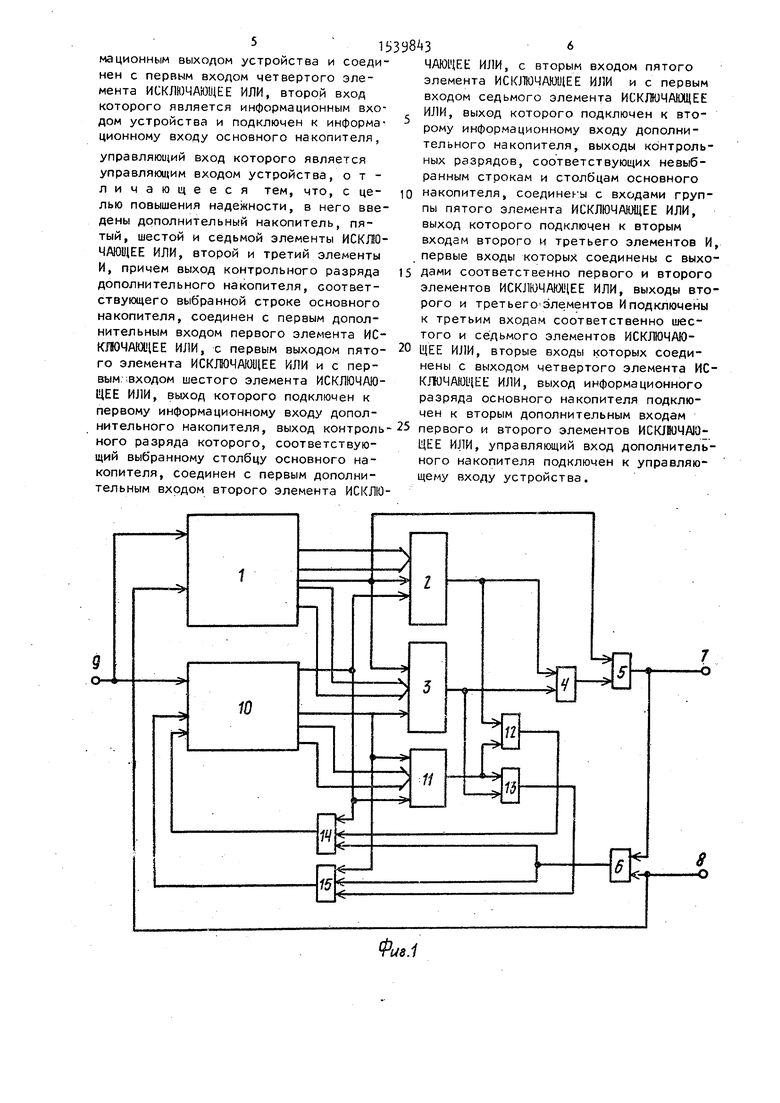

На фиг. 1 показана схема одноразрядного оперативного запоминающего устройства с встроенной коррекцией ошибок; на фиг. 2 - пример массива информационных и контрольных разрядов, для которого пунктирными и сплошными линиями выделены разряды, считываемые соответственно из дополнительного и основного накопителей.

Устройство содержит основной накопитель 1, первый 2 и второй 3 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, первый элемент И 4, третий 5 и четвертый 6 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, информационные выход 7 и вход 8 устройства, управляющий вход 9 устройства, дополнительный накопитель 10, пятый элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 11, второй 12 и третий 13 элементы И, шестой 14 и седьмой 15 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ;

Устройство работает следующим образом.

Исправление однократных ошибок в массиве информационных битов Д1-Д16 (фиг. 2) в предлагаемом одноразрядном оперативном запоминающем устройстве (ОЗУ) основано на использовании итера-. ционного кода. Поэтому в состав устройства входят дополнительный накопитель 1U контрольных разрядов (С1-С8)

сл

со со

00 4

со

и единый блок кодирования / декодирования, построенный на логических элементах 2-6 и 11-15. В целях упрощения описания устройства из его состава исключены адресные цепи выборки эле- ментов памяти (ЭП) основного 1 и дополнительного 10 накопителей.

Так как предлагаемое устройство с коррекцией ошибок имеет однораэряд- ную организацию, то любое обращение к нему начинается со считывания данных из основного 1 и дополнительного 10 накопителей. Если внешнее обращение к ОЗУ производится в режиме записи, считанные данные модифицируются и перезаписываются в накопители 1 и 10. В режиме внешнего считывания по считанным данным восстанавливается истинное значение выбираемого бита (поступаю- щего на первый выход основного накопителя 1), которое передается на информационный выход 7 устройства.

В устройстве, принятом за прототип за один цикл обращения к ЭП разряда Дб считываются информационные разряды Д2, Д5, Дб, Д7, Д8, ДЮ, ДЙ и контрольные разряды С2 и Сб, причем содержимое контрольных разрядов С2 и СЬ отражает соответственно результаты суммирования по модулю 2 содержимых битов строки и столбца, на пересечении которых находится искомый разряд Дб. Следует отметить, что разделение указанного на фиг. 2 массива разрядов на строки и столбцы является условным, поскольку в реальной матрице все ЭП разрядов вытянуты в одну строку и выбираются за один цикл обращения к ОЗУ.

В известном устройстве по выбранным разрядам производится проверка сохранения четности для строки (элемент ИСКЛОЧАЩЕЕ ИЛИ 2) и столбца (элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 3), и при на рушении четности и для строки, и для столбца одновременно элемент И 4 формирует сигнал уровня , указывающий элементу ИСКЛЮЧАЮЩЕЕ ИЛИ 5 на необходимость инвертирования содержимого разряда Дб. В режиме внешней записи исправленное содержимое разряда Дб сравнивается с битом данных, поступив ,шим на информационный вход 8 устройства, и в случае несовпадения формируется сигнал на одновременное инвер- тирование содержимого контрольных разрядов С2 и Сб. Таким образом, рас смотренные средства коррекции ошибок

0

5 5

д5

0

допускают устранение ошибок только в ЭП основного накопителя 1. Если же ошибка возникает в каком-либо контрольном разряде, то одновременное нарушение четности для строки и столбца не наблюдается и, следовательно, такая ошибка сохраняется либо до момента выключения питания ОЗУ и следующей после повторного включения питания начальной установки его ЭП, либо до момента возникновения ошибки в любом друром ЭП массива Д1-Д16 и С1-С8, что приводит к сбою в работе устройства.

В отличие от известного устройства, в предлагаемом ОЗУ в каждом цикле записи и считывания, помимо перечисленных выше информационных и контрольных разрядов, считываются также все оставшиеся контрольные разряды (С1, СЗ-С5,С7,С8). Это позволяет при любом обращении к ОЗУ осуществлять проверку на сохранение четности для всех контрольных разрядов с помощью элемента ИСКЛОЧАЩЕЕ ИЛИ 11. Если, например, имеет место ошибка в разряде С2, то она обнаруживается элементом И 12, исправляется элементом ИСКЛЮЧАЮЩЕЕ ИЛИ Ц и перезаписывается в дополнительный накопитель 10. В ис--. правлении ошибки в разряде Сб участвуют элемент И 13 и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15.

Таким образом, преимущество предлагаемого устройства состоит в повышении надежности работы ОЗУ за счет обнаружения ошибок в контрольных разрядах полных слов даннь х, их исправления и перезаписи исправленных данных в дополнительный накопитель.

Формула изобретения

Одноразрядное оперативнее запоминающее устройство с коррекцией ошибок, содержащее основной накопитель, выходы выбираемых при обращении в соответствии с матрицей кодирования разрядов строки и столбцы-которого соединены с входами группы соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых подключены к входам первого элемента И, выход которого соединен с первым входом третьего элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого подключен к вы-, ходу информационного разряда основно- го накопителя, а выход является инфор5 1

мационным выходом устройства и соеди нен с первым входом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого является информационным входом устройства и подключен к информационному входу основного накопителя,

управляющий вход которого является управляющим входом устройства, отличающееся тем, что, с целью повышения надежности, в него введены дополнительный накопитель, пятый, шестой и седьмой элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, второй и третий элементы И, причем выход контрольного разряда дополнительного накопителя, соответствующего выбранной строке основного накопителя, соединен с первым дополнительным входом первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, с первым выходом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом шестого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к первому информационному входу дополнительного накопителя, выход контроль ного разряда которого, соответствующий выбранному столбцу основного накопителя, соединен с первым дополнительным входом второго элемента ИСКЛЮ

ЗЭВЬЗ6

ЧАЮЩЕЕ ИЛИ, с вторым входом пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и с первым входом седьмого элемента ИСКЛЮЧАЮЩЕЕ 5 ИЛИ, выход которого подключен к второму информационному входу дополнительного накопителя, выходы контрольных разрядов, соответствующих невыбранным строкам и столбцам основного Ю накопителя, соединеьы с входами группы пятого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого подключен к вторым входам второго и третьего элементов И, первые входы которых соединены с выхо- 15 дами соответственно первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы второго и третьего элементов И подключены к третьим входам соответственно шестого и седьмого элементов ИСКЛЮЧАЮ- 20 ЩЈЕ ИЛИ, вторые входы которых соединены с выходом четвертого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход информационного разряда основного накопителя подключен к вторым дополнительным входам 25 первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, управляющий вход дополнительного накопителя подключен к управляющему входу устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Запоминающее устройство | 1990 |

|

SU1801227A3 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО | 2004 |

|

RU2297033C2 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297030C2 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО ХРАНЕНИЯ ИНФОРМАЦИИ | 2004 |

|

RU2297034C2 |

| ОТКАЗОУСТОЙЧИВОЕ УСТРОЙСТВО | 2004 |

|

RU2297031C2 |

| ОТКАЗОУСТОЙЧИВОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297035C2 |

| Запоминающее устройство с самоконтролем | 1987 |

|

SU1432613A1 |

| САМОКОРРЕКТИРУЮЩЕЕСЯ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2297032C2 |

| Запоминающее устройство с контролем и коррекцией ошибок | 1983 |

|

SU1117715A1 |

| Запоминающее устройство с коррекцией ошибок | 1983 |

|

SU1127012A1 |

Изобретение относится к вычислительной технике и микроэлектронике и может быть использовано при создании запоминающих устройств с встроенной коррекцией ошибок в интегральном исполнении. Целью изобретения является повышение надежности устройства. Устройство содержит основной и дополнительный накопители, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ, с первого по седьмой, и элементы И, с первого по третий. Цель изобретения достигается тем, что в каждом цикле обращения к устройству, помимо выбираемых информационных и контрольных разрядов строки и столбца итерационного кода, считываются и проверяются по четности все оставшиеся контрольные разряды, что позволяет обнаруживать ошибки в контрольных разрядах, исправлять их и восстанавливать истинное значение в дополнительном накопителе в такте записи цикла обращения. 2 ил.

9 о-

7 -о

Фиг. г

| Патент США Н° 4561095, кл | |||

| Гидравлическая передача, могущая служить насосом | 1921 |

|

SU371A1 |

| Приспособление для установки двигателя в топках с получающими возвратно-поступательное перемещение колосниками | 1917 |

|

SU1985A1 |

| Патент США № 4456980, кл | |||

| Станок для нарезания зубьев на гребнях | 1921 |

|

SU365A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1990-01-30—Публикация

1987-07-06—Подача