tjiib

Од

tsd

а

со

Изобретение относитсл к вычислительной технике, в частности к запоминающим устройствам.

Цель изобретения - повышение достоверности функционирования.

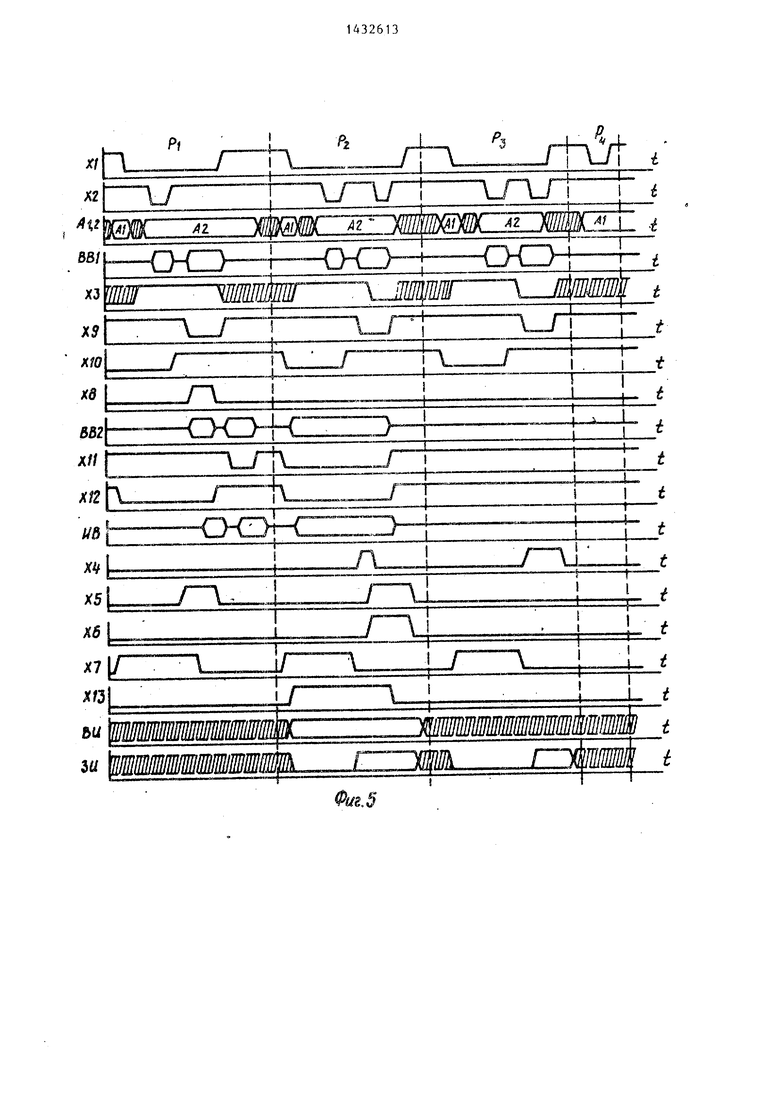

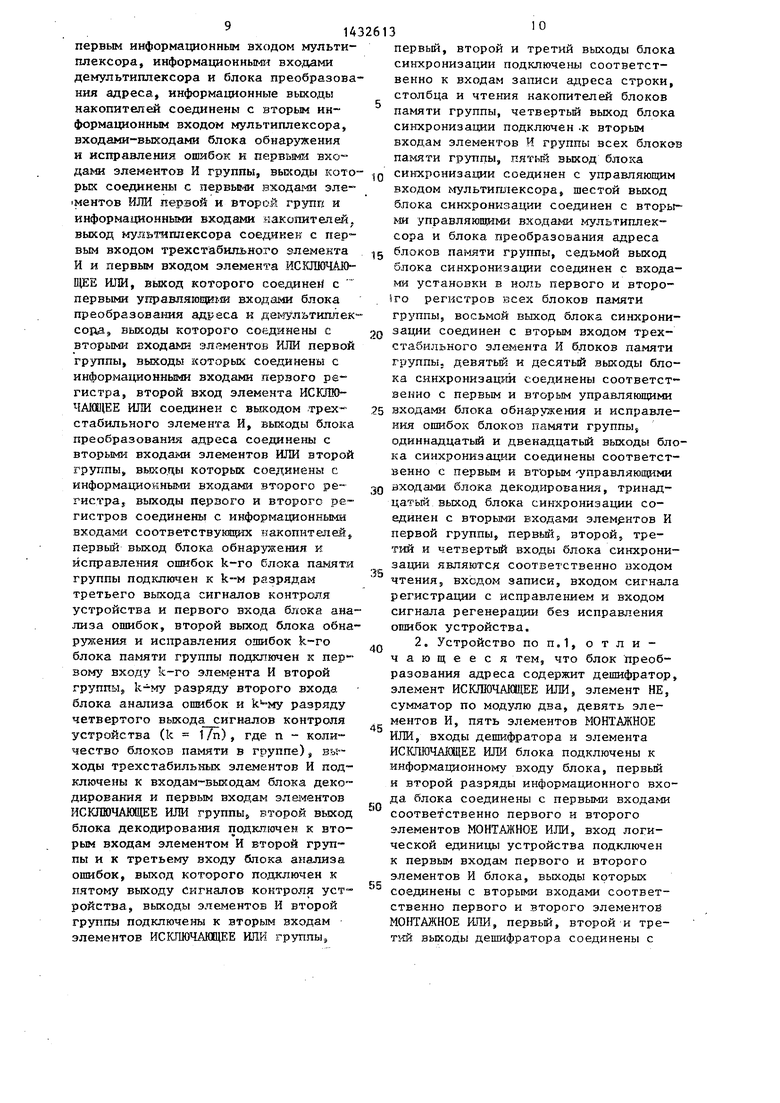

На фиг, 1 представлена функциональная схема устройства5 на фиг,2 функциональная схема блока преобразования адреса} на фиг. 3 функционал ная схема блока анализа ошибок,- на фиг. 4 - показана Н-матрица используемого в блоке обнаружения и исправления ошибок корректирующего кода; на фиг. 5 - временные диаграммы ра- боты блока синхронизации и устройства; на фиг„ 6 - структура используемого в устройстве корректирующего кода и принцип коррекции ошибок раз- ли1Л1ой кратности.

Устройство содержит блоки Ij-l памяти группы, регистр 2 адреса, адресный 3 и. информационный 4 входы устройства, группу 5 элементов Ид блок 6 декодирования, группу Т эле- ментов ИСКЛЮЧАМЦЕЕ ИЛИ, группу 8 элементов И, блок 9 анализа ошибок,, блок 10 синхронизации, входы 11 чтения, 12 записи, сигнала регенерации

с исправлением 13 и без исправления

14 ошибок устройства, ка:«(дьй блок памяти содержит накопители , блок 16 обнаружения и исправления ошибок, мультиплексор 17, дёмульти- плексор 18, группу 19 элементов И блок 20 преобразования адреса, груп- пу 21 и 22 элементов ИЛИ, регистры 23 и 24, элемент ИСКПННАЩЕЕ ИЛИ 25, трехстабильньм элемент И 26, инфор- мационньй выход 27 устройства, выходы 28-32 сигналов контроля устройст- ва.

Блок 20 преобразования адреса содержит дешифратор 33, элемент 34 ИСКПЮЧАЩЕЕ ИЛИ, сумматор 35 по модулю два, элементы И 36-43, элемент НЕ 44, элемент И 45, элементы МОНТАЖНОЕ ИЛИ 46-50.

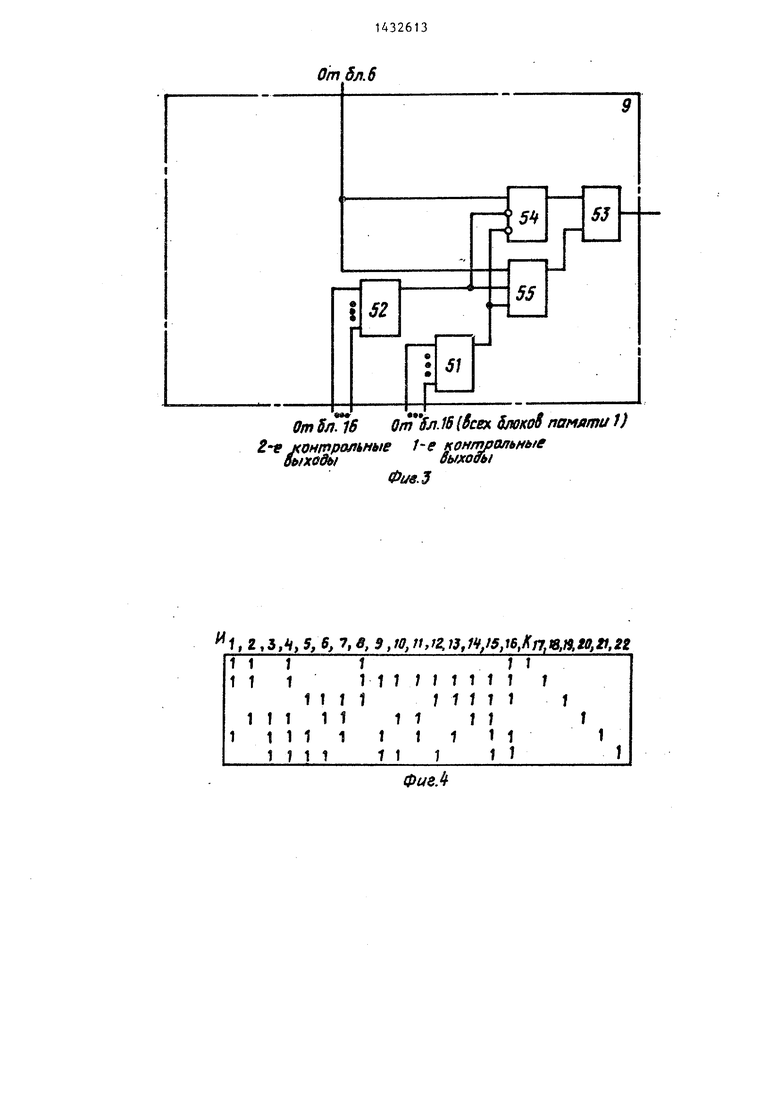

Блок 9 анализа ошибок содержит элементы ИЛИ 51-53, элементы И 54 и 55.

На фиг. 4 обозначены информацион ные И 1-16 и контрольные К17-22 разряды кода, используемого в блоках t памяти.

На фиг. 5 обозначены Р1 - режим чтения, Р2 - режим записи, РЗ - регенерация с исправлением ошибок Р4 - регенерация без исправления оши

п j п

5

0

0

5

5

бок, Х1-Х13 сигналы управлегшя с выходов один - тринадцать блока 10, А1,2 - коды адреса на адресных входах накопителей 15 блоков 1 памяти,

881- информадаонные и контрольные сигналы на входах-выходах блока 16,

882- информац {онные и контрольные сигналы на входах-выходах блока 6, ИВ - информационные сигналы на выходах 27 устройства, ВИ - входные информационные сигналы на входах 4 устройства, ЗИ - записываемые информационные и контрольные сигналы на информационных входах накопителей 15 блоков 1 памяти.

Блок 16 и блок 6 выполняют аналогичные функции и содержат блоки задания направления обмена информационными и контрольными разрядами, блок управления, блок формирования признаков одиночной и многократной (двойной) ошибки. В таблице указаны режимы работы блока 16 (6) в зависимости от значений управлякшщх сигналов Х9, Х10, (XII, Х12), поступающих на их входы,

Блок 10 построен на ждущих мультивибраторах типа К 155 -АГЗ .и формирует управляющие сигналы Х1-Х13 согласно временной диаграмме, приведенной на фиг, 3,

Накопители 15 блоков 1 памяти представляют собой одноразрядные схемы памяти динамического типа с тремя состояниями выхода.

В группу 7 входят элементы ИСКЛЮЧАЮЩЕЕ РШИ по числу информационных разрядов. Адрес,-поступакядий по входам 3 на регистр 2 состоит из трех частей. Первая часть - адрес строки накопителей 15, вторая часть - адрес столбца накопителей 15 и третья чисть (младшие разряды) - номер разряда в считанном слове. В процессе работы в регистр 2 вначале поступает первая и третья части адреса, а затем на место первой части - вторая часть адреса.

Блок 20 предназначен для преобразования младших разрядов адреса в , столбисы контрольной матрицы используемого корректирующего кода. Необходимость преобразования вызвана тем, что в режиме записи в накопители 15 каясдого блока 1 памяти за письшается только один разряд, а ему соответствует определенный столбец контрольной матрицы кода. Между младшими

разрядами адреса и столбца контрольной матрицы имеется взаимно однозначное соответствие. Поэтому вместо формирования новых контрольньк разрядов достаточно сложить по модулю два их старые значения и преобразованньм код младших разрядов адреса. Код младших разрядов адреса и столбцы контрольной матрицы различаются в 1, 2, 4, 8 и 16-м столбцах. Поэтому при поступлении этих кодов адреса, а их признаком является наличие только одной единицы, блок 20 преобразовьша ет их соответственно в код 25, 26, 27, 28, 29. Кроме того, блок 20 формирует сигнал четности столбца контрольной матрицы, который также необходимо корректировать в числе контрольных разрядов при записи.

Дешифратор 33 преобразовывает унитарный код в двоичный. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 34 вьшвляет наличие одной единицы в поступившем коде адреса и разрешает вьдачу преобразованного кода на выход. При любом другом коде адреса он проходит на выход блока 20 без изменения. Сумматор 35 по модулю два формирует по вьщаваемому коду сигнал четности.

Устройство работает следующим образом.

Режим чтения. При считьшании на вход 3 адреса поступает адрес, а на вход 11 блока 10 - сигнал чтения. По сигналу чтения блок 10 формирует последовательность управляющих сигнало Х1-Х13 (фиг.5), С выхода блока 10- сигнал XI поступает на первый управляющий вход накопителей 15 блоков 1 памяти. По спаду фронта этого сигнал в накопителях 15 фиксируется адрес А1 строки, а по сигналу Х2, поступающему на их вторые управляющие входы с выхода блока 10, фиксируется адрес А2 столбца. Сигнал ХЗ на третьих управляющих входах накопителей 15 равен единице, и на выходах накопителе 15 появляется считанная информация. По сигналам Х9 и Х10, поступающим из блока 10 на управлякадие входы блока 16, производится запись информационных и контрольных разрядов в блок 16 а также вьздача откорректированных разрядов из него. Откорректированные разряды с входов-выходов блока 16 поступают на вторые входы мультиплексора 17, на первые входы которого поступают младшие разряды адреса из

0

5

5

0

5

0

5

0

регистра 2. При поступлении единичного сигнала Х5 из блока 10 на третий вход мультиплексора в соответствии с младшими разрядами адреса на выход мультиплексора выдается один из разрядов. По единичному сигналу Х8 элемент И 26 выдает этот разряд на выход блока памяти. Поскольку считьшание происходит одновременно во всех блоках 1 памяти, то на входы-выходы бло-. ка 6 поступает 72 разряда, среди которых имеются информационные и контрольные .

Пр сигналам XII и XI2 из блока 10, поступающим на управляющие входы блока 6, производится запись информационных и контрольных разрядов в блок 6, а также вьщача откорректированных разрядов из него. Откорректированные разряды с входов-выходов блока 6 поступают на группу 7, его производится дополнительная коррек1щя и выдача информационных разрядов на выход 27 устройства.

Режим записи. При записи на вход

3адреса поступает адрес, на вход

4- записьшается информация, на вход 12 блока 10 - сигнал записи. По этому сигналу блок 10 формирует управляющие сигналы Х1-Х13 (фиг.5). С выхода блока 10 сигнал Х1 поступает на первьй управляющий вход накопителей 15 блоков 1 памяти. По спаду фронта этого сигнала в накопителях 15 фик- скруется адрес А1 строки, а по сигналу Х2, поступающему на их вторые управляющие входы с выхода блока 10, фиксируется адрес А2 столбца. Сигнал ХЗ на третьих управляющих входах накопителей 15 равен единице, и на выходах накопителей . 15 появляется считанная информация. По сигналам Х9 и XIО, поступающим из блока 10 на управляющие входы блока 16, производится запись информационных и контрольных разрядов в блок 16 обнаружения и исправления ошибок, а также выдача откорректированных разрядов из него. Откорректированные разряды с входов- выходов блока 16 поступают на вторые входы мультиплексора 17, на первые входы которого поступают младшие разряды адреса из регистра 2. При поступлении единичного сигнала Х5 из блока 10 на третий вход мультиплексора в соответствии с младшими разрядами адреса на его выход вьщается один из разрядов. Одновременно со считыванием информации из накопителей 15 выходная информация, подааежащая .запиеи по сигналу XI3, поступающему на второй вход группы 5 элементов И из блока 10, вьщается на входы-выходы соот ветствукщих блоков 1 памяти и входы- выходы блока 6, в последкетз формщ)у- ются контрольные разряды:, которые за тем также подаются на вкоды-вьжоды соответствукшщх блоков 1 памяти,

В блоке 1 памяти разряд, считанный по данном / адресу из накопятех{аЙ с выхода мультиплексора 17 и носту- пивншй в блок памяти (для записи) сравниваются элементом ИСКЛ10 1АЩЕЕ ИЛИ 25, Если они равны, то сигнал сравнения равен яулк если нет то гдини1де. Перед вьрача 1 ннформацин из блока 16 регистры 23 ;д 24 обкуляф

ются единичньм сигнсшок S7, а при вы даче информации из блока 16 она через группы 21 и 22 эле1ментоз ИЛИ за- гшсьиБается в регистры 23 и 24, В регистр 23 записываются икформащюнные разряды, а в регистр 24 - контроль - ные.

По сигналу Хб сигнал сравнения через демультиплексор 18 и rp.v nny 21 элементов ИЛИ поступает на один из входов регистра 23, а именно на тот,, которьй соответствует записываемому разряду. Поскольку регистры 23 и 24 имеют счатнь е входы то прм. пастуш е нии сигнала сравнения в регистр 23 происходит сложение по модулю два этого сигнала и информащж,, записаи™ ной в регистре. При этом сигнал сравнения может быть равен нулю или единице с

Рассмотрим случай, при котором сигнал сравнения равен единице Это означает, что записьгааемьй разряд не согласован со считанным. Например с, считана единица, а записать необходимо ноль или ноль, а записать необходимо единицус В o6oi- x с.т1згчаях (Сложение по модулю два считанного разряда и сигнала сравнения приводит к появлен1по такого значения данного разряда, которьй необходимо записать Например, считана единица,, а записат необходимо ноль, В этом случае, нал сравнения равен единице и сложение его по модулю два со считанным разрядом (равньм единице) приводит- к появлению в данном разряде нулевого значения что и требуется. В случаеэ когда считан ноль а необходимо запиo

0

5

сать единицуJ сигнал сравнения равен и его сложение по модулю два со считанным разрядом (равным нулю) приводит к появлению в данном разряде единичного значения, что и требуется.

До появления сигнала сравнения в регистр 24 производится запись конт- рольных разрядов из блока 16 через 19 по сигналу Х4. При несогла- совани1-д записываемого и считанного разрядов необходимо скорректировать контрольные разрады так, чтобы они соотзетствовагш записьшаемой инфор- 5 мадии. При зтон если сигнал сравне- кап равен единицвд то д.г1я приведения в соответствие контро. льных разрядов записываег ой информации достаточно л прежним значениям контрольных раз- ря/1,ов прибавить по модулю два стол бец контрольной матрицы, соответствующий записьшаемо Еу разряду. Блок 20 по а,цресу записьпзаеьюго разряда . форг шрует данный столбец и по единичному сигналу сравнения и разрешающему сигналу Хб вьщает его через группу 22 злементов ИТМ на счетные входы регистра 24, где производится сложение по модулю два о контрольными разрядги-да.

При согласонанки записьгваемого разряда и считанного сигнал сравнения равен нулю и изметьзний в регистрах 23 к 24 не происходит. Информационные к контрольные разряды с ходов регистров 23 и 24 поступают на вкоды соответствующих накопителей 15, и rfo спаду фронта сигнала Х2 производится их запись.

Регенерация с исправлением ошибок (фиг.54 РЗ). В этом режиме производится считьшание5 исправление ошибок 3 блоке 16 и запись исправленной информации через группу 19 элементов И в накопители 15,

Регенерация без исправления ошибок (фиг.З Р4), В этом режиме в накопители 15 подается только а,прес А1 строки и по спаду фронта сигнала Х1 в накопителях 15 производится регене- ращ-гя.

Рассмотрим работу устройства при исправлении ошибок.

Допустим, что произошла одиночная ошибка (фиг,6, случай 1). Эта ошибка S исправляется кодом Хзмминга в блоке 16 первого блока 1 памяти.

Двухкратная опмбка (фиг,6, случай 2), Для блоков 1 памяти эти опиб5

0

5

0

14

ки воспринимаются как одиночные и исправляются в них блоками 16, Аналогично, при возникновении ошибок любой кратности, располагающихся по одной в блоках памяти, такие ошибки будут исправлены.

Двойная ошибка в одном блоке памяти (фиг.6, случай 3). В блоке памяти 1 эта ошибка не может быть исправле- на, поскольку превьш1ает корректирующую способность кода внутри блока памяти. Но, поскольку на выход блоков 1 памяти в.ыдаются только по одному разряду (например, А-е), в составе выданных разрядов будет только одна ошибка, которая исправляется кодом Хэмминга в блоке 6,

Трехкратная ошибка (фиг.6, случай 4). Эта ошибка в блоке 16 не может быть исправлена, однако, поскольку на выход блока памяти выдается только один разряд, такая ошибка исправляется в блоке 6 кодом Хэмминга. Аналогично исправляются ошибки любой кратности в пределах одного блока памяти.

Трехкратная ошибка (фиг.6, случай 5). При такой конфигурации ошибки в первом блоке памяти она отожде- ствляется как двухкратная, а во втором блоке памяти - как одиночная. Во втором блоке памяти ошибка исправляется блоком 16. Далее оставшаяся двукратная ошибка исправляется, как и в случае 3.

Четырехкратная ошибка (фиг,6, случай 6). При этом ошибки располагаются по две в двух блоках памяти. Такая ошибка кодом Хэмминга ни в блоках 16 блоков памяти, ни в блоке 6 декодирования не может быть исправлена, так как и в блоках памяти, и на их выходах (при выдаче 9-х или 10-х разрядов) ошибка является двухкратной. Исправление производится в группе 7 следукяцим образом. Сигналы обнаружения двойной ошибки из блоков 16 блоков памяти поступают -на первые входы группы 8 элементов И, на вторые входы подается разрешающий сигнал о ; двойной ошибке из блока 6. С выхода группы 8 элементов И сигналы обнаружения двойных ошибок в качестве единичных сигналов коррекции поступавзт на входы группы 7, где они складьта- ются с соответствующими информационными разрядами. В результате этого происходит их коррекция и на выход

8

5

„

5

5

0

27 устройства вьщается исправленная

информация.

I Блок 9 предназначен для обнаружения некорректируемых ошибок. Этот факт определяется по наличию нулевых сигналов обнаружения одиночных и двойных ошибок в блоках 1 памяти и единичного сигнала обнаружения двойной ошибки в блоке 6 (фиг.6, случай 7) либо по наличию единичных сигналов обнаружения одиночной и двойной ошибки в блоках 1 памяти и двойной ошибки в блоке 6 (фиг.6, случай 8). Ука- ранные ситуации определяются с помо- (цью элементов И 54 и 55 и элементов ИЛИ 51-53. На выход блока анализа ошибок из элемента ИЛИ 53 вьщается сигнал обнаружения некорректируемой ошибки.

Формула изобретения

1. Запоминающее устройство с самоконтролем, содержащее регистр адреса, группу блоков памяти, группу элементов ИСКЛЮЧАЩЕЕ ИЛИ, блок декодирования, причем информационный вход регистра адреса подключен к адресному входу устройства, выход р.егистра ад реса подключен к адресным входам блоков памяти группы, выходы элементов ИСКЛЮЧАЩЕЕ ИЛИ группы подключены к соответствующим разрядам информационного выхода устройства, отличающееся тем, что, с целью по- вьшения достоверности функционирования, в негр введены две группы элементов И, блок анализа ошибок и блок синхронизации, причем каждьм блок памяти группы содержит группу накопи- телей, мультиплексор, блок обнаружения и исправления ошибок, элемент ИСКЛЮЧАЩЕЕ ИЛИ, трехстабильньй элемент И, демультиплексор, два регистра, две группы элементов ИЛИ, группу элементов И и блок преобразования адреса, причем информационный вход устройства подключен к первым входам элементов И первой группы, выходы которых подключены к первым входам элементов ИСКЛЮЧАЩЕЕ ИЖ группы и к входам-выходам блока декодирования, первьй и второй выходы которого подключены к первому и второму выходам сигналов контроля устройства, причем в каждом блоке памяти группы адресный вход блока памяти соединен с адресными входами накопителей группы.

первым информационным входом мультиплексора, информационныг.1И вхо, демультиплексора и блока преобразования адреса, информационные выходы накопителей соединены с вторым ин- формагщонным входом мультиплексора, входами-вькодами блока обнаружения и исправления ошибок и первыми входами элементов И группы, вьвсоды которых соединены с первыми входами эле |ментов ИЛИ первой и второй групц и информационными вxoдa ш накопителей. выход MyjibTMraieKcopa соедннек с первым входом трехстабильного элемента И и первым входом элемента ИСКЛЮЧАКЬ- DIEE ИЛИ, вькод которого соединен с первыми управляющиг-ш входами блока преобразования адреса и де1«гультиплек- coixa выходы которого соединены с вторьми входами элементов ИЛИ первой группы, выходы которых соединены с информационными входами первого ре гистра, второй вход элемента ИСКЛЮ- ЧА КЬЦЕЕ ИЛИ соединен с вьисодом трех стабильного элемента И, выходы блока преобразования адреса соединены с вторыми входами элементов ИЛИ второй группы, вьосоды которых соединены с информационными входами второго ре- гистра, выходы первого и второго регистров соединены с информационными входами соответствукшщх накопителей, первый выход блока обнаружения и исправления ошибок k-ro блока памяти группы подключен к разрядам третьего выхода сигналов контроля устройства и первого входа бхшка анализа ошибок, второй выход блока обнаружения и исправления ошибок k-ro блока памяти группы подключен к вому входу k-ro элемента И второй rpynnbij k-му разряду второго входа блока анализа ошибок и k -му разряду четвертого выхода сигналов контроля устройства (k f/n), где п - количество блоков памяти в группе), выходы трехстабильных элементов И подключены к входам-выходам блока декодирования и первым входам эле1 1ентов ИСКПЮЧАЮОЩЕ ИЛИ группы, второй выход блока декодирования подключен к вторым входам элементом И второй группы и к третьему входу блока анализа ошибок, выход которого подключен к пятому выходу сигналов контроля устройства, выходы элементов И второй группы подключены к вторым входам элементов ИСКПЮЧАЮЩЕЕ ИЛИ группы.

0

5

0

5

0

5

0

5

0

5

первый, второй и третий выходы блока синхронизации подключены соответственно к входам записи адреса строки, столбца и чтения накопителей блоков памяти группы, четвертьй выход блока синхронизации подключен .к вторым входам элементов И группы всех блоков памяти группы, пятьй выход блока синхронизации соединен с управляющим входом ryльтишIeкcopa, шестой выход блока синхронизации соединен с вторы управляющими входа ш мультиплексора и блока преобразования адреса блоков памяти группы, седьмой выход блока синхронизации соединен с входами установки в ноль первого и второ- iro регистров :.зсех блоков памяти грутты, восьмой выход блока синхронизации соединен с вторым входом трек- стабильного эле 3ента И блоков памяти группы, девятьй и десятый выходы блока синхроннзащш соединены соответственно с первым и вторым управляющими входами блока обнаружения и исправления ошибок блоков памяти группы одиннадцатый и двенадцатый выходы блока синхронизации соединены соответственно с первым и вт орым -управляюпщми входах-ш блока, декодирования, тринад- цатьй,выход блока синхронизации соединен с вторьзми входами элементов И первой группы, первьйр второй, третий и четвертый входы блока синхронизации являются соответственно входом чтения, входом записи, входом сигнала регистрации с исправлением и входом сигнала регенерации без исправления ошибок устройства.

2. Устройство по п.1, отличающееся тем, что блок преобразования адреса содержит дешифратор, элемент ИСКЛЮЧАЩЕЕ ИЛИ, элемент НЕ, сумматор по модулю два, девять элементов И, пять элементов МОНТАЖНОЕ ИЛИ, входы дешифратора и элемента ИСКгаоЧАМЦЕЕ ИЛИ блока подключены к информационному входу блока, первьш и второй разряды информационного входа блока соединены с первыми входами соответственно первого и второго элементов МОНТАЖНОЕ ИЛИ, вход логической единицы устройства подключен к первым входам первого и второго элементов И блока, выходы которых соединены с вторыми входами соответственно первого и второго элементов МОНТАЖНОЕ ИДИ, первьй, второй и третий вькоды дешифратора соединены с

первыми входами соответственно третьего, четвертого и пятого элементов И, выходы которых соединены с вторыми входами соответственно третьего, четвертого и пятого элементов МОНТАЖНОЕ ИЛИ, выход элемента ИСКЛЮЧАЩЕЕ ИЛИ соединен с вторыми входами элементов И с первого по пятьй и входом элемента НЕ, третий, четвертый и пятый разряды информационного входа блока соединены с первыми входами соответственно шестого, седьмого и восьмого элементов И блока, выходы которых соединены с первыми . входами соответственно третьего, четвертого и пятого элементов МОНТАЖНОЕ ИЛИ; выход элемента НЕ соединен с вторыми входами с шестого по восьмой элементов И, выходы элементов МОНТАЖНОЕ ИЛИ соединены с входами сумматора по модулю два, первьй и второй входы девятого элемента И подключены соответственно к первому и

второму управляющим входам блока, выходы девятого элемента И блока соединены с третьими входами с первого по восьмой элементов И, выходы , элементов МОНТАЖНОЕ ИЛИ и сумматора по модулю два подключены соответственно к выходам блока.

3. Устройство ПОП.1, отличающееся тем, что блок анализа ошибок содержит три элемента ИЛИ и два элемента И, причем k-e разряды первого и второго входов блока подключены соответственно к k-м. входам первого и второго элементов ЩШ, выходы которых подключены соответственно к первому и второму входам первого и второго элементов И, третьи входы которых подключены к третьему входу блока, выходы первого и второго элементов И подключены соответственно к первому и второму входам третьего элемента ИЛИ, выход которого подключен к вькоду блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство на полупроводниковых динамических элементах памяти | 1987 |

|

SU1525744A1 |

| Запоминающее устройство с автономным контролем | 1990 |

|

SU1785040A1 |

| Запоминающее устройство с самоконтролем | 1986 |

|

SU1411834A1 |

| Оперативное запоминающее устройство с исправлением ошибок | 1988 |

|

SU1674269A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1751762A1 |

| Запоминающее устройство на цилиндрических магнитных доменах | 1990 |

|

SU1737511A1 |

| Оперативное запоминающее устройство с самоконтролем | 1986 |

|

SU1332386A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1985 |

|

SU1274006A1 |

| Запоминающее устройство с самоконтролем | 1988 |

|

SU1569905A1 |

| Устройство обмена информацией между ЭВМ и абонентами | 1990 |

|

SU1835545A1 |

Изобретение относится к вычислительной технике, в частности к запоминающим устройствам. Целью изобрете, ния является повьппение достоверности функционирования. Устройство содержит блоки 1-1т4 памяти группы, регистр 2 адреса, адресный 3 и информационный 4 входы устройства, группу элементов И 5, блок 6 декодирования, группу 7 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, группу элементов И 8, блок 9 анализа ошибок, блок 10 синхронизации, входы 11 чтения, 12 записи, сигнала регенерации с исправлением 13 и без исправления 14 ошибок устройства, каждьй блок памяти содержит накопители 15/- 15 , блок 16 обнаружения и исправления ошибок, мультиплексор 17, демуль- типлексор 18, rpynrty элементов И 19, блок 20 преобразования адреса, группу 21, 22 элементов ИЛИ, регистры 23, 24, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 25, трех- стабильный элемент И 26, информационный выход 27, выходы 28-32 сигналов контроля устройства. Цель достигается пут€м введения средств для обнаружения и исправления ошибок различных типов. 2 3.п. ф-лы, 6 ил. (Л

О

О

Вычисление конт- Входные информацион- Запрещены рольных разрядов ные и вычисленные

контрольные разряды

Прием информа- Входные информацион- ционньк и конт- ные и контрольные рольных разрядов разряды

1 1

Блокировка информации

Выключенное состояние

Коррекция и вы- Выходные исправлен- дача исправлен- ные информационные ной информации разряды

Разрешены

От Sff.Z

От б д. 25 Xff

от §л.Ю

к ёй.П

От дл.б

t,2.3,,5,g, 7, , f, 1Q, 11,12.13, Ш5,1б,/(/7. в,. Щ Д «

1 1 Jt

It 1М 7 ;I t 1 tt f

liltI f t Т7

1 I I 1 tItJ J

11111 t 1 1 11

tillt t1t1

ФиеЛ

Фив.

ЕГЗСШШ i

1 2 3 tf 5 6 1 8 9 Ш 11 12 f6 22

г

3 (/ 5 б 7 б

5

i/2.5

| Запоминающее устройство с автономным контролем | 1984 |

|

SU1215140A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Запоминающее устройство с самоконтролем | 1984 |

|

SU1157575A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-10-23—Публикация

1987-04-02—Подача