Изобретение относится к приборостроению, а именно к технике записи и воспроизведения (передачи) цифровой информации с использованием маркирования информационных комбинаций для обеспечения асинхронного считывания информации с носителя записи.

Цель изобретения заключается в повышении достоверности процесса вы- дел.ения сигналов синхронизации при воспроизведении.

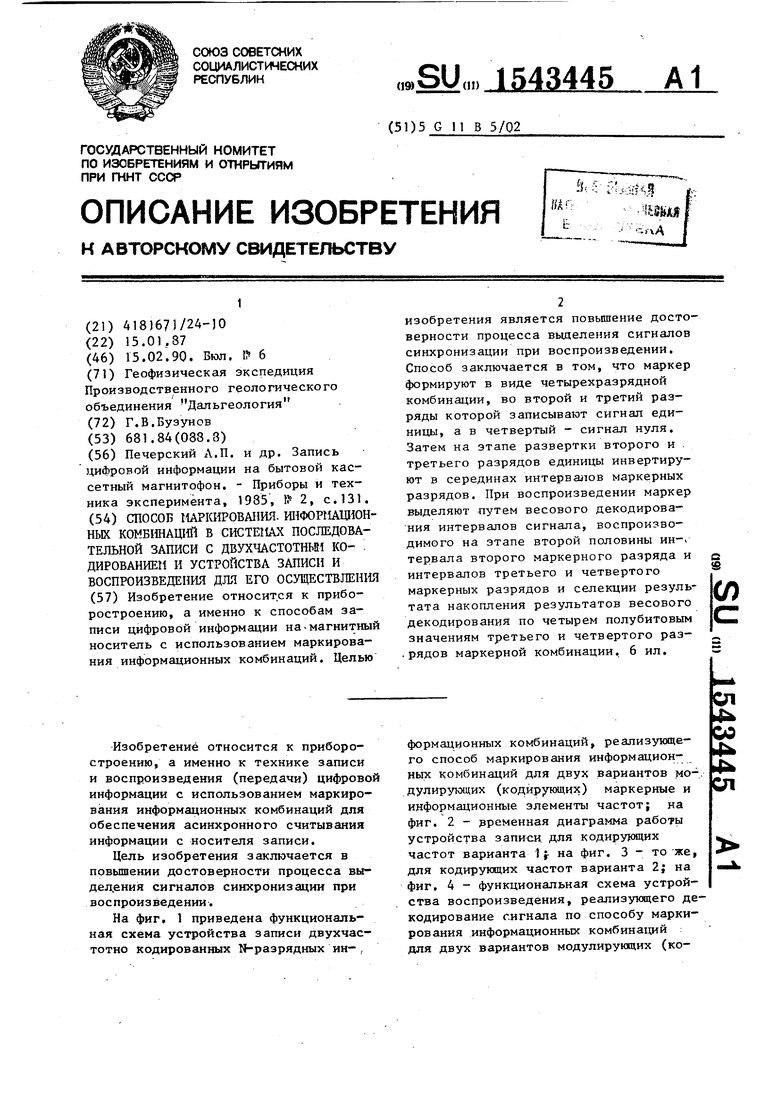

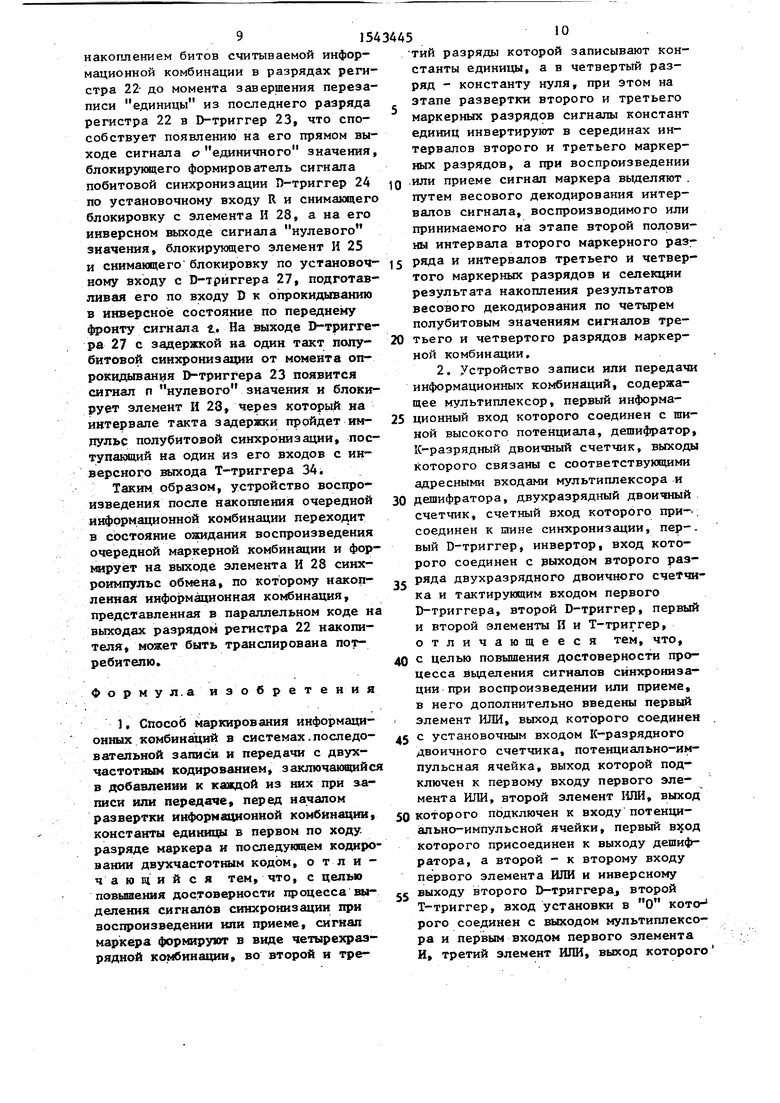

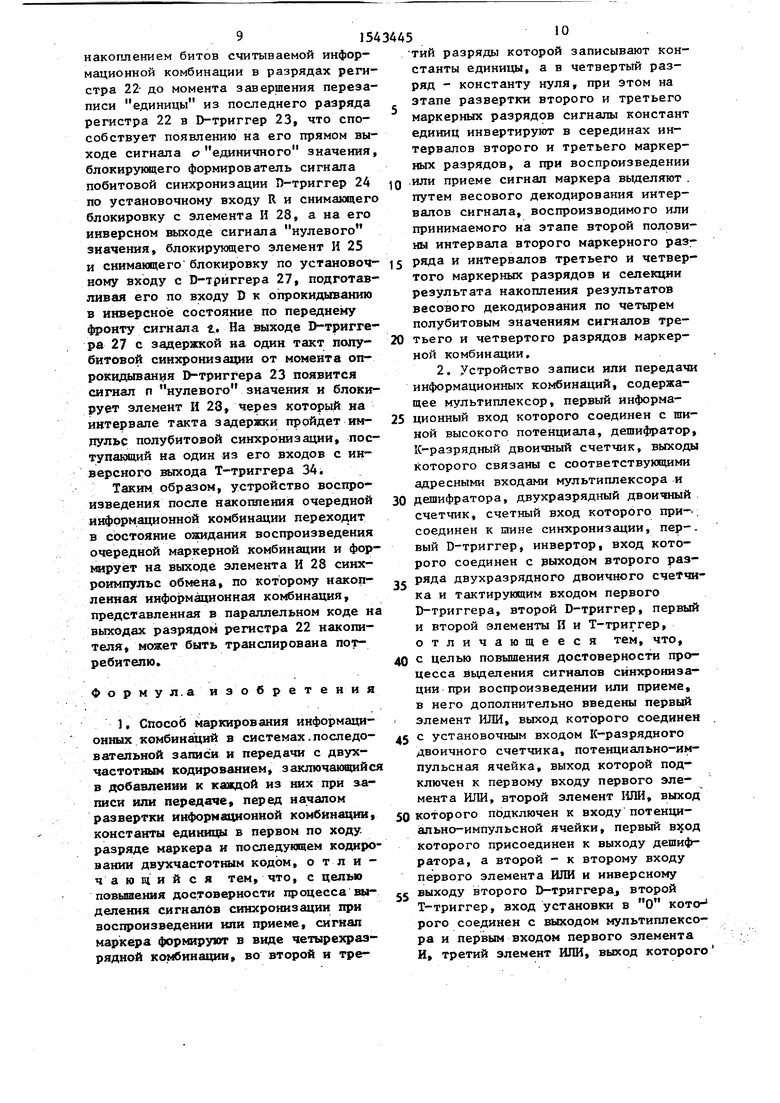

На фиг. 1 приведена функциональная схема устройства записи двухчас- тотно кодированных N-разрядных ин- ,

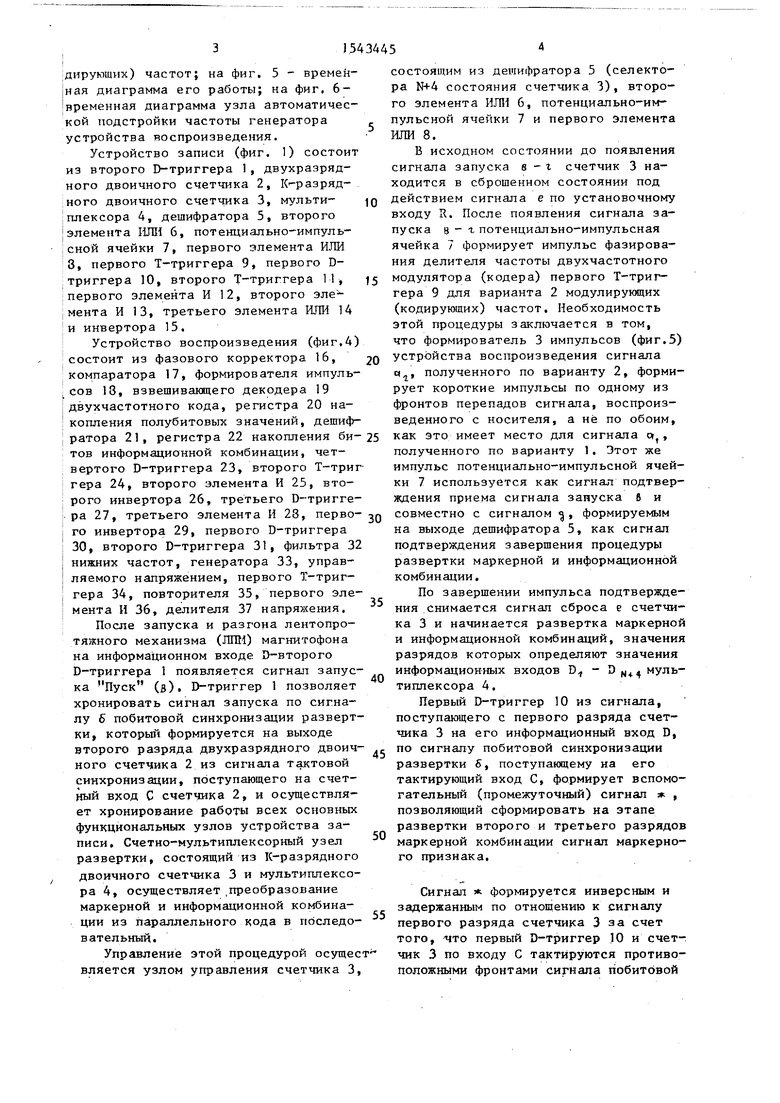

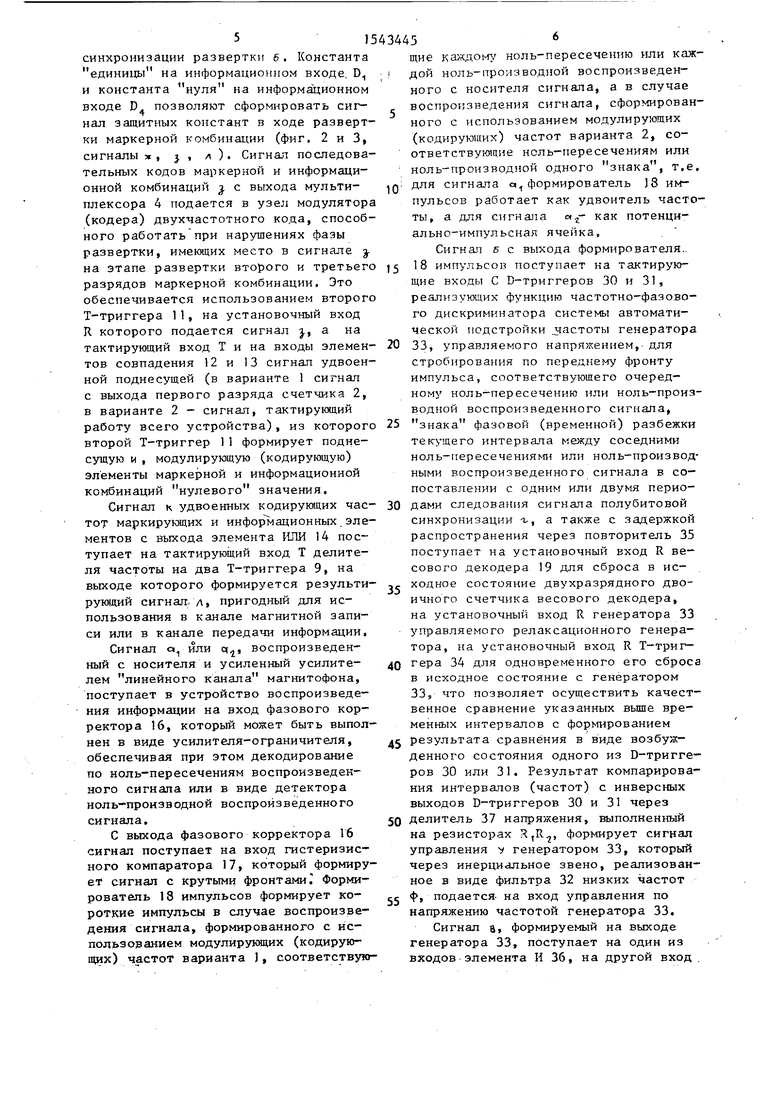

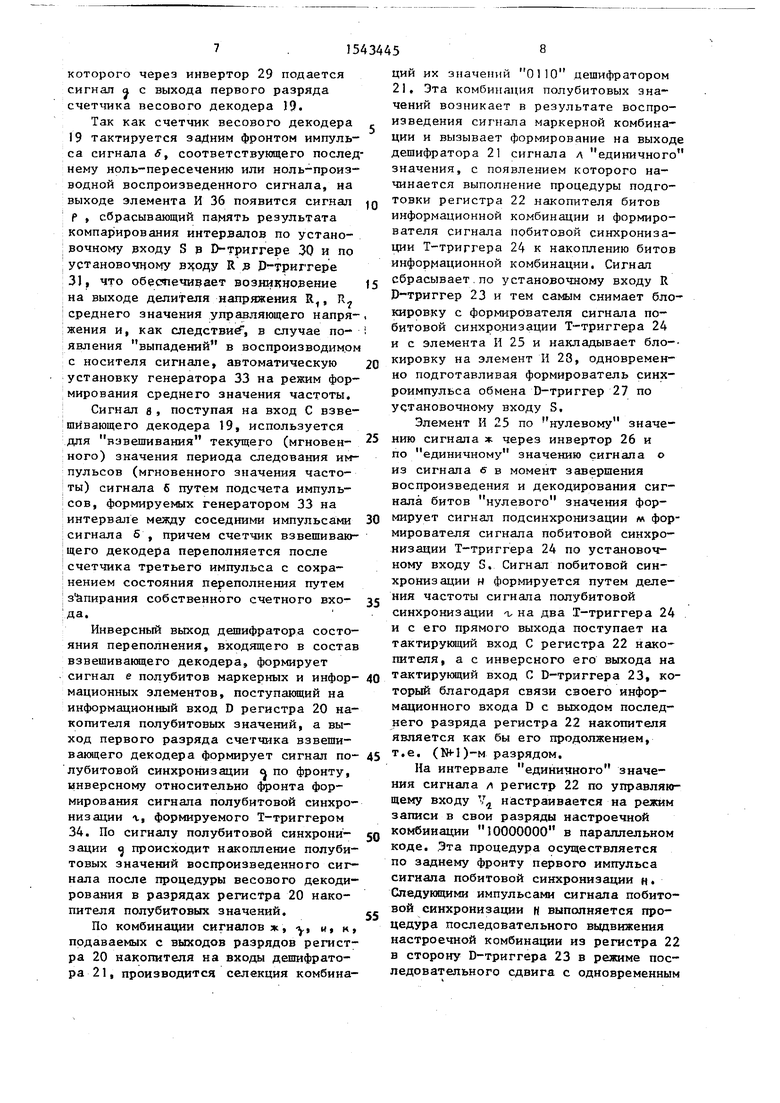

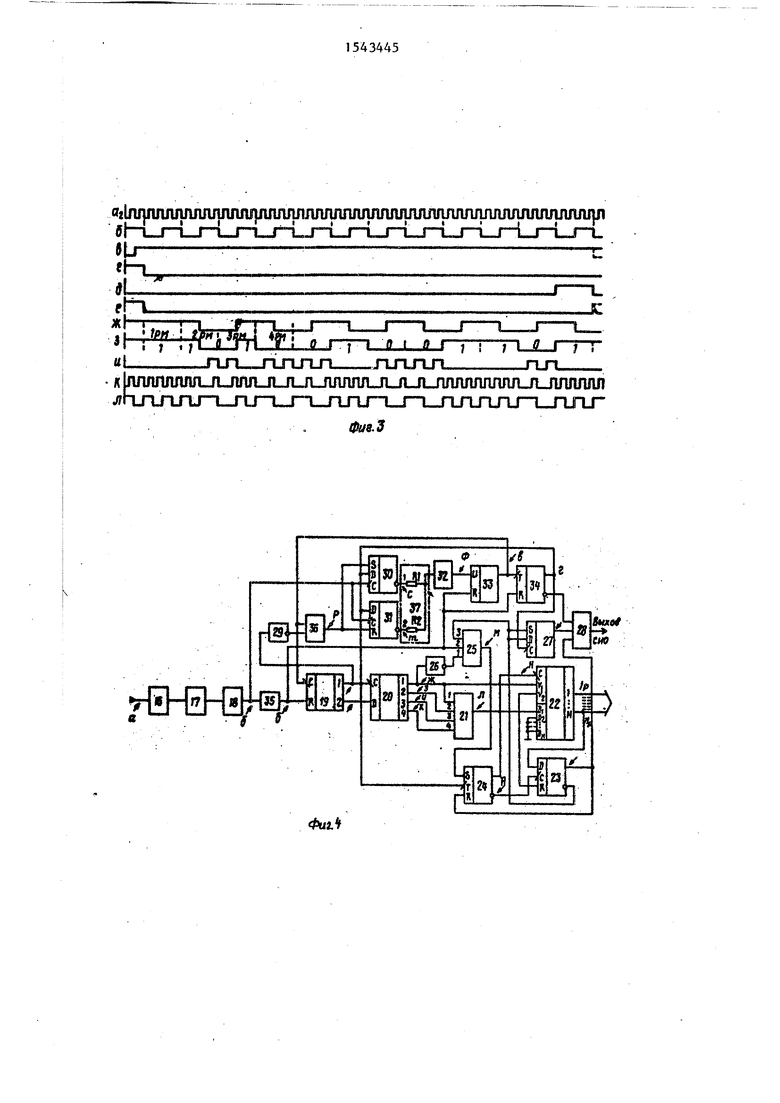

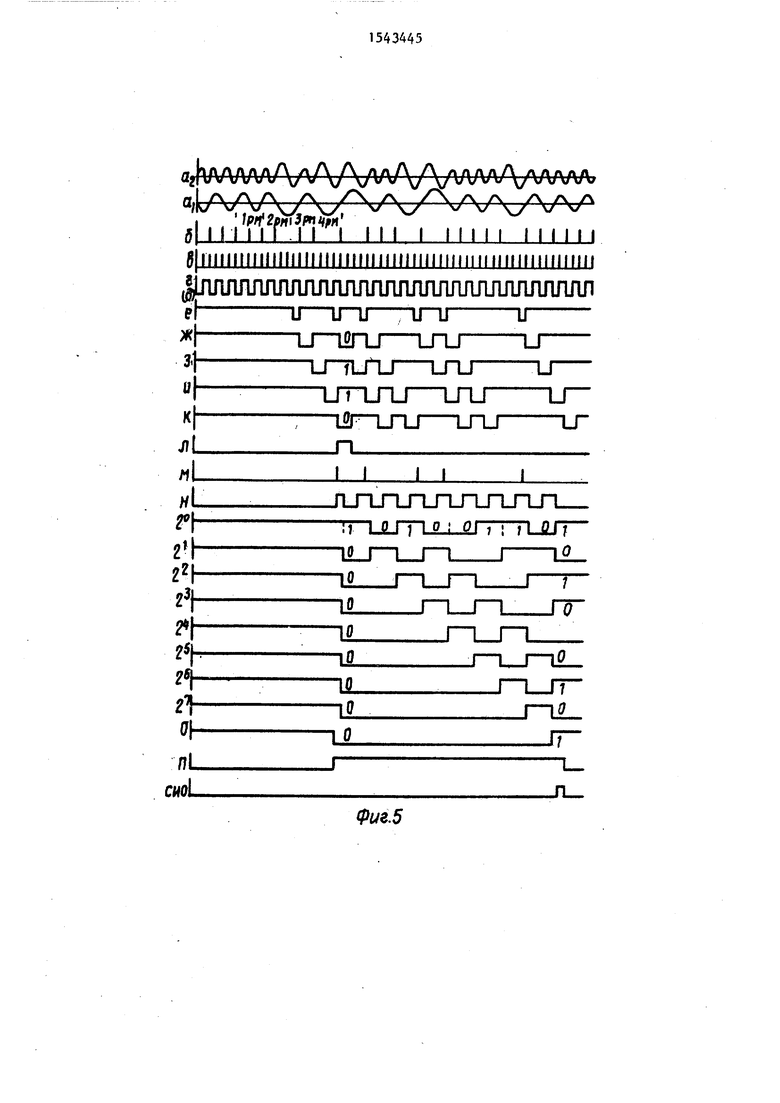

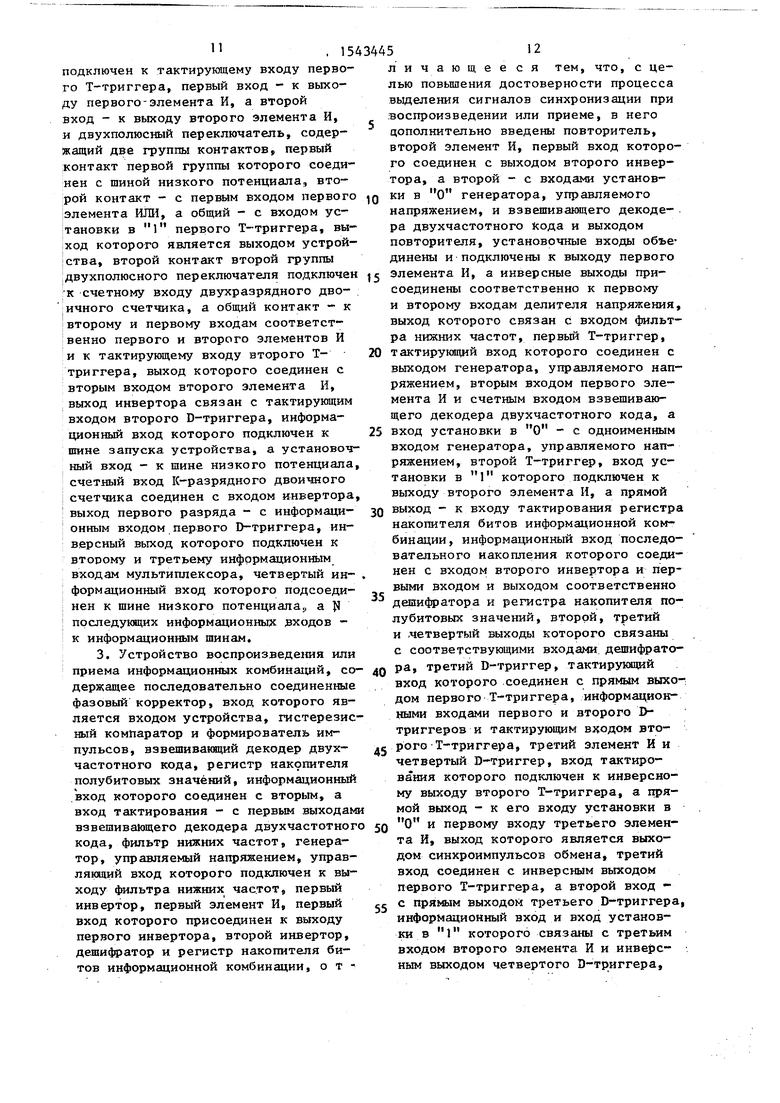

формационных комбинаций, реализующего способ маркирования информационных комбинаций для двух вариантов модулирующих (кодирующих) маркерные и информационные элементы частот; на фиг. 2 - рременная диаграмма работы устройства записи для кодирующих частот варианта If на фиг. 3 - то же, для кодирующих частот варианта 2; на фиг. 4 - функциональная схема устройства воспроизведения, реализующего декодирование сигнала по способу маркирования информационных комбинаций для двух вариантов модулирующих (косл

4ь 00 Јь Ј СЛ

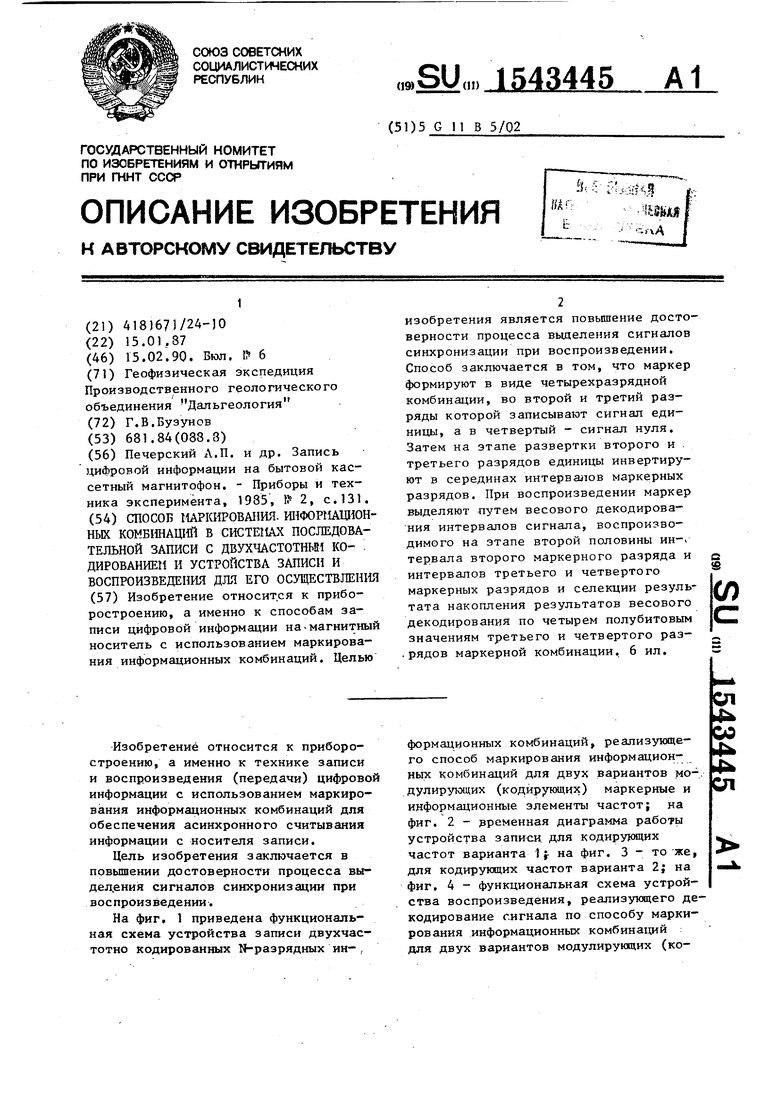

дирующих) частот; на фиг. 5 - времен- ная диаграмма его работы; на фиг. 6- временная диаграмма узла автоматической подстройки частоты генератора устройства воспроизведения.

Устройство записи (фиг. 1) состоит из второго D-триггера , двухразрядного двоичного счетчика 2, Ю-разряд- ного двоичного счетчика 3, мультиплексора 4, дешифратора 5, второго

элемента ИЛИ 6, потенциально-импульсной ячейки 7, первого элемента ИЛИ 3, первого Т-триггера 9, первого D- триггера 10, второго Т-триггера 11, первого элемента И 12, второго мента И 13, третьего элемента ИЛИ 14 и инвертора 15.

Устройство воспроизведения (фиг.4) состоит из фазового корректора 16, компаратора 17, формирователя импульtсов 13, взвешивающего декодера 19 двухчастотного кода, регистра 20 накопления полубитовых значений, дешиф

10

20 3445

состоящим из дешифратора 5 (селектора N+4 состояния счетчика 3), второго элемента ИЛИ 6, потенциально-импульсной ячейки 7 и первого элемента ИЛИ 8.

В исходном состоянии до появления сигнала запуска s - г счетчик 3 находится в сброшенном состоянии под действием сигнала е по установочному входу U. После появления сигнала запуска в - г потенциально-импульсная ячейка 7 формирует импульс фазирования делителя частоты двухчастотного модулятора (кодера) первого Т-триггера 9 для варианта 2 модулирующих (кодирующих) частот. Необходимость этой процедуры заключается в том, что формирователь 3 импульсов (фиг.5) устройства воспроизведения сигнала с«1, полученного по варианту 2, формирует короткие импульсы по одному из фронтов перепадов сигнала, воспроизведенного с носителя, а не по обоим,

15

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ последовательной записи или передачи с двухчастотным кодированием и устройство для его осуществления | 1989 |

|

SU1645993A1 |

| Устройство диагностического контроля аппаратуры цифровой магнитной записи | 1987 |

|

SU1478253A1 |

| Устройство цикловой синхронизации воспроизведения цифровой информации с носителя магнитной записи | 1989 |

|

SU1599895A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Устройство для контроля аппарата магнитной записи | 1988 |

|

SU1607012A1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| Способ последовательной записи или передачи с двухчастотным кодированием и устройство для его осуществления | 1990 |

|

SU1746401A2 |

| Некогерентный приемник | 1988 |

|

SU1525933A1 |

| Микропрограммное устройство формирования тестовой последовательности | 1984 |

|

SU1267425A1 |

| Устройство воспроизведения или приема информационных комбинаций | 1990 |

|

SU1746402A2 |

Изобретение относится к приборостроению, а именно к способам записи цифровой информации на магнитный носитель с использованием маркирования информационных комбинаций. Целью изобретения является повышение достоверности процесса выделения сигналов синхронизации при воспроизведении. Способ заключается в том, что маркер формируют в виде четырехразрядной комбинации, во второй и третий разряды которой записывают сигнал единицы, а в четвертый - сигнал нуля. Затем на этапе развертки второго и третьего разрядов единицы инвертируют в серединах интервалов маркерных разрядов. При воспроизведении маркер выделяют путем весового декодирования интервалов сигнала, воспроизводимого на этапе второй половины интервала второго маркерного разряда и интервалов третьего и четвертого маркерных разрядов, и селекции результата накопления результатов весового декодирования по четырем полубитовым значениям третьего и четвертого разрядов маркерной комбинации. 6 ил.

ратора 21, регистра 22 накопления би- 25 как это имеет место для сигнала от

Этот же

тов информационной комбинации, четвертого D-триггера 23, второго Т-триг гера 24, второго элемента И 25, второго инвертора 26, третьего D-триггера 27, третьего элемента И 28, перво- д совместно с сигналом , формируемым го инвертора 29, первого D-триггерана выходе дешифратора 5, как сигнал

полученного по варианту 1, импульс потенциально-импульсной ячей ки 7 используется как сигнал подтвер ждения приема сигнала запуска 8 и

30, второго D-триггера 31, фильтра 32 нижних частот, генератора 33, управляемого напряжением, первого Т-триг- гера 34, повторителя 35, первого элемента И 36, делителя 37 напряжения.

После запуска и разгона лентопротяжного механизма (ЛПМ) магнитофона на информационном входе D-второго D-триггера 1 появляется сигнал запуска Пуск (в). D-триггер 1 позволяет хронировать сигнал запуска по сигналу 6 побитовой синхронизации развертки, который формируется на выходе

второго разряда двухразрядного двоич- ., по сигналу побитовой синхронизации

ного счетчика 2 из сигнала тактовой синхронизации, поступающего на счетный вход С счетчика 2, и осуществляет хронирование работы всех основных функциональных узлов устройства записи. Счетно-мультиплексорный узел развертки, состоящий из К-разрядного двоичного счетчика 3 и мультиплексора 4, осуществляет ,преобразование маркерной и информационной комбинации из параллельного кода в последовательный.

Управление этой процедурой осущест вляется узлом управления счетчика 3,

50

55

развертки 5, поступающему на его тактирующий вход С, формирует вспо гательный (промежуточный) сигнал позволяющий сформировать на этапе развертки второго и третьего разряд маркерной комбинации сигнал маркер го признака.

Сигнал формируется инверсным и задержанным по отношению к сигналу первого разряда счетчика 3 за счет того, что первый D-триггер 10 и сче чик 3 по входу С тактируются против положными фронтами сигнала побитово

как это имеет место для сигнала от

Этот же

совместно с сигналом , формируемым на выходе дешифратора 5, как сигнал

полученного по варианту 1, импульс потенциально-импульсной ячейки 7 используется как сигнал подтверждения приема сигнала запуска 8 и

5

0

подтверждения завершения процедуры развертки маркерной и информационной комбинации.

По завершении импульса подтверждения снимается сигнал сброса е счетчика 3 и начинается развертка маркерной и информационной комбинаций, значения разрядов которых определяют значения информационных входов В., - D N4 мультиплексора 4.

Первый D-триггер 10 из сигнала, поступающего с первого разряда счетчика 3 на его информационный вход D,

0

5

развертки 5, поступающему на его тактирующий вход С, формирует вспомогательный (промежуточный) сигнал , позволяющий сформировать на этапе развертки второго и третьего разрядов маркерной комбинации сигнал маркерного признака.

Сигнал формируется инверсным и задержанным по отношению к сигналу первого разряда счетчика 3 за счет того, что первый D-триггер 10 и счетчик 3 по входу С тактируются противоположными фронтами сигнала побитовой

синхронизации развертки 6, Константа единицы на информационном входе D, и константа нуля на информационном входе D4 позволяют сформировать сигнал защитных констант в ходе развертки маркерной комбинации (фиг, 2 и 3, сигналы ж , j , л ). Сигнал последовательных кодов маркерной и информационной комбинаций с выхода мульти- плексора 4 подается в узел модулятора (кодера) двухчастотного кода, способного работать при нарушениях фазы развертки, имеющих место в сигнале на этапе развертки второго и третьего разрядов маркерной комбинации. Это обеспечивается использованием второго Т-триггера 11, на установочный вход R которого подается сигнал |, а на тактирующий вход Т и на входы элемен- тов совпадения 12 и 13 сигнал удвоенной поднесущей (в варианте 1 сигнал с выхода первого разряда счетчика 2, в варианте 2 - сигнал, тактирующий работу всего устройства), из которого второй Т-триггер 11 формирует подне- сущую и, модулирующую (кодирующую) элементы маркерной и информационной комбинаций нулевого значения.

Сигнал к удвоенных кодирующих частот маркирующих и информационных элементов с выхода элемента ИЛИ 14 поступает на тактирующий вход Т делителя частоты на два Т-триггера 9, на выходе которого формируется результирующий сигнал л пригодный для использования в канале магнитной записи или в канале передачи информации.

Сигнал QI или cf4, воспроизведенный с носителя и усиленный усилите

лем линейного канала магнитофона, поступает в устройство воспроизведения информации на вход фазового корректора 16, который может быть выполнен в виде усилителя-ограничителя, обеспечивая при этом декодирование по ноль-пересечениям воспроизведенного сигнала или в виде детектора ноль-производной воспроизведенного сигнала,

С выхода фазового корректора 16 сигнал поступает на вход гистеризис- ного компаратора 17, который формирует сигнал с крутыми фронтами Формирователь 18 импульсов формирует короткие импульсы в случае воспроизведения сигнала, формированного с использованием модулирующих (кодирующих) частот варианта J, соответствующие каждому ноль-пересечению или каждой ноль-производной воспроизведенного с носителя сигнала, а в случае воспроизведения сигнала, сформированного с использованием модулирующих (кодирующих) частот варианта 2, соответствующие ноль-пересечениям или ноль-производной одного знака, т.е. для сигнала а, формирователь 18 импульсов работает как удвоитель частоты, а для сигнала «t- как потенциально-импульсная ячейка,

Сигнал Б с выхода формирователя 18 импульсов поступает на тактирующие входы С D-триггеров 30 и 31, реализующих функцию частотно-фазового дискриминатора системы автоматической подстройки .частоты генератора 33, управляемого напряжением, для стробирования по переднему фронту импульса, соответствующего очередному ноль-пересечению или ноль-производной воспроизведенного сигнала, знака фазовой (временной) разбежки

текущего интервала между соседними ноль-пересечениями или ноль-производными воспроизведенного сигнала в сопоставлении с одним или двумя периодами следования сигнала полубитовой синхронизации -и, а также с задержкой распространения через повторитель 35 поступает на установочный вход R весового декодера 19 для сброса в исходное состояние двухразряцного двоичного счетчика весового декодера, на установочный вход R генератора 33 управляемого релаксационного генератора, на установочный вход R Т-триггера 34 для одновременного его сброса в исходное состояние с генератором 33s что позволяет осуществить качественное сравнение указанных выше временных интервалов с формированием

результата сравнения в виде возбужденного состояния одного из D-тригге- ров 30 или 31. Результат компарирова- ния интервалов (частот) с инверсных выходов D-трнггеров 30 и 31 через

делитель 37 напряжения, выполненный на резисторах ,R, формирует сигнал управления v генератором 33, который через инерциальное звено, реализованное в виде фильтра 32 низких частот

Ф, подается на вход управления по напряжению частотой генератора 33. Сигнал в, формируемый на выходе генератора 33, поступает на один из входов элемента И 36, на другой вход

которого через инвертор 29 подается сигнал а с выхода первого разряда

счетчика весового декодера 19.

Так как счетчик весового декодера , 19 тактируется задним фронтом импульса сигнала б, соответствующего последнему ноль-пересечению или ноль-производной воспроизведенного сигнала, на выходе элемента И 36 появится сигнал JQ р , сбрасывающий память результата компарирования интервалов по установочному входу S в D-триггере 30 и по установочному входу R в Р-триггере 31, что обеспечивает возникновение 15 на выходе делителя напряжения R1, R7 среднего значения управляющего напря-, жения и, как следствие , в случае по- i явления выпадений в воспроизводимом с носителя сигнале, автоматическую 20 установку генератора 33 на режим формирования среднего значения частоты.

Сигнал в поступая на вход С взвешивающего декодера 19, используется для взвешивания текущего (мгновен- 5 ного) значения периода следования импульсов (мгновенного значения частоты) сигнала б путем подсчета импульсов, формируемых генератором 33 на интервале между соседними импульсами

ций их значений 0110 дешифратором 21, Эта комбинация полубитовых значений возникает в результате воспроизведения сигнала маркерной комбинации и вызывает формирование на выходе

дешифратора 21 сигнала л единичного значения, с появлением которого начинается выполнение процедуры подготовки регистра 22 накопителя битов информационной комбинации и формирователя сигнала побитовой синхронизации Т-триггера 24 к накоплению битов информационной комбинации. Сигнал сбрасывает по установочному входу R Р-триггер 23 и тем самым снимает блокировку с формирователя сигнала побитовой синхронизации Т-триггера 24 и с элемента И 25 и накладывает бло- кировку на элемент И 23, одновременно подготавливая формирователь синхроимпульса обмена D-триггер 27 по установочному входу S,

Элемент И 25 по нулевому значению сигнала через инвертор 26 и по единичному значению сигнала о из сигнала б в момент завершения воспроизведения и декодирования сигнала битов нулевого значения фор30

сигнала б , причем счетчик взвешивающего декодера переполняется после счетчика третьего импульса с сохранением состояния переполнения путем з апирания собственного счетного входа.

Инверсный выход дешифратора состояния переполнения, входящего в состав взвешивающего декодера формирует

35

мирует сигнал подсинхронизации м формирователя сигнала побитовой синхронизации Т-триггера 24 по установочному входу 5. Сигнал побитовой синхронизации н формируется путем деления частоты сигнала полубитовой синхронизации ч- на два Т-триггера 24 и с его прямого выхода поступает на тактирующий вход С регистра 22 накопителя, а с инверсного его выхода на

сигнал е полубитов маркерных и инфор- 40 тактирующий вход С D-триггера 23, ко- мационных элементов, поступающий наторый благодаря связи своего инфоринформационный вход D регистра 20 накопителя полубитовых значений, а выход первого разряда счетчика взвешивающего декодера формирует сигнал по- 45 (и+-1)-м разрядом, лубитовой синхронизации j по фронту, интервале

инверсному относительно фронта формирования сигнала полубитовой синхронизации г, формируемого Т-триггером 34. По сигналу полубитовой синхрони- 50 зации j происходит накопление полубитовых значений воспроизведенного сигнала после процедуры весового декодирования в разрядах регистра 20 накопителя полубитовых значений.55

По комбинации сигналов ж, -у, и, к, подаваемых с выходов разрядов регистра 20 накопителя на входы дешифратора 2 1 , производится селекция комбинамационного входа D с выходом последнего разряда регистра 22 накопителя является как бы его продолжением,

ядом.

единичного значения сигнала / регистр 22 по управляющему входу V4 настраивается на режим записи в свои разряды настроечной комбинации 10000000 в параллельном коде. Эта процедура осуществляется по заднему фронту первого импульса сигнала побитовой синхронизации н« Следующими импульсами сигнала побитовой синхронизации ц выполняется процедура последовательного выдвижения настроечной комбинации из регистра 22 в сторону D-триггера 23 в режиме последовательного сдвига с одновременным

, Q 5 20

34458

ций их значений 0110 дешифратором 21, Эта комбинация полубитовых значений возникает в результате воспроизведения сигнала маркерной комбинации и вызывает формирование на выходе

дешифратора 21 сигнала л единичного значения, с появлением которого начинается выполнение процедуры подготовки регистра 22 накопителя битов информационной комбинации и формирователя сигнала побитовой синхронизации Т-триггера 24 к накоплению битов информационной комбинации. Сигнал сбрасывает по установочному входу R Р-триггер 23 и тем самым снимает блокировку с формирователя сигнала побитовой синхронизации Т-триггера 24 и с элемента И 25 и накладывает блокировку на элемент И 23, одновременно подготавливая формирователь синхроимпульса обмена D-триггер 27 по установочному входу S,

Элемент И 25 по нулевому значению сигнала через инвертор 26 и по единичному значению сигнала о из сигнала б в момент завершения воспроизведения и декодирования сигнала битов нулевого значения фор тактирующий вход С D-триггера 23, ко- торый благодаря связи своего инфор (и+-1)-м разрядом, а интервале

мационного входа D с выходом последнего разряда регистра 22 накопителя является как бы его продолжением,

ядом.

единичного значения сигнала / регистр 22 по управляющему входу V4 настраивается на режим записи в свои разряды настроечной комбинации 10000000 в параллельном коде. Эта процедура осуществляется по заднему фронту первого импульса сигнала побитовой синхронизации н« Следующими импульсами сигнала побитовой синхронизации ц выполняется процедура последовательного выдвижения настроечной комбинации из регистра 22 в сторону D-триггера 23 в режиме последовательного сдвига с одновременным

накоплением битов считываемой информационной комбинации в разрядах регистра 22- до момента завершения перезаписи единицы из последнего разряда регистра 22 в D-триггер 23, что способствует появлению на его прямом выходе сигнала о единичного значения, блокирующего формирователь сигнала побитовой синхронизации D-триггер 24 по установочному входу R и снимающего блокировку с элемента И 28, а на его инверсном выходе сигнала нулевого значения, блокирующего элемент И 25 и снимающего блокировку по установоч- ному входу с D-триггера 27, подготавливая его по входу D к опрокидыванию в инверсное состояние по переднему фронту сигнала 1. На выходе D-триггера 27 с задержкой на один такт полубитовой синхронизации от момента опрокидывания D-триггера 23 появится сигнал п нулевого значения и блокирует элемент И 23, через который на интервале такта задержки пройдет импульс полубитовой синхронизации, поступающий на один из его входов с инверсного выхода Т-триггера 34.

Таким образом, устройство воспроизведения после накопления очередной информационной комбинации переходит в состояние ожидания воспроизведения очередной маркерной комбинации и формирует на выходе элемента И 28 синхроимпульс обмена, по которому накопленная информационная комбинация, представленная в параллельном коде на выходах разрядом регистра 22 накопителя, может быть транслирована потребителю.

Формула изобретения

0

s

тий разряды которой записывают константы единицы, а в четвертый разряд - константу нуля, при этом на этапе развертки второго и третьего маркерных разрядов сигналы констант единиц инвертируют в серединах интервалов второго и третьего маркерных разрядов, а при воспроизведении или приеме сигнал маркера выделяют . путем весового декодирования интервалов сигнала, воспроизводимого или принимаемого на этапе второй половины интервала второго маркерного разряда и интервалов третьего и четвертого маркерных разрядов и селекции результата накопления результатов весового декодирования по четырем полубитовым значениям сигналов третьего и четвертого разрядов маркерной комбинации.

0 дешифратора, двухразрядный двоичный счетчик, счетный вход которого при-. соединен к шине синхронизации, пер-, вый D-триггер, инвертор, вход которого соединен с выходом второго раз, ряда двухразрядного двоичного счетчи- ка и тактирующим входом первого D-триггера, второй D-триггер, первый и второй элементы И и Т-триггер отличающееся тем, что, с целью повышения достоверности процесса выделения сигналов синхронизации при воспроизведении или приеме, в него дополнительно введены первый элемент ИЛИ, выход которого соединен с установочным входом К-разрядного двоичного счетчика, потенциально-импульсная ячейка, выход которой подключен к первому входу первого элемента ИЛИ, второй элемент ИЛИ, выход

0 которого подключен к входу потенциально-импульсной ячейки, первый вход которого присоединен к выходу дешифратора, а второй - к второму входу первого элемента ИЛИ и инверсному

5 выходу второго 0-триггераэ второй Т-триггер, вход установки в О кото-1 рого соединен с выходом мультиплексора и первым входом первого элемента И, третий элемент ИЛИ, выход которого

0

5

11

1543445

подключен к тактирующему входу первого Т-триггера, первый вход - к выходу первого-элемента И, а второй вход - к выходу второго элемента И, и двухполюсный переключатель, содержащий две группы контактов, первый контакт первой группы которого соединен с шиной низкого потенциала, второй контакт - с первым входом первого элемента ИЛИ, а общий - с входом установки в 1 первого Т-триггера, выход которого является выходом устройства, второй контакт второй группы двухполюсного переключателя подключен к счетному входу двухразрядного двоичного счетчика, а общий контакт - к второму и первому входам соответственно первого и второго элементов И и к тактирующему входу второго Т-триггера, выход которого соединен с вторым входом второго элемента И, выход инвертора связан с тактирующим входом второго D-триггера, информационный вход которого подключен к шине запуска устройства, а установочный вход - к шине низкого потенциала, счетный вход К-разрядного двоичного счетчика соединен с входом инвертора, выход первого разряда - с информационным входом первого D-триггера, инверсный выход которого подключен к второму и третьему информационным входам мультиплексора, четвертый ин- формационный вход которого подсоединен к шине низкого потенциала,, а $ последующих информационных входов - к информационным шинам.

ичающее

12 с я

тем, что, с це

5

0

5

0

лью повышения достоверности процесса выделения сигналов синхронизации при воспроизведении или приеме, в него дополнительно введены повторитель, второй элемент И, первый вход которого соединен с выходом второго инвертора, а второй - с входами установки в О генератора, управляемого напряжением, и взвешивающего декодера двухчастотного Кода и выходом повторителя, установочные входы объединены и подключены к выходу первого элемента И, а инверсные выходы присоединены соответственно к первому и второму входам делителя напряжения, выход которого связан с входом фильтра нижних частот, первый Т-триггер, тактирующий вход которого соединен с выходом генератора, управляемого напряжением, вторым входом первого элемента И и счетным входом взвешивающего декодера двухчастотного кода, а вход установки в О - с одноименным входом генератора, управляемого напряжением, второй Т-триггер, вход установки в 1 которого подключен к выходу второго элемента И, а прямой выход - к входу тактирования регистра накопителя битов информационной комбинации, информационный вход последовательного накопления которого соединен с входом второго инвертора и первыми входом и выходом соответственно дешифратора и регистра накопителя полубитовых значений, второй, третий и четвертый выходы которого связаны с соответствующими входами дешифратол ра, третий D-триггер, тактирующий вход которого соединен с прямым выходом первого Т-триггера, информационными входами первого и второго D- триггеров и тактирующим входом втос рого Т-триггера, третий элемент И и четвертый D-триггер, вход тактирования которого подключен к инверсному выходу второго Т-триггера, а прямой выход - к его входу установки в О и первому входу третьего элемента И, выход которого является выходом синхроимпульсов обмена, третий вход соединен с инверсным выходом первого Т-триггера, а второй вход - с прямым выходом третьего D-триггера, информационный вход и вход установки в 1 которого связаны с третьим входом второго элемента И и инверсным выходом четвертого D-триггера,

5

0

5

131543445I

вход установки в . 0 которого присое- параллельного накопителя которого динен к выходу дешифратора и входу соединен с шиной низкого потенциала, установки режима работы и информационному входу параллельного накопления первого разряда регистра накопителя битов информационной комбинации,

остальные N-1 информационные входы

выходы являются выходом устройства, причем выход старшего разряда также подключен к информационному входу четвертого D-триггера.

а 11шшишпллш1ши1лллл тгшшшллллл

-I I I I I I I I I I I I I I

6 h-riJTjnjTj jTj4jTjnjn r

0 г

01

U

Г-г |

II1

ЗЬ fi Г о ГП о i о 1 т

к Innnnmjuiji-jimLJiJ

л|

Фк/&2

параллельного накопителя которого соединен с шиной низкого потенциала,

выходы являются выходом устройства, причем выход старшего разряда также подключен к информационному входу четвертого D-триггера.

Л 72

Л

ГЦ

г

/т

лт

11

Выход

фие.1

;

г

а11Ш}П1ШПЛПЛЛЛПЛ1}Л1ШЛ

ж|-т

l uulлnлл uLЛJlnлJlJUЛJШЛJ ЛJa j hjTJTJbTT rira T-JTJTj-n

Фаа.З

8tuet

ПП П П П in

fl

runru U-njlЈ

ПЛГШП|ж

Пп п п п

ШЛЛПЛЛ1Ж1ППЛШ

llllll lllllllllllllllllllllllllllll lll|||||l||l|IIIJIIIHl|g

MINI Mill I I I I (J I И I I Q

/У А. /. /У / /. /. / А X /N7n / / / / / у / 7 / / / и

П

JL

Фиг. 6

| Печерский Л.П | |||

| и др | |||

| Запись цифровой информации на бытовой кассетный магнитофон | |||

| - Приборы и техника эксперимента, 1985, № 2, с.131. |

Авторы

Даты

1990-02-15—Публикация

1987-01-15—Подача