СП

со оо

CD СП

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство диагностического контроля аппаратуры цифровой магнитной записи | 1987 |

|

SU1478253A1 |

| Устройство для контроля ошибок канала цифровой магнитной записи | 1988 |

|

SU1510007A1 |

| Устройство для контроля ошибок воспроизведения информации с носителя магнитной записи | 1989 |

|

SU1619339A1 |

| Устройство для воспроизведения информации с магнитного носителя | 1981 |

|

SU1014017A1 |

| Устройство для контроля ошибок магнитной записи-воспроизведения цифровой информации | 1985 |

|

SU1273994A1 |

| Устройство для воспроизведения сигналов цифровой информации с носителя магнитной записи | 1983 |

|

SU1065875A1 |

| Устройство для контроля ошибок аппаратуры многоканальной магнитной записи | 1988 |

|

SU1580438A1 |

| Устройство для магнитной записи цифровой информации | 1982 |

|

SU1037337A1 |

| Устройство для контроля синхронизма воспроизведенных сигналов | 1988 |

|

SU1585833A1 |

| Устройство магнитной записи и воспроизведения двухчастотных сигналов | 1983 |

|

SU1129648A1 |

Изобретение может быть использовано при воспроизведении блочно-кодированной информации, например, в системе помехоустойчивого кодирования многоканальной аппаратуры магнитной записи. Устройство содержит входную информационную шину 1, шину 2 тактовой синхронизации, элемент 3 задержки, регистр 4 сдвига, дешифратор 5 маркера, триггер 6, элемент И 7, элемент ИЛИ 8, выходную шину 9 сигнала цикловой синхронизации, выходную информационную шину 10, счетчики 11, 12 и триггеры 13, 14, 15. Цель изобретения - уменьшение цикловой синхронизации достигается в результате исключения ложных сигналов маркера и восстановления импульсов цикловой синхронизации при выпадении воспроизводимых сигналов маркера. 2 ил.

/ о

Ф.иг.1

Изобретение относится к приборостроению, а именно к технике магнитной записи, и может быть использовано в системе помехоустойчивого кодирования многоканальной аппаратуры цифровой магнитной записи.

Цель изобретения - уменьшение погрешности цикловой синхронизации воспроизведения цифровой информации.

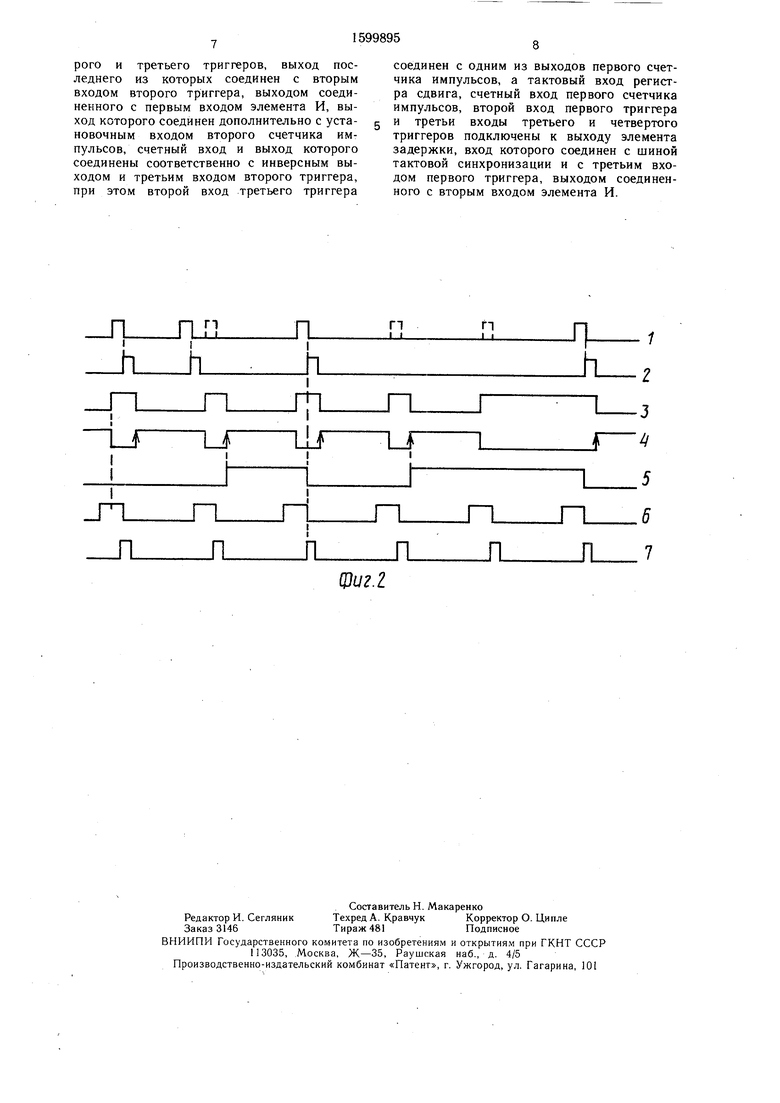

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - временные диаграммы, иллюстрирующие принцип его действия.

Устройство для цикловой синхронизации воспроизведения блочно-кодированной цифровой информации с носителя магнитной записи - магнитной ленты содержит входную шину 1 воспроизводимой цифровой информации, входную шину 2 тактового синхросигнала воспроизведения, элемент 3 задержки, регистр 4 сдвига, дешифратор 5 маркера, первый триггер б, элемент И 7, элемент ИЛИ 8, выходную шину 9 сигнала цикловой синхронизации, выходную шину 10 воспроизводимой цифровой информации, первый 11 и второй 12 счетчики импульсов и второй 13, третий 14 и четвертый 15 триггеры.

Информационная шина 1 соединена с информационным входом регистра 4 сдвига, выходы разрядов которого соединены с входами дешифратора 5 маркера, выход которого соединен с первым, информационным входом Д триггера б, выход которого соединен с вторым входом элемента И 7, выход которого соединен с первым входом элемента ИЛИ 8, выход которого соединен с выходной шиной 9 сигнала цикловой синхронизации и с установочным в нулевое состояние входом двоичного счетчика 11 импульсов. Выход первого разряда регистра 4 сдвига соединен дополнительно с выходной информационной шиной 10.

Шина 2 тактовой синхронизации соединена с третьим, инверсным установочным в нулевое состояние входом т))иггера бис входом элемента 3 задержки, выход которого соединен с тактовым входом регистра 4 сдвига, с вторым, тактирующим входом С триггера б, со счетным входом счетчика 11 импульсов, с третьим, инверсным установочным в нулевое состояние входом триггера 15 и с третьим, инверсным установочным в нулевое состояние входом триггера 14, выход которого соединен с вторым, установочным в единичное состояние входом триггера. 13.

Выход пятого разряда счетчика 11 импульсов соединен с первым, тактирующим входом С триггера 14 и с первым, тактирующим входом С триггера 13, инверсный выход которого соединен со счетным входом двоичного счетчика 12 импульсов, выход второго разряда которого соединен с первым, информационным входом Д триг

гера 13, прямой выход которого соединен с первым входом элемента И 7.

Выход шестого разряда счетчика 11 импульсов соединен с вторым, тактирующим 5 входом С триггера 15. Выход девятого разряда счетчика 11 импульсов соединен с вторым, информационным входом Д триггера 14 и с третьим, информационным входом Д триггера 15, выход которого соединен с вторым входом элемента

ИЛИ 8. Выход элемента И 7 соединен

дополнительно с установочным в нулевое

состояние входом счетчика 12 импульсов.

Устройство работает следующим образом.

Подаваемая на щину 1 воспроизводи5 мая цифр.овая информация по структуре состоит из последовательности кадров, каждый из которых содержит, в частности, 256-ти битовый информационный блок, 16-ти разрядный контрольный остаток кода циклического контроля и 16-ти разрядную мар0 керную комбинацию.

С помощью тактового синхросигнала, поступающего по щине 2, продвигается информация в регистре 4 и устанавливаются в нулевое состояние триггеры б, 14, 15.

5 Тактовые импульсы подсчитывает счетчик 11. Каждый раз, при введении в регистр 4 маркерной комбинации воспроизводимого сигнала на выходе дешифратора 5 диаграмма 1, фиг. 2) формируется сигнал - импульс маркера. Этот сигнал записывает0 ся фронтом следующего тактового импульса, в триггер б, который сбрасывается в исходное нулевое состояние через полтакта отрицательной полуволной синхросигнала. В результате на выходе триггера б (диаграмма 2, фиг. 2). Формирует5 ся длительностью в полтакта положительный импульс маркера, который происходит через элемент И 7, элемент ИЛИ 8 и поступает на выходную шину сигнала цикловой синхронизации, осуществляемой, таким образом, импульсами маркера.

Погрешность цикловой синхронизации воспроизведения цифровой информации, осуществляемой с помощью маркеров, записываемых на магнитный носитель на границах кадров (информационных блоков),

5 определяется тремя особенностями такого способа синхронизации: при сбое воспроизведения маркерной комбинации импульс цикловой синхронизации сформирован не будет; при соответствующих сбоях в информационном блоке кадра может быть сфор0 мирован ложный импульс маркера кадра в отличном от истинного местоположении (второй импульс на диаграмме 2, фиг. 2); ложный импульс маркера может быть сформирован также при появлении в информационном блоке кадра комбинации информационных бит, совпадающей с маркерной. Для защиты от ложных сигналов (второй импульс на диаграмме 1, фиг. 2) маркера в устройстве элемент И 7 открывается для прохождения выходного сигнала триггера 6 только в области ожидаемого появления импульса маркера. Открывается элемент И 1 выходным сигналом триггера 13, показанным по диаграмме 3, фиг. 2.

Протяженность временных «ворот (временного «окна) ожидаемого прохождения воспроизведенного сигнала маркера в предлагаемом устройстве равна, в частности, ±16 тактов.

Для защиты от выпадения сигналов маркеров (показаны пунктиром на второй половине диаграммы 1, фиг. 2) в устройстве производится непрерывное формирование сигнала замещения импульсов маркеров, который с выхода триггера 15 (диаграмма 7, фиг. 2) поступает на выходную шину 9 через элемент ИЛИ 8.

С выходного элемента ИЛИ 8 вое- произведенный импульс маркера устанавливает в нулевое состояние счетчик 11. А счетчик 12 устанавливается в нулевое состояние выходным воспроизведенным импульсом маркера элемента И 7. Через 256 тактов после этого, т. е. после окончания информационного блока кадра на информационных входах триггеров 14 и 15 устанавливается высокий уровень напряжения, формируемый на выходе девятого разряда (диаграмму 6, фиг. 2) счетчика 11.

Через 16 тактов после этого триггер 14 переключается в единичное состояние и его сигнал устанавливает в единичное состояние триггер 13, на выходе которого при этом положительные импульсы на диаграмме 3, фиг. 2) формируется сигнал «ворот, открывающий элемент И 7. Сигнал на инверсном выходе триггера 13 показан на диаграмме 4, фиг. 2.

Через 32 такта после появления высокого уровня напряжения на выходе девятого разряда счетчика 11 и соответственно через 16 тактов после начала формирования разрешающего сигнала «ворот на выходе триггера 13, формируется сигнал на выходе триггера 15 (диаграмма 7, фиг. 2), который через пол-такта сбрасывается так- товым синхросигналом в исходное состояние. В результате на выходе триггера 15 формируется длительностью в пол-такта импульс замещения воспроизводимого сигнала маркера. Импульс замещения совпадает по времени с воспроизводимым им- пульсом маркера, когда он поступает с выхода элемента И 7 в положенный момент.

На выходе триггера 14 формируется импульс также длительностью в пол-такта.

Через 16 тактов после формирования импульса замещения триггер 13 устанавливается в нулевое состояние и запирается элемент И 7. Формируемый при этом положительный перепад уровней напряжений на инверсном выходе триггера 13 (диаграмма 4 фиг. 2) подсчитывается счетчиком 12 циклов.

Если следующий, очередной импульс маркера на выходе элемента И 7 сформирован не будет, то триггером 13 будут сформированы разрешающие «ворота для элемента И7; на выходную шину 9 -поступит через элемент ИЛИ 8 импульс замещения сигнала маркера с выхода триггера 15; счетчик 12 подсчитает второй цикл и на его выходе (диаграмма 5, фиг. 2) будет сформирован высокий уровень напряжения.

Если же на выходе элемента И 7 не поступит и следующий, т. е. второй подряд импульс воспроизводимого маркера, то таким же образом на выходную шину 9 поступит импульс замещения воспроизводимого сигнала маркера и будет сформирован разрешающий сигнал, на выходе триггера 13. Но этот сигнал уже не снимается через 32 такта (второй положительный импульс на диаграмме 5, фиг. 2) и элемент И 7 будет постоянно открыт до поступления воспроизводимого сигнала маркера. Снятие «ворот, в частном случае после двухкратного отсутствия воспроизведения маркера, необходимо для ввода устройства в синхронизм как в первоначальный момент его работы, так и в случае крупного сбоя воспроизведения.

Элемент 3 выдерживает момент записи информации в триггер 6 относительно снятия сигнала по его установочному входу.

Фронт импульса цикловой синхронизации на выходной шине 9 соответствует началу первого бита информационного блока кадра на выходной шине 10.

Формула изобретения

Устройство цикловой синхронизации воспроизведения цифровой информации с носителя магнитной записи содержащее щину тактовой синхронизации, последовательно соединенные информационную шину, регистр сдвига, дешифратор маркера, и первый триггер, последовательно соединенные информационную шину, регистр сдвига, дешифратор маркера и первый триггер, последовательно соединенные элемент И, элемент ИЛИ и выходную шину сигнала цикловой синхронизации, первый и второй счетчики импульсов, второй и третий триггеры и элемент задержки, отличающееся тем, что, с целью уменьшения погрешности цикловой синхронизации, в него введен четвертый триггер, подсоединенный к двум выходам первого счетчика импулъ- сов и соединенный выходом с вторым входом элемента ИЛИ, выход которого соединен дополнительно с установочным входом первого счетчика импульсов, третий выход которого соединен с первыми входами второго и третьего триггеров, выход последнего из которых соединен с вторым входом второго триггера, выходом соединенного с первым входом элемента И, выход которого соединен дополнительно с установочным входом второго счетчика импульсов, счетный вход и выход которого соединены соответственно с инверсным выходом и третьим входом второго триггера, при этом второй вход третьего триггера

соединен с одним из выходов первого счетчика импульсов, а тактовый вход регистра сдвига, счетный вход первого счетчика импульсов, второй вход первого триггера и третьи входы третьего и четвертого триггеров подключены к выходу элемента задержки, вход которого соединен с шиной тактовой синхронизации и с третьим входом первого триггера, выходом соединенного с вторым входом элемента И.

| Устройство для цикловой синхронизации цифрового видеомагнитофона | 1986 |

|

SU1377906A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Патент США № 3792443, кл | |||

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для воспроизведения цифровой информации с носителя магнитной записи | 1986 |

|

SU1365117A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1990-10-15—Публикация

1989-02-13—Подача