Вход

сл

00 00

Изобретение относится к радиотехнике и может использоваться в системах передачи информации и аппаратуре магнитной записио

Цель изобретения - повышение скорости демодуляции.

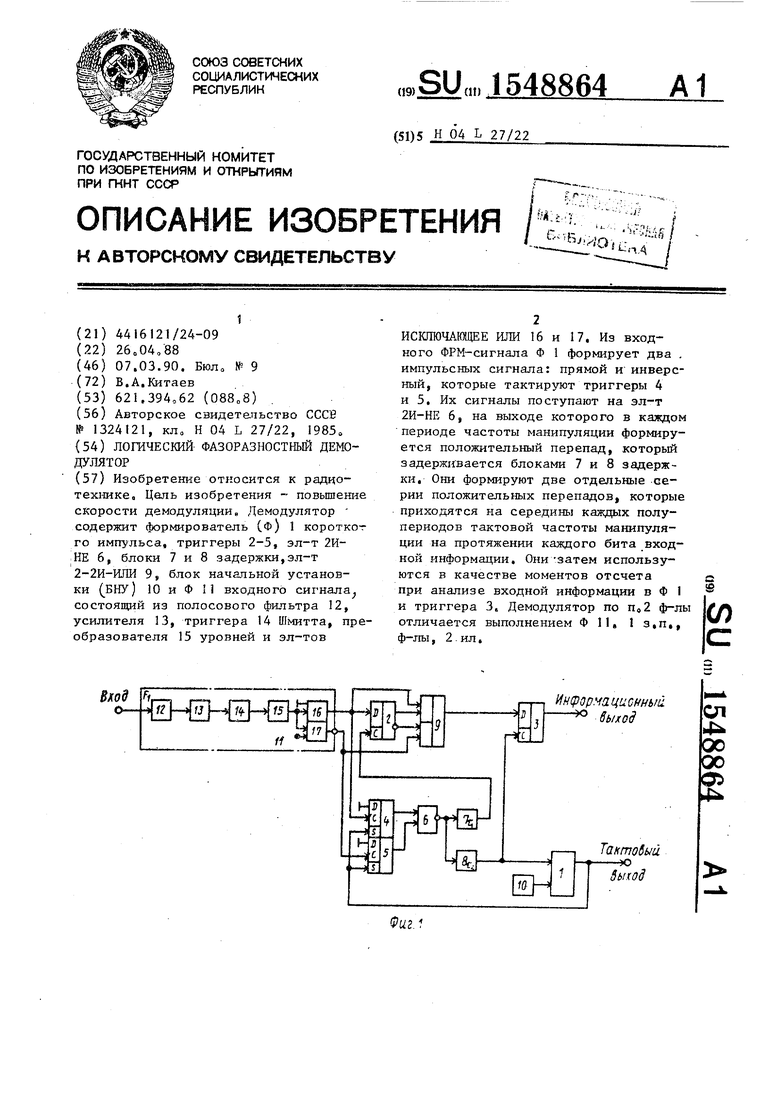

На фиг.1 представлена структурная электрическая схема предлагаемого логического фазоразностного демодулятора; на фиг02 - эпюры напряжения, поясняющие его работу0

Логический фаэоразностный демодулятор содержит формирователь 1 короткого импульса, первый 2, второй 3, третий 4 и четвертый 5 триггеры, элемент 2И-НЕ 6, первый 7 и второй 8 блоки задержки, элемент 2- 2И-ИЛИ 9, блок 10 начальной установки формирователь 11 входного сигнала, состоящий из полосового фильтра 12, усилителя 13, триггера Шмитта 14, преобразователя 15 уровней, первого 16 и второго 17 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Логический фазоразностный демодулятор работает следующим образом0

Входной ФРМ сигнал (фиг,2а) из канала связи через полосовой фильтр

12(фиг.1J формирователя 11 входного сигнала поступает на вход усилителя

13(обычно с симметричными напряжениями питания ± ииит), где с необходимым коэффициентом линейно усиливается и поступает на вход триггера Шмитта 14, который может быть выполнен на основе достаточно быстродействующего интегрального компаратора с регулируемым уровнем порога срабатывания и соответствующей петлей гистерезиса, что увеличивает помехоустойчивость приема входной информации при наличии определенного помехового уровня в канале связи,,

Затем в преобразователе 15 уровне ФРМ-сигнал подвергается преобразованию уровней, которое необходимо для согласования уровней выходного сигнала триггера Шмитта 14 с цифровыми входами первого 16 и второго 17 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ

К второму входу первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 16 постоянно подсоединен нулевой потенциал, поэтому выход этого элемента является прямым выходом формирователя 11 входного сигнала, а к второму входу второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 17 постоянно подключен высокий потенциал, по

0

5

0

5

0

этому его выход является инверсным выходом формирователя 11 входного сигнала. Первый 16 и второй 17 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ должны располагаться в одном кристалле для обеспечения одинаковых временных задержек. Таким способом устраняется разница в задержках прямого и инверсного сигналов на выходе формирователя 11 входного сигнала.

С формирователя 11 входного сигнала прямой и инверсный Офиг.2б,в) импульсные сигналы поступают на тактовые входы третьего 4 и четвертого 5 триггеров, которые тактируются, например, положительным фронтом и один из двух сигналов, прямой или инверсный устанавливает выход третьего 4 (фиг.2г) или четвертого 5 триг- гера (фиг,2д) в нулевое состояние, так как к информационным D-входам третьего 4 и четвертого 5 триггеров постоянно подключен нулевой потенциал

Отрицательный перепад напряжения с одного из выходов либо третьего 4Р либо четвертого 5 трип еров проходит на выход элемента 2И-НЕ 6 через один из входов этого элемента 2И- НЕ б, так как на другой вход этого элемента 2И-НЕ 6 подключается высокий потенциал в момент начала каждой последней четгерти интервала TO частоты манипуляции фазоразностного сигнала, С выхода элемента 2И-НЕ 6 положительный перепад напряжения (фиг.2е) поступает на входы первого 7 и второго 8 блоков задержек9 которые задерживают этот положительный перепад соответственно первый на четверть периода

частоты манипуляции

0,25 Т,

(фиг,2ж) и второй на три четверти периода частоты манипуляции 0,75 Т0 (фиг.2з),.

После момента времени с-г 0,75 Т0

на каждом интервале частоты манипулял ции формирователем 1 короткого импульса формируется отрицательный короткий импульс (фиг.2и), который производит очередную установку третьего 4 и четвертого 5 триггеров в исходное единичное состояние по выходам, при этом на выходе элемента 2И-НЕ 6 устанавливается низкий нулевой уровень и схема демодулятора таким образом каждый раз подготавливается к последующему циклу демодуляции на

следующем интервале частоты манипуляции - Т0 .

Таким образом, на выходе элемента 2И-НЕ 6 в каждом периоде частоты ма- нипуляции формируется положительный перепад, который задерживается первым 7 и вторым 8 блоками задержек На выходах первого (фиг.2ж) и второго (фиг.2з) блоков задержек ф ормиру.- ются две отдельные серии положительных перепадов, которые приходятся на середины каждых полупериодов тактовой частоты манипуляции на протяжении каждого бита входной информации и затем используются в качестве моментов отсчета при анализе входной информации.

Анализ проводится в соответствии с таблицей и заключается в том, что логический фаэоразностный демодулятор фиксирует меняется или нет полярность импульсного сигнала, сформированного формирователем 1 входного сигнала на протяжении тактового интервала Т ,

Примечание. XI- уровень входнго ФРМ-сигнала в момент 0,25 Т0; Х2 - уровень входного ФРМ-сигнала в момент 0,75 Т0; Y - выходной сигнал0

Изменение полярности означает появление О на выходе логического фазоразностного демодулятора (фаза несущего колебания входного сигнала остается неизменной). Отсутствие такого изменения означает появление 1 на выходе демодулятора. Отсчеты для анализа берутся в моменты времени 0,25 Т0 и 0,75 Т0 каждого бита входной информации.

Логическая функция У реализуется элементом 2-2И-ИЛИ 9, при этом первый триггер 2 фиксирует уровень входного сигнала в момент времени 0,25.Т0 на протяжении каждого бита входного фазоразностного сигнала. Эпюры напряжений показаны на прямом и инверсном выходах первого триггера 2 (фиг,2к,л) на выхо5

0 5

0

5

0

5

0

5

де элемента 2-2П -НЛТ1 9 (фиг. 2м), Выходной сигнал в прямой двоичной форме появляется на выходе второго триггера 3 (фиг,2н) в моменты времени 0,75 Т0 каждого бита входного фазоразностного сигнала с задержкой от этого момента, равной времени распространения в смехе второго триггера 3 и сопровождается отслеживающей синхронизацией с выхода формирователя 1 короткого импульса (фиг02п)

При начальном включении логического фазоразностного демодулятора третий 4 и четвертый 5 триггеры могут установиться в такие состояния по выходам, что на выходе элемента 2И-НЕ б постоянно установится высокий потенциал, а это приводит к невозможности демодуляции, так как ка выходе элемента 2И-НЕ 6 не сформирован начальный, первый попожитепъный перепад и третий 4 и четвертый 5 триггеры не переведены начально в единичное состояние по своим установочным S-входам. Для исключения такого мертвого состояния в устройство введен блок 10 начальной установки, который при включении питания формирует на своем выходе отрицательный импульс достаточной длительности, поступающий на второй вход схемы формирователя I короткого импульса и, если третий 4 и четвертый 5 триггеры устанавливаются при включении в такие состояния, когда на выходе элемента 2И-НЕ 6 и второго блока 8 задержки установлен первоначально высокий уровень, то этот отрицательный импульс производит установку по S-устаноБОЧным входам третьего 4 и четвертого 5 триггеров в единичное состояние и подготавливает логический фазоразностный демодулятор к р а- боте.

Формула изобретения

1. Логический фазоразностный демодулятор, содержащий последовательно соединенные формирователь входного сигнала, первый триггер, элемент 2-2И-ИЛИ и второй триггер, выход которого является информационным выходом демодулятора8 входом которого является вход формирователя входного сигнала, первый выход которого подключен к тактовому входу третьего триггера и к второму входу элемента

2-2H-HnHj, третий и четвертый входы которого соединены соответственно с инверсным выходом первого триггера и с вторым выходом формирователя входного сигналаs который подключен к тактовому входу четвертого триггера, информационный вход которого соединен с информационным входом третьего триггера и общей шиной, о т л и- чающийся тем, что9 с целью повышения скорости демодуляции, введены два блока задержки,, элемент 2И-НЕ и последовательно соединенные блок начальной установки и формирова тель короткого импульса, выход которого подключен к установочным входам третьего и четвертого триггеровf выходы которых соединены с входами

элемента 2И-НЕ5 выход которого подключен к входу первого блока задержки ,, выход которого соединен с тактовым входом первого триггера, и к входу второго блока задержки выход

Q 5

0

второго триггера и с вторым входам формирователя короткого импульса, выход которого является тактовым выходом демодулятора,

2. Демодулятор по п01, о т л и - чающийся тем, что формирователь входного сигнала содержит два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и последовательно соединенные полосовой фильтр, усилитель, триггер Шмитта и преобразователь уровней, выход кото,- рого подключен к первым входам первого и второго элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которых являются соответственно первым и вторым выходами формирователя входного сигнала, входом которого является вход полосового фильтра, при этом второй вход первого элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с общей шиной, а второй вход второго элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является потенциальным входом форми

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический фазоразностный демодулятор | 1987 |

|

SU1443199A1 |

| Логический фазоразностный демодулятор | 1985 |

|

SU1324121A1 |

| СИСТЕМА АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ АЛС | 2023 |

|

RU2815588C1 |

| СТАРТСТОПНАЯ СИСТЕМА СВЯЗИ | 2000 |

|

RU2177209C2 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2002 |

|

RU2223609C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2002 |

|

RU2233040C2 |

| Генератор концентрических окружностей для телевизионного индикатора | 1983 |

|

SU1124373A1 |

| Устройство для приема дискретных сообщений | 1988 |

|

SU1559417A1 |

| Цифровой демодулятор сигналов фазоразностной модуляции первого и второго порядка | 1991 |

|

SU1838884A3 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1998 |

|

RU2136114C1 |

Изобретение относится к радиотехнике. Цель изобретения - повышение скорости демодуляции. Демодулятор содержит формирователь (Ф) 1 короткого импульса, триггеры 2 - 5, эл-т 2 И-НЕ 6, блоки 7 и 8 задержки, эл-т 2 - 2 И-ИЛИ 9, блок начальной установки (БНУ) 10 и Ф 11 входного сигнала, состоящий из полосового фильтра 12, усилителя 13, триггера 14 Шмидта, преобразователя 15 уровней и эл-тов ИСКЛЮЧАЮЩЕЕ ИЛИ 16 и 17. Из входного ФМН сигнала Ф 1 формирует два импульсных сигнала: прямой и инверсный, которые тактируют триггеры 4 и 5. Их сигналы поступают на эл-т 2И-НЕ 6, на выходе которого в каждом периоде частоты манипуляции формируется положительный перепад, который задерживается блоками 7 и 8 задержки. Они формируют две отдельные серии положительных перепадов, которые приходятся на середины каждых полупериодов тактовой частоты манипуляции на протяжении каждого бита входной информации. Они затем используются в качестве моментов отсчета при анализе входной информации в Ф 1 и триггере 3. Демодулятор по п.2 ф-лы отличается выполнением Ф 11. 1 з.п. ф-лы, 2 ил.

которого соединен с тактовым входом 25 рователя входного сигналас

и

| Логический фазоразностный демодулятор | 1985 |

|

SU1324121A1 |

Авторы

Даты

1990-03-07—Публикация

1988-04-26—Подача