Изобретение относится к связи и ожет найти применение при построеии приемников цифровых систем пеедачи информации.

Целью изобретения является повыение скорости приема информации ри увеличении кратности манипуляции.

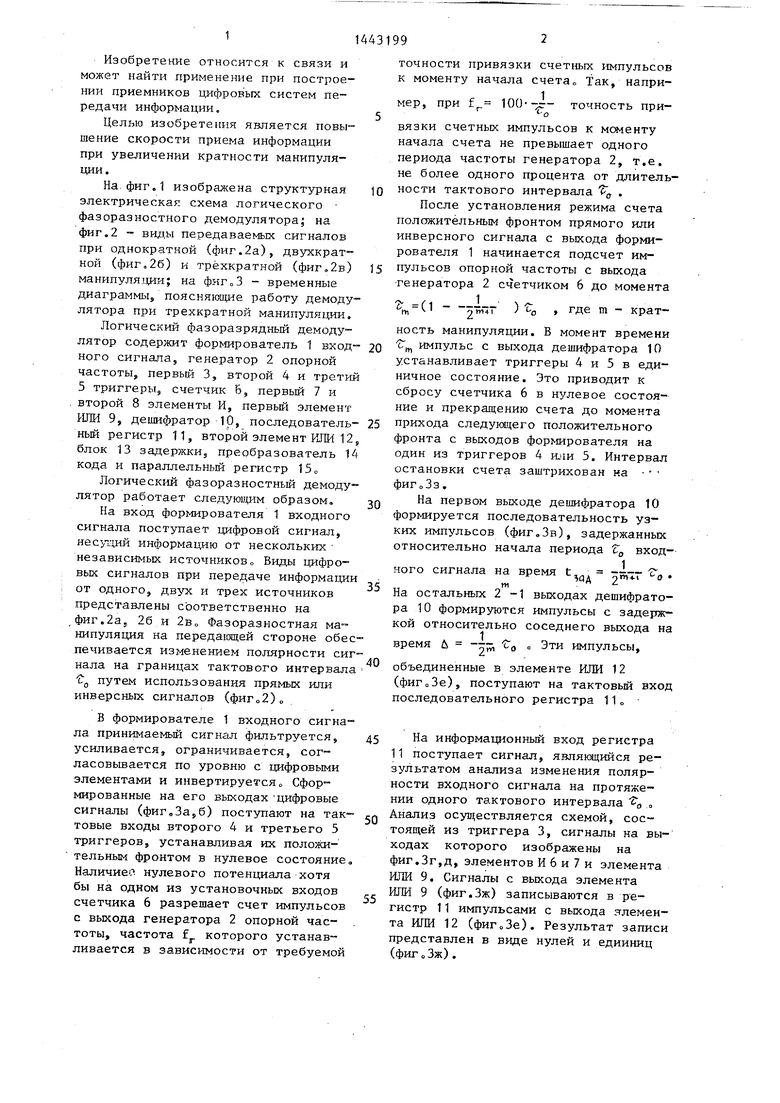

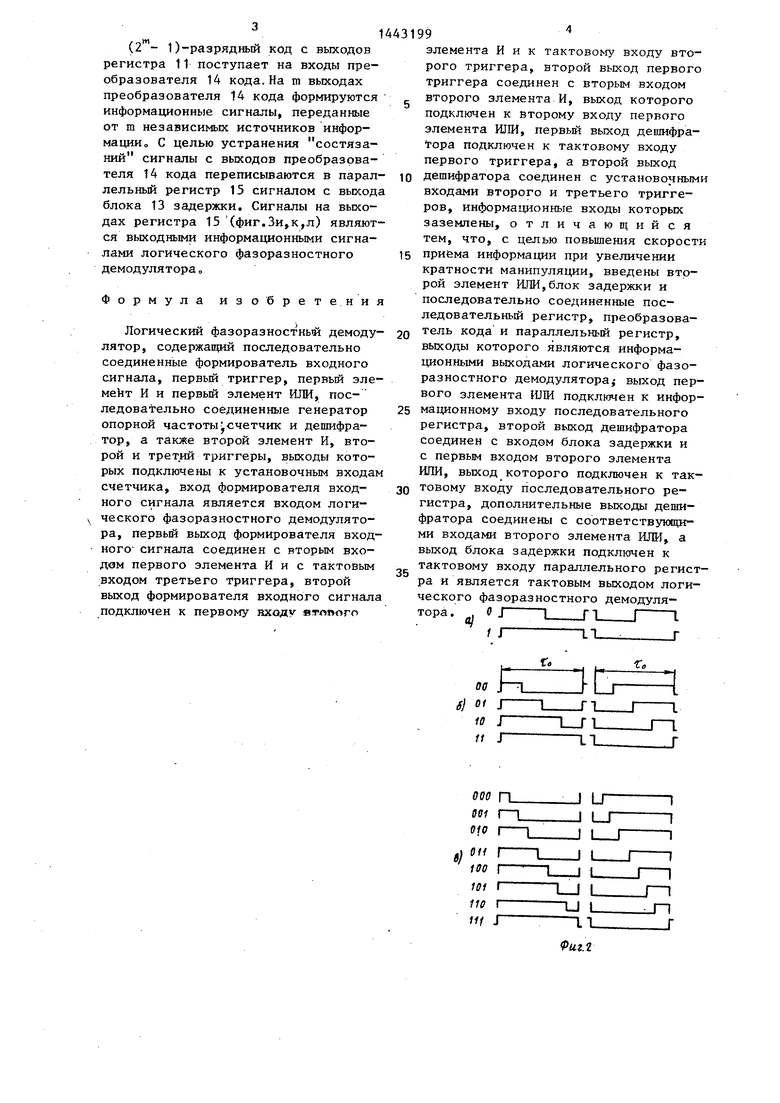

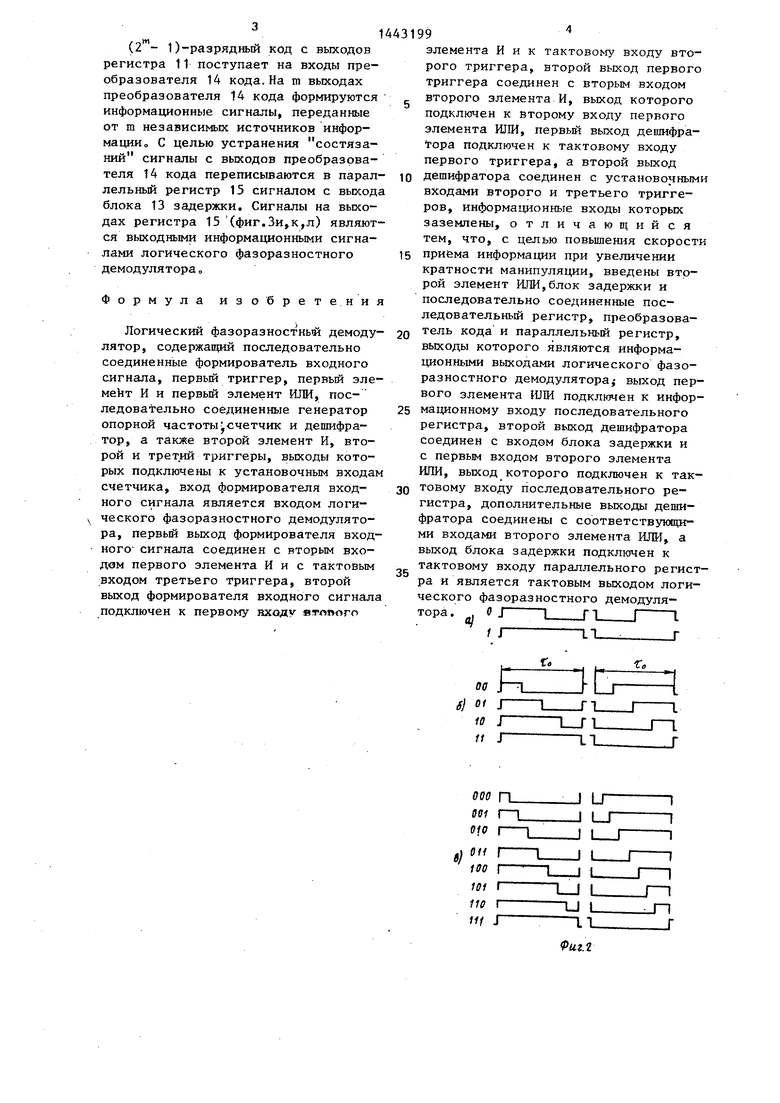

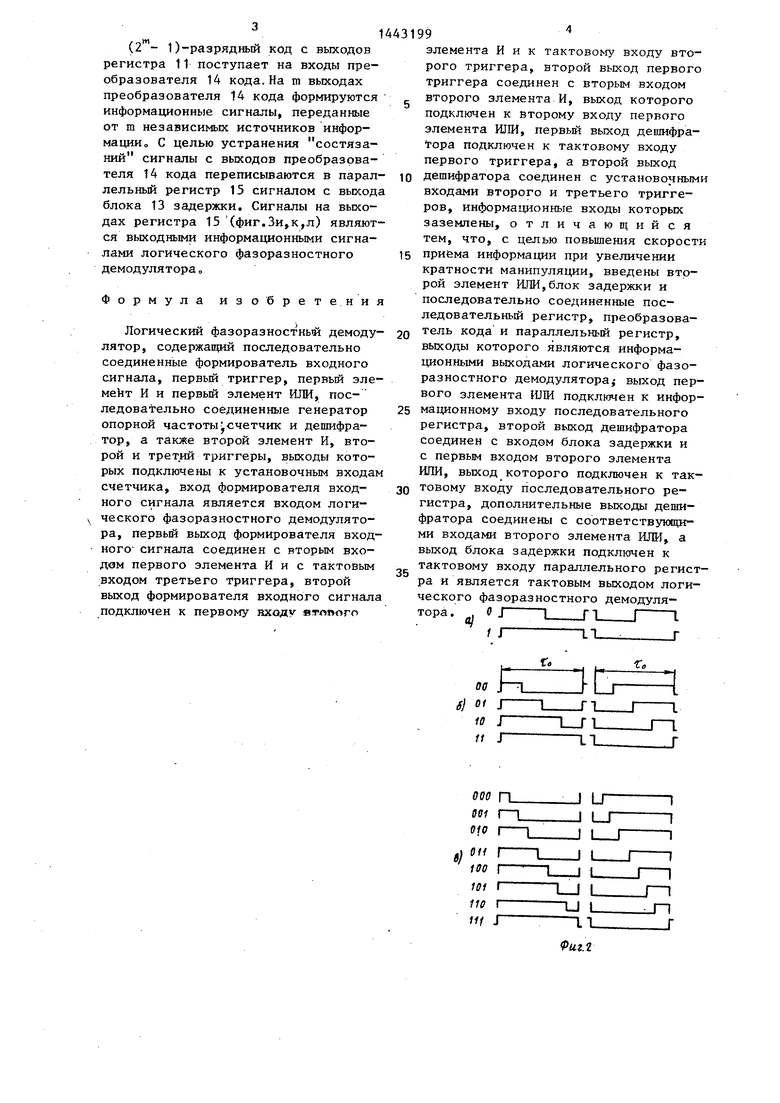

На. фиг.1 изображена структурная электрическая схема логического азоразностного демодулятора на иг.2 - виды передаваемых сигналов при однократной (фиг.2а), дву скрат- ной (фиг,26) и трёхкратной (фиг,2в) манипуля1щи; на фиГоЗ - временные иаграммы, поясняюище работу демодуятора при трехкратной манипуляции.

Логический фазоразрядный демодуятор содержит формирователь 1 входного сигнала, генератор 2 опорной частоты, первый 3, второй 4 и третий 5 триггеры, счетчик Б, первьй 7 и второй 8 элементы И, первый элемент 1-ШИ 9, дешифратор 10, последователь- ньй регистр 11, второй элемент ИЛИ 12, блок 13 задержки2 преобразователь 14 кода и параллельный регистр 15„

Логический фазоразностньй демодулятор работает следуюи;им образом.

На вход формирователя 1 входного сигнала поступает цифровой сигнал, информацию от нескольких независимых источников Виды цифровых сигналов при передаче информации от одного, двух и трех источников представлены соответственно на фиг.2а5 26 и 2во Фазоразностная ма нипуляция на переда сщей стороне обеспечивается изменением полярности сигнала на границах тактового интервала Lg путем использования прямых или инверсных сигналов (фиго2)„

В формирователе 1 входного сигнала принимаемьй сигнал фильтруется, усиливается, ограничивается, сог- ласовьшается по уровню с цифровыми элементами и инвертируется„ Сформированные на его выходах цифровые сигналы (фиг.) поступают на тактовые входы второго 4 и третьего 5 триггеров, устанавливая их положи- тельным фронтом в нулевое состояние Наличие нулевого потенциала хотя бы на одном из установочных входов счетчика 6 разрешает счет импульсов с выхода генератора 2 опорной час- , тоты, частота f. которого устанавливается в зависимости от требуемой

точности привязки счетш.х импульсов к моменту начала счета Так, например, при f 100--XT- точность при

вязки счетных импульсов к моменту

начала счета не превышает одного периода частоты генератора 2, т.е. не более одного процента от длительности тактового интервала f .

После установления режима счета положительным фронтом прямого или инверсного сигнала с выхода формирователя 1 начинается подсчет импульсов опорной частоты с выхода генератора 2 счетчиком 6 до момента

2 ( ) о , где m - кратность манипуляции. В момент времени

t импульс с выхода дешифратора 10 устанавливает триггеры 4 и 5 в единичное состояние. Это приводит к сбросу счетчика 6 в нулевое состояние и прекращению счета до момента

прихода следукяцего положительного фронта с выходов формирователя на один из триггеров 4 или 5. Интервал остановки счета заштрихован на фигоЗз,

На первом выходе дешифратора 10 формируется последовательность уз ких импульсов (фиг.Зв), задержанных относительно начала периода Г входного сигнала на время t,. -rffir о

1

На остальных 2 -1 выходах дешифратора 10 формируются импульсы с задержкой относительно соседнего выхода на

время Л -r;7i ° Эти импульсы,

объединенные в элементе ИЛИ 12

(фиГоЗе), поступают на тактовый вход последовательного регистра 11 о

5 На информационный вход регистра 11 поступает сигнал, являкяцийся результатом анализа изменения полярности входного сигнала на протяжении одного тактового интервала о о

Q Анализ осуществляется схемой, состоящей из триггера 3, сигналы на выходах которого изображены на фиг,3г,д, элементов И 6 и 7 и элемента ИЛИ 9. Сигналы с выхода элемента ИЛИ 9 (фиг.Зж) записываются в регистр 11 импульсами с выхода аглемен- та ИЛИ 12 (фиГоЗе). Результат записи представлен в виде нулей и едииниц (фиГоЗж).

(2 - 1)-разрядный код с выходов регистра 11 поступает на входы преобразователя 14 кода.На m выходах преобразователя 14 кода формируются информационные сигналы, переданные от m независимых источников информации С целью устранения состязаний сигналы с выходов преобразователя 14 кода переписываются в парал- лельньй регистр 15 сигналом с выхода блока 13 задержки. Сигналы на выходах регистра 15 (фиг.3и,к,л) являются выходными информационными сигналами логического фазоразностного демодулятора„

Формула изобретения

Логический фазоразностный демодулятор, содержащий последовательно соединенные формирователь входного сигнала, первый триггер, первый эле- меНт И и первый элемент ИЛИ, последовательно соединенные генератор опорной частотыусчетчик и дешифратор, а также второй элемент И, второй и третий триггеры, выходы которых подключены к установочным входам счетчика, вход формирователя входного сигнала является входом логического фазоразностного демодулятора, первый выход формирователя вход- ного сигнала соединен с вторым входом первого элемента И и с тактовым входом третьего триггера, второй выход формирователя входного сигнала подключен к первому входу

0

5

5

0

5

элемента Инк тактовому входу второго триггера, второй вькод первого триггера соединен с вторым входом второго элемента И, выход которого подключен к второму входу первого элемента ШШ, первьй выход дешифратора подключен к тактовому входу первого триггера, а второй выход дешифратора соединен с установочными входами второго и третьего триггеров, информационные входы которых заземлены, отличающийся тем, что, с целью повышения скорости приёма информации при увеличении кратности манипуляции, введены второй элемент ИЛИ,блок задержки и последовательно соединенные последовательный регистр, преобразователь кода и параллельный регистр, выходы которого являются информационными выходами логического фазоразностного демодулятора выход первого элемента ШШ подключен к информационному входу последовательного регистра, второй выход дешифратора соединен с входом блока задержки и с первым входом второго элемента ШШ, выход которого подключен к тактовому входу последовательного регистра, дополнительные выходы дешифратора соединены с соответств5тощи- ми входами второго элемента ИЛИ, а выход блока задержки подключен к тактовому входу параллельного регистра и является тактовым выходом логического фазоразностного демодулятора . , О в/

гг

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический фазоразностный демодулятор | 1985 |

|

SU1324121A1 |

| Логический фазоразностный демодулятор | 1988 |

|

SU1548864A1 |

| СИСТЕМА АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ АЛС | 2023 |

|

RU2815588C1 |

| Устройство для контроля цифровых блоков | 1983 |

|

SU1166115A1 |

| Устройство для приема и обработки избыточных сигналов | 1984 |

|

SU1233201A1 |

| Цифровой фазоразностный демодулятор | 1989 |

|

SU1688401A1 |

| Устройство для отладки цифровых систем | 1985 |

|

SU1254492A1 |

| Цифровой коррелятор | 1989 |

|

SU1711181A1 |

| Устройство записи-воспроизведения многоканальной цифровой информации на магнитный носитель | 1991 |

|

SU1777176A1 |

| ПРИЕМНИК СИГНАЛОВ МНОГОЗНАЧНОЙ АВТОМАТИЧЕСКОЙ ЛОКОМОТИВНОЙ СИГНАЛИЗАЦИИ (АЛС-ЕН) | 2007 |

|

RU2347705C2 |

Изобретение может быть использовано при построении приемников цифровых систем передачи информации. Цель изобретения - повышение скорости приема информации при увеличении кратности манипуляции. Уст-во содержит формирователь 1 входного сигнала, г-р 2 опорной частоты, триггеры 3, 4 и 5, счетчик 6, эл-ты И 7 и 8, эл-т ИЛИ 9, дешифратор 10 и последовательный регистр 11„ Для достижения цели в устр-во введены зл-т ИЛИ 12, блок задержки 13, преобразователь 14 кода и параллель- ньй регистр 15. 3 ило

000 п

001 010

д-u- i jii. .., . . . ,un, ...../

и 11111 ft t 000 a ft 11100 fJoJJJT noooTo 1111110 & iuoit i

JFH.ra

| Логический фазоразностный демодулятор | 1985 |

|

SU1324121A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1988-12-07—Публикация

1987-01-16—Подача