Изобретение относится к электро- . измерениям и может быть использовано для измерения среднего значения тока в последовательности импульсов произвольной формы и длительности.

Цель изобретения - расширение области использования устройства за счет обеспечения измерения среднего значения тока последовательности импульсов произвольной формы и длительности.

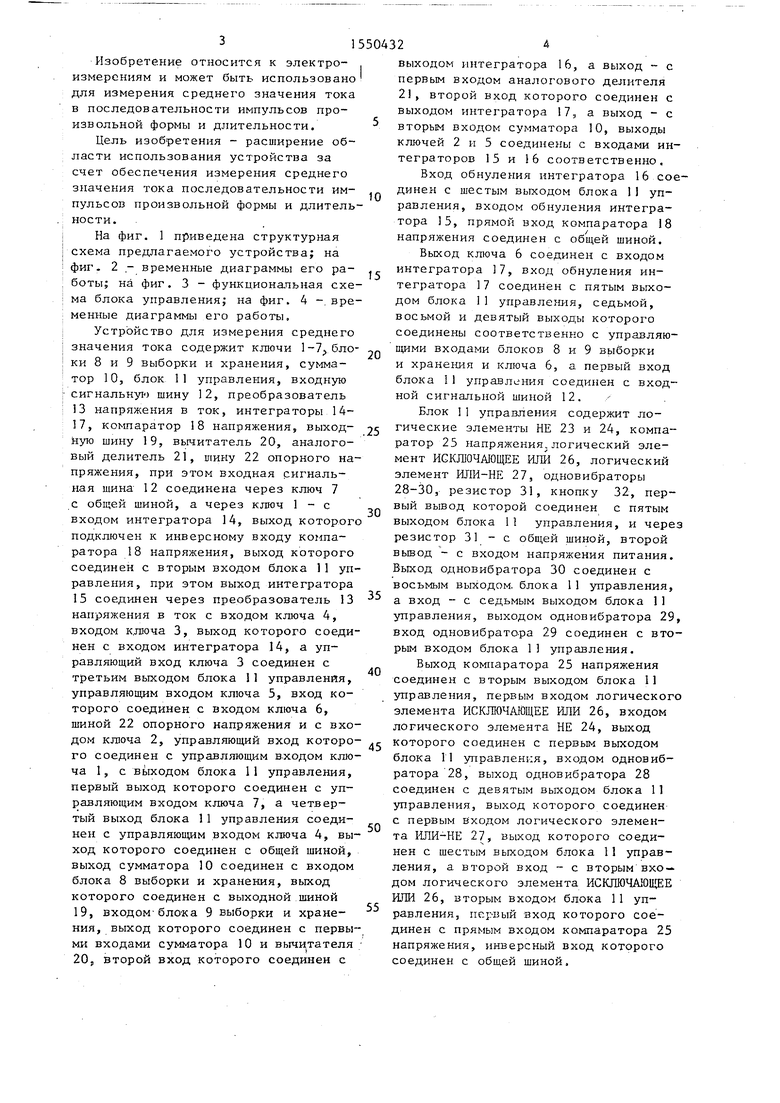

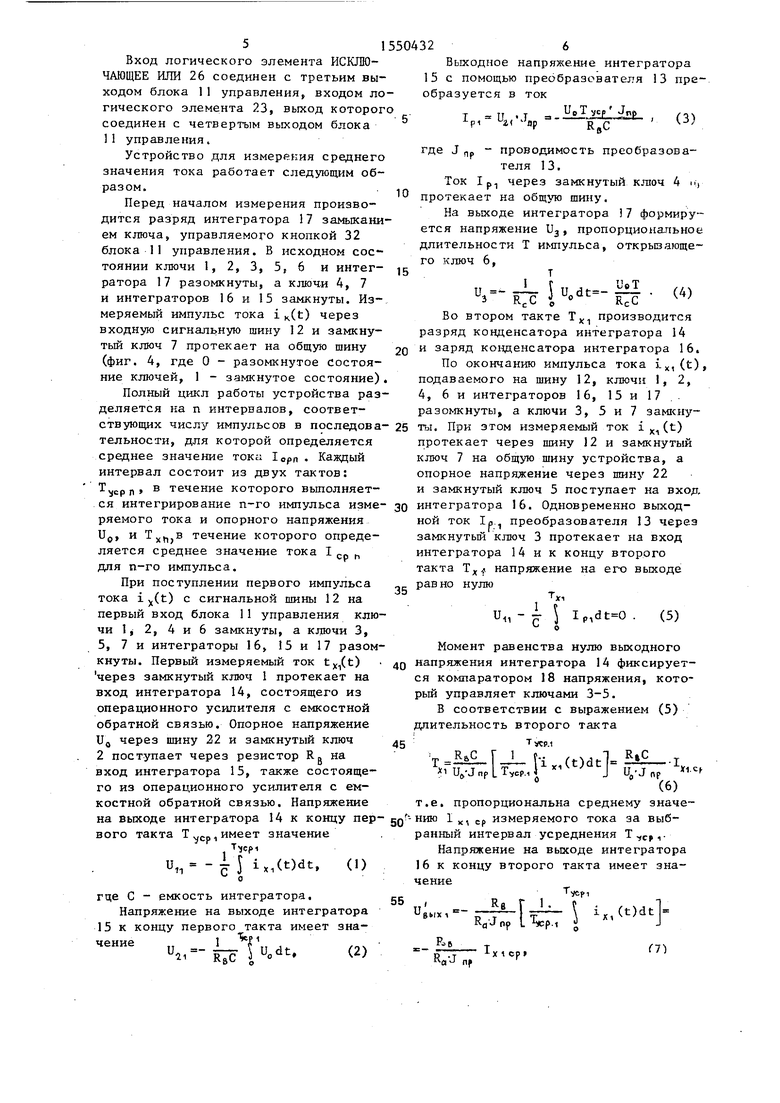

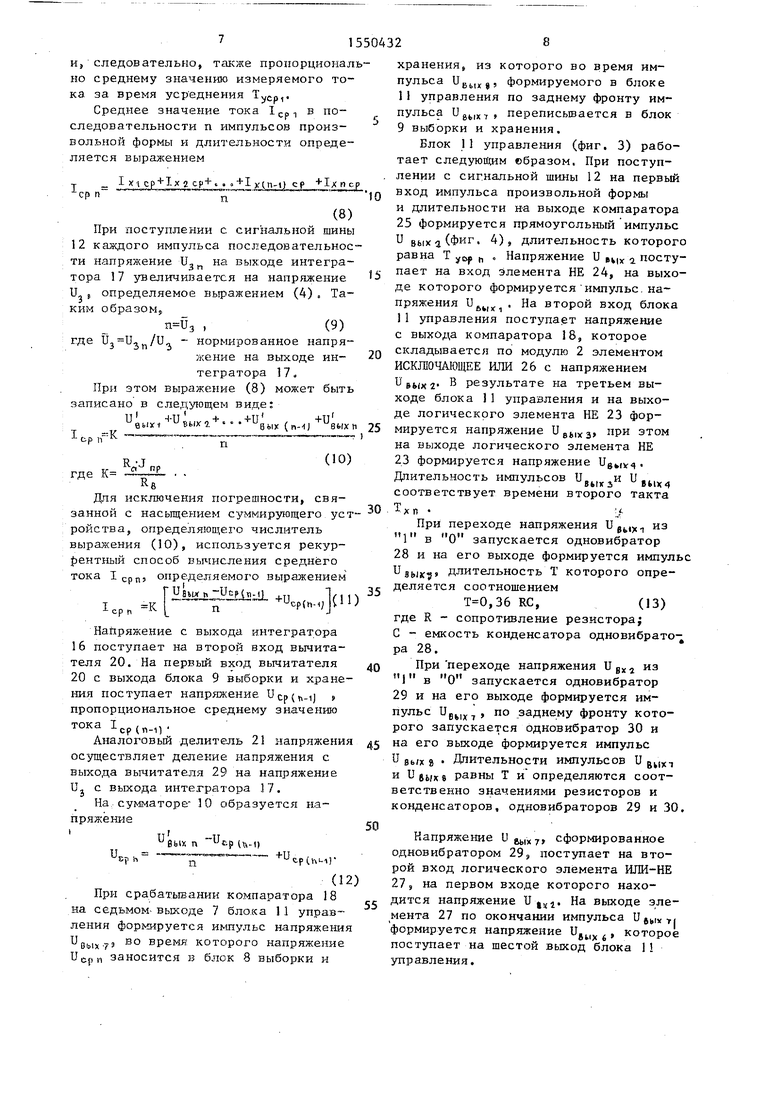

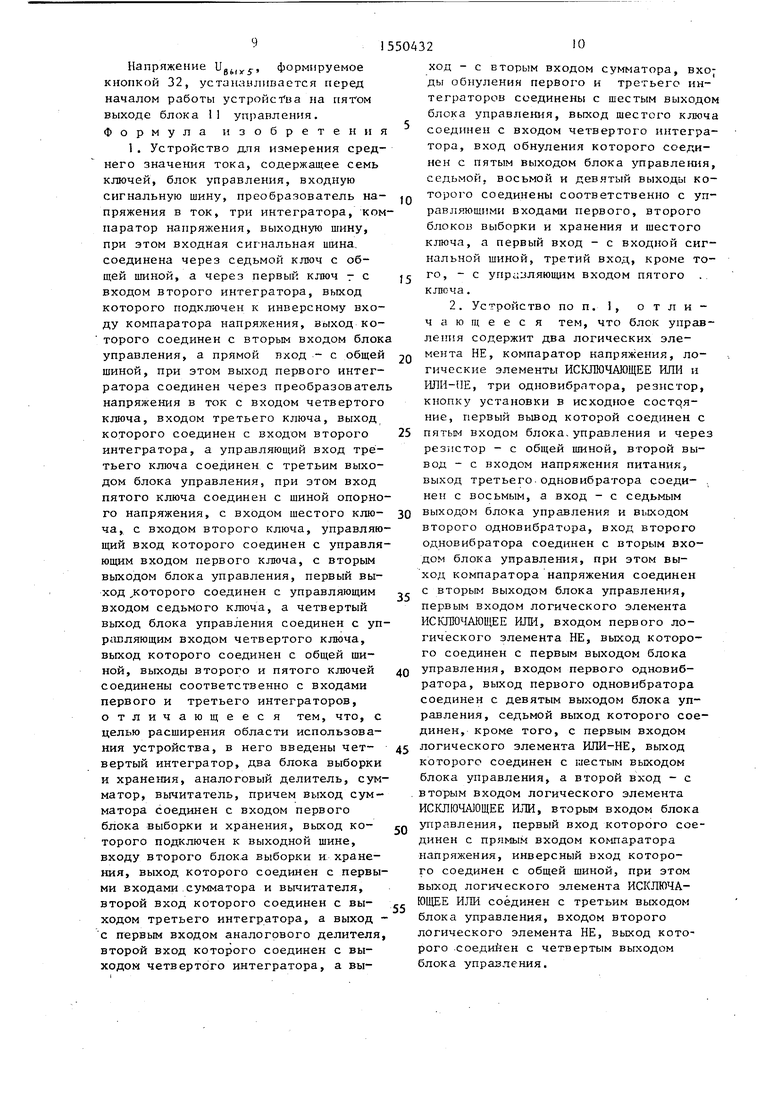

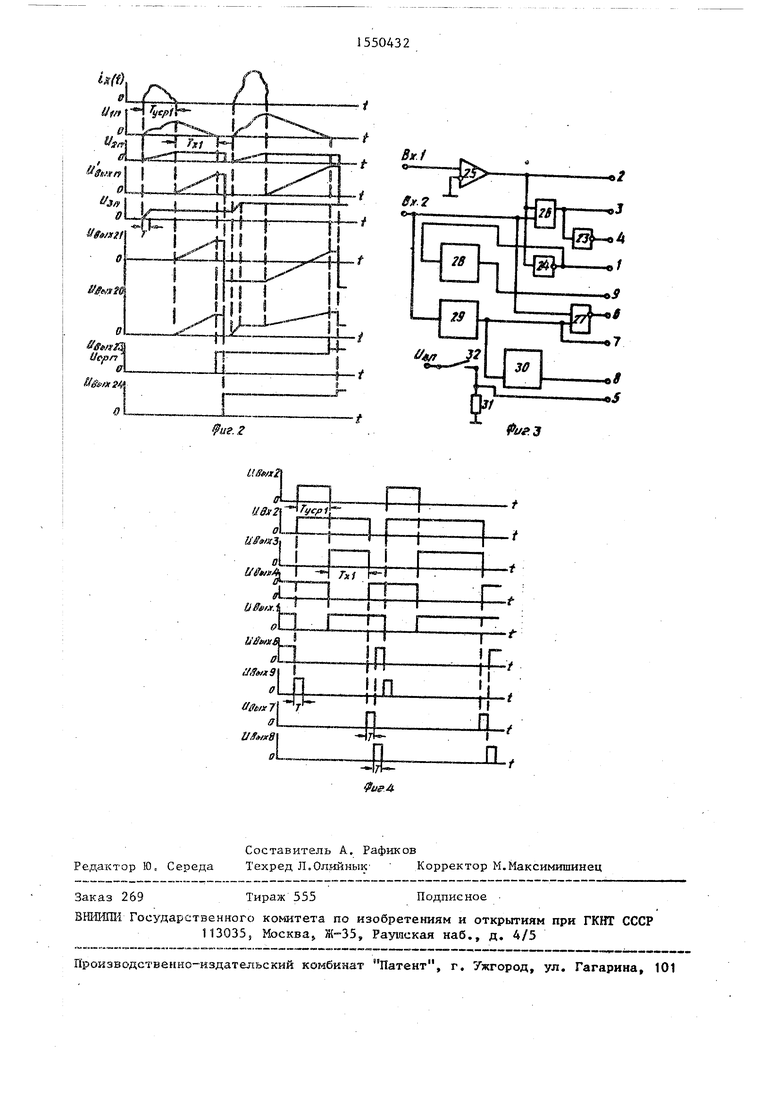

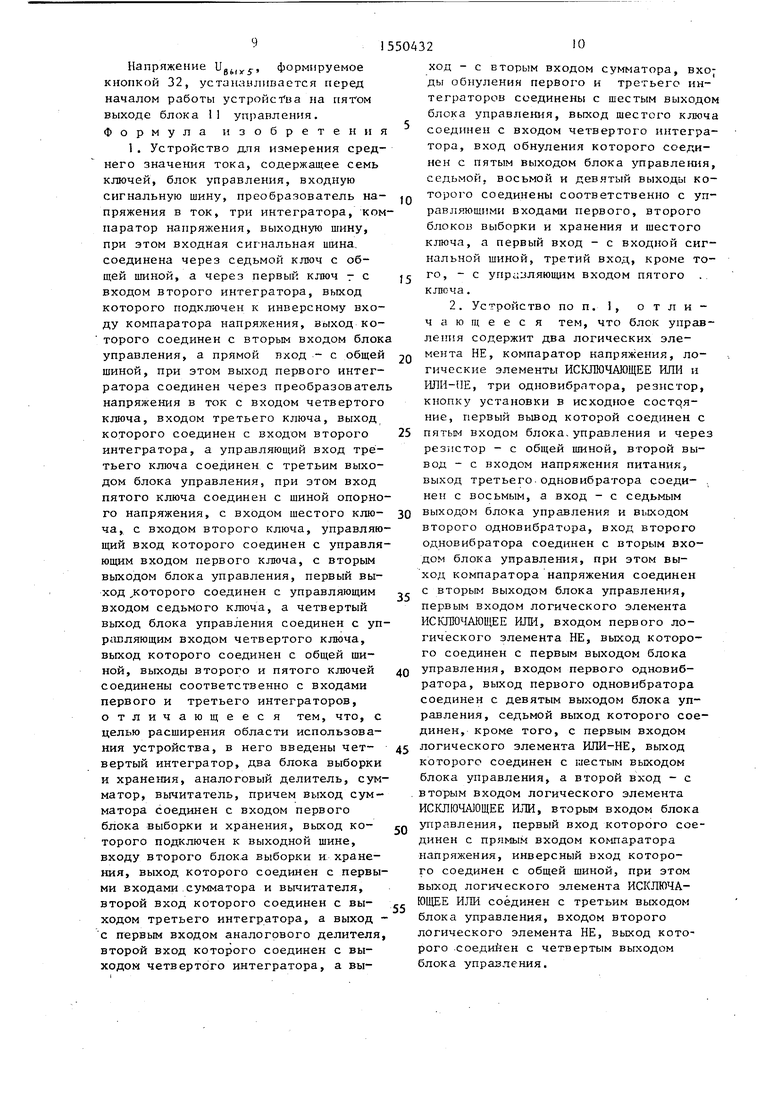

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - временные диаграммы его ра- боты; на фиг. 3 - функциональная схема блока управления; на фиг. 4 - временные диаграммы его работы.

Устройство для измерения среднего значения тока содержит ключи 1-7, блоки 8 и 9 выборки и хранения, сумматор 10, блок 11 управления, входную сигнальную шину 12, преобразователь 13 напряжения в ток, интеграторы 14- 17, компаратор 18 напряжения, выходную шину 19, вычитатель 20, аналоговый делитель 21, шину 22 опорного напряжения, при этом входная сигнальная шина 12 соединена через ключ 7 с общей шиной, а через ключ 1 - с входом интегратора 14, выход которого подключен к инверсному входу компаратора 18 напряжения, выход которого соединен с вторым входом блока 11 управления, при этом выход интегратора 15 соединен через преобразователь 13 напряжения в ток с входом ключа 4, входом ключа 3, выход которого соединен с входом интегратора 14, а управляющий вход ключа 3 соединен с третьим выходом блока 11 управления, управляющим входом ключа 5, вход которого соединен с входом ключа 6, шиной 22 опорного напряжения и с вхо

0

,.

5

0

5

0

выходом интегратора 16, а выход - с первым входом аналогового делителя 2, второй вход которого соединен с выходом интегратора 17, а выход - с вторым входом сумматора 10, выходы ключей 2 н 5 соединены с входами интеграторов 15 и 16 соответственно.

Вход обнуления интегратора 16 соединен с шестым выходом блока 11 управления, входом обнуления интегратора 15, прямой вход компаратора 18 напряжения соединен с общей шиной.

Выход ключа 6 соединен с входом интегратора 17, вход обнуления интегратора 17 соединен с пятым выходом блока 11 управления, седьмой, восьмой и девятый выходы которого соединены соответственно с управляющими входами блоков 8 и 9 выборки и хранения и ключа 6, а первый вход блока 11 управления соединен с входной сигнальной шиной 12.

Блок управления содержит логические элементы НЕ 23 и 24, компаратор 25 напряжения.логический элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 26, логический элемент ИЛИ-НЕ 27, одновибраторы 28-30, резистор 31, кнопку 32, первый вывод которой соединен с пятым выходом блока 1 управления, и через резистор 31 - с общей шиной, второй вывод - с входом напряжения питания. Выход одновибратора 30 соединен с восьмым выходом, блока 11 управления, а вход - с седьмым выходом блока 11 управления, выходом одновибратора 29, вход одновибратора 29 соединен с вторым входом блока И управления.

Выход компаратора 25 напряжения соединен с вторым выходом блока 11 управления, первым входом логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26, входом логического элемента НЕ 24, выход

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ измерения рассогласования между углами поворота,один из которых задан кодом | 1985 |

|

SU1285595A1 |

| Система управления | 1983 |

|

SU1168896A1 |

| Измерительный преобразователь активной мощности | 1989 |

|

SU1659890A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ЭЛЕКТРИЧЕСКИХ ПАРАМЕТРОВ | 1991 |

|

RU2017161C1 |

| Устройство для измерения рассогласования между углом и кодом | 1987 |

|

SU1411973A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1200421A1 |

| Амплитудно-фазовый анализатор гармоник | 1985 |

|

SU1272272A2 |

| Дифференцирующее устройство | 1990 |

|

SU1749899A2 |

| Электромагнитный расходомер | 1988 |

|

SU1522041A1 |

| Многоканальное устройство для записи и воспроизведения аналоговой информации | 1989 |

|

SU1615792A1 |

Изобретение относится к электроизмерительной технике и может найти применение при научных исследованиях в технической диагностике и в промышленных измерительно-вычислительных комплексах для испытания полупроводниковых приборов. Цель изобретения - расширение области использования устройства за счет обеспечения измерения среднего значения тока последовательности импульсов произвольной формы и длительности. Для этого в устройство введены интегратор 17, блоки 8 и 9 выборки и хранения соответственно, делитель 21, сумматор 10, вычитатель 20. Устройство содержит также ключи 1 - 7, блок 11 управления, входную шину 12, преобразователь 13 напряжения в ток, интеграторы 14 - 16, компаратор 18, выходную шину 19, шину 22 опорного напряжения. 4 ил.

дом ключа 2, управляющий вход которо- которого соединен с первым выходом

го соединен с управляющим входом ключа 1 , с выходом блока 11 управления, первый выход которого соединен с управляющим входом ключа 7, а четвертый выход блока 11 управления соединен с управляющим входом ключа 4, выход которого соединен с общей шиной, выход сумматора 10 соединен с входом блока 8 выборки и хранения, выход которого соединен с выходной шиной

19,входом блока 9 выборки и хранения, выход которого соединен с первыми входами сумматора 10 и вычитателя

20,второй вход которого соединен с

50

55

блока 11 управления, входом одновиб ратора 28, выход одновибратора 28 соединен с девятым выходом блока 11 управления, выход которого соединен с первым входом логического элемента ИЛИ-НЕ 27, выход которого соединен с шестым выходом блока 11 управ ления, а второй вход - с вторым вхо дом логического элемента ИСКЛЮЧАЮЩЕ ИЛИ 26, вторым входом блока 11 управления, псгвый вход которого соединен с прямым входом компаратора 2 напряжения, инверсный вход которого соединен с общей шиной.

которого соединен с первым выходом

блока 11 управления, входом одновибратора 28, выход одновибратора 28 соединен с девятым выходом блока 11 управления, выход которого соединен с первым входом логического элемента ИЛИ-НЕ 27, выход которого соединен с шестым выходом блока 11 управления, а второй вход - с вторым входом логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26, вторым входом блока 11 управления, псгвый вход которого соединен с прямым входом компаратора 25 напряжения, инверсный вход которого соединен с общей шиной.

Вход логического элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 26 соединен с третьим выходом блока 11 управления, входом логического элемента 23, выход которого соединен с четвертым выходом блока 11 управления.

Устройство для измерения среднего значения тока работает следующим образом.

Перед началом измерения производится разряд интегратора 17 замыканием ключа, управляемого кнопкой 32 блока 11 управления. В исходном состоянии ключи 1, 2, 3, 5, 6 и интегратора 17 разомкнуты, а ключи 4, 7 и интеграторов 16 и 15 замкнуты. Измеряемый импульс тока i K(t) через входную сигнальную шину 12 и замкнутый ключ 7 протекает на общую шину (фиг. 4, где 0 - разомкнутое состояние ключей, 1 - замкнутое состояние).

Полный цикл работы устройства разделяется ка п интервалов, соответXI

протекает через шину 12 и замкнутый ключ 7 на общую шину устройства, а опорное напряжение через шину 22 и замкнутый ключ 5 поступает на вход.

ствующих числу импульсов в последова- 25 ты. При этом измеряемый ток iM(t) тельности, для которой определяется среднее значение тока lopn Каждый интервал состоит из двух тактов: Тусрп B течение которого выполняется интегрирование n-го импульса изме- зо интегратора 16. Одновременно выходной ток 1р1 преобразователя 13 через замкнутый ключ 3 протекает на вход интегратора 14 и к концу второго такта Тх напряжение на его выходе „ равно нулю

оОт..

ряемого тока и опорного напряжения

U

о

И TXh,B

течение которого опредетока I

ср п

ляется среднее значение для n-го импульса.

При поступлении первого импульса тока ix(t) с сигнальной шины 12 на первый вход блока 11 управления ключи 1 , 2, 4 и 6 замкнуты, а ключи 3, 5, 7 и интеграторы 16, 15 и 17 разомкнуты. Первый измеряемый ток tXl(t) через замкнутый ключ I протекает на вход интегратора 14, состоящего из операционного усилителя с емкостной обратной связью. Опорное напряжение U0 через шину 22 и замкнутый ключ

«-Ј

Ip,

(5)

Момент равенства нулю выходного 4Q напряжения интегратора 14 фиксируется компаратором 18 напряжения, который управляет ключами 3-5.

В соответствии с выражением (5) длительность второго такта т«р.1

45

змм

2 поступает через резистор Rg на вход интегратора 15, также состоящего из операционного усилителя с емкостной обратной связью. Напряжение на выходе интегратора 14 к концу пер вого такта TVC|)1HMeeT значение Тцер1

-IJ ixi(t)dt,

и

11

(О

где С - емкость интегратора.

Напряжение на выходе интегратора

15 к концу первого такта имеет зна- ЪР 1 U0dt.(2)

чение

U4iJ

R8C

Выходное напряжение интегратора 15 с помощью преобразователя 13 преобразуется в ток

U о Т уср

р

VJ.P

R9C

(3)

0

5

где J пр - проводимость преобразователя 1 3.

Ток 1р1 через замкнутый ключ 4 и, протекает на общую шину.

На выходе интегратора 7 формируется напряжение U3, пропорциональное длительности Т импульса, открывающего ключ 6,

Т I

V

0

Г ..... UeT ,,. RCC iU dt -RTc W Во втором такте Т,1 производится разряд конденсатора интегратора 14 и заряд конденсатора интегратора 16,

По окончанию импульса тока i.x, (t), подаваемого на шину 12, ключи 1, 2, 4, 6 и интеграторов 16, 15 и 17 разомкнуты, а ключи 3, 5 и 7 замкну-

XI

протекает через шину 12 и замкнутый ключ 7 на общую шину устройства, а опорное напряжение через шину 22 и замкнутый ключ 5 поступает на вход.

ты. При этом измеряемый ток iM(t) интегратора 16. Одновременно выходной ток 1р1 преобразователя 13 через замкнутый ключ 3 протекает на вход интегратора 14 и к концу второго такта Тх напряжение на его выходе равно нулю

«-Ј

Ip,

(5)

Момент равенства нулю выходного напряжения интегратора 14 фиксируется компаратором 18 напряжения, который управляет ключами 3-5.

В соответствии с выражением (5) длительность второго такта т«р.1

„ллЛ.ЬСх

J-. 1С

Tj(1 iVJnpL

змм

„(Odcl-Si

LT cpiij и-.

пр

(6)

т.е, нию

пропорциональна среднему эначе- 1К, с(1 измеряемого тока за выб1 Ct чранный интервал усреднения Т

Напряжение на выходе интегратора 16 к концу второго такта имеет значение

5

U

i

вых i:

JJL.F.

RaJop L P

lyepi

:1

ix,(t)dt

-X Cpl

(7)

и, следовательно, также пропорционально среднему значению измеряемого тока за время усреднения ТуСр,.

Среднее значение тока 1СрП в последовательности п импульсов произвольной формы и длительности определяется выражением

т UJLP.JL-x.-5:J Jlv... J- cf. .+ЛХ..,°,Р ср nn

(8)

При поступлении с сигнальной шины 12 каждого импульса последовательности напряжение на выходе интегратора 17 увеличивается на напряжение U s определяемое выражением (4). Таким образомз

,(9)

где иэ и3п/и., - нормированное напряжение на выходе интегратора 17.

При этом выражение (8) может быть записано в следующем виде:

1 С-р П К

ии,+и«.хг+.

+11 +U еых (n-i) выхп

п

(Ю)

где К

Для исключения погрешности, связанной с насыщением суммирующего уст ройства, определяющего числитель выражения (10), используется рекуррентный способ вычисления среднего тока Iсрп, определяемого выражением

1с

рп

4-Т1

К I n СР(И

п

,(

11)

.

Напряжение с выхода интегратора 16 поступает на второй вход вычита- теля 20. На первый вход вычитателя 20 с выхода блока 9 выборки и хранения поступает напряжение UCp(h.,j , пропорциональное среднему значению

тока cp(«-ir

Аналоговый делитель 21 напряжения

осуществляет деление напряжения с выхода вычитателя 29 на напряжение Uj с выхода интегратора 17.

На сумматоре 10 образуется напряжение

п-и

ивых n utp U-D

п

(12)

При срабатывании компаратора 18 на седьмом выходе 7 блока 11 управления формируется импульс напряжения вых/ во ВРЈМЯ которого напряжение Uepn заносится в блок 8 выборки и

0

5

храненияе из которого во время импульса UEbU8, формируемого в блоке 11 управления по заднему фронту импульса Uettix7 переписывается в блок 9 выборки и хранения.

Блок 11 управления (фиг. 3) работает следукнйнм ебразом. При поступлении с сигнальной шины 12 на первый вход импульса произвольной формы и длительности на выходе компаратора 25 формируется прямоугольный импульс U 8Ь(Х(фиг, 4), длительность которого равна Т уьр „ , Напряжение U оих г поступает на вход элемента НЕ 24, на выходе которого формируется импульс напряжения U6fc . На второй вход блока 11 управления поступает напряжение с выхода компаратора 18, которое складывается по модулю 2 элементом ИСКЛЮЧАЮЩЕЕ ИЛИ 26 с напряжением ых2- В результате на третьем выходе блока 11 управления и на выходе логического элемента НЕ 23 формируется напряжение , при этом на выходе логического элемента НЕ 23 формируется напряжение Uekiv . Длительность импульсов UBt(x2H U Btlx, соответствует времени второго такта

. зо т

X П

5

0

5

0

5

При переходе напряжения ивь,Х1 из I в О запускается одновибратор

28и на его выходе формируется импульс и8ык, длительность Т которого определяется соотношением

,36 RC,(13)

где R - сопротивление резистора; С - емкость конденсатора одновибрато- ра 28.

При переходе напряжения UBX2 из 1 в О запускается одновибратор

29и на его выходе формируется импульс UBklX7, по заднему фронту которого запускается одновибратор 30 и на его выходе формируется импульс

U аьпс а Длительности импульсов U ВИХ1 и Ugt,xe равны Т и определяются соответственно значениями резисторов и конденсаторов, одновибраторов 29 и 30.

Напряжение U сформированное одновибратором 29, поступает на второй вход логического элемента ИЛИ-НЕ 27 9 на первом входе которого находится напряжение U iul. На выходе элемента 27 по окончании импульса Ueb,XT, формируется напряжение U4ux 6, которое поступает на шестой выход блока 1 управления.

Напряжение Ugt()f5., формируемое кнопкой 32, устанавливается перед началом работы устройства на пятом выходе блока 11 управления. Формула изобретения

второй вход которого соединен с выходом третьего интегратора, а выход - с первым входом аналогового делителя, второй вход которого соединен с выходом четвертого интегратора, а вы10

15

20

5

ход - с вторым входом сумматора, вхо; ды обнуления первого и третьего интеграторов соединены с шестым выходом блока управления, выход шестого ключа соединен с входом четвертою интегратора, вход обнуления которого соединен с пятым выходом блока управления, седьмой, восьмой и девятый выхоцы которого соединены соответственно с управляющими входами первого, второго блоков выборки и хранения и шестого ключа, а первый вход - с входной сигнальной шиной, третий вход, кроме того, - с управляющим входом пятого ключа.

0

5

0

0

5

lxff)t

Ј

| Преобразователь переменного напряжения в постоянное | 1976 |

|

SU665273A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения среднего значения тока | 1984 |

|

SU1273823A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1990-03-15—Публикация

1988-02-21—Подача