Изобретение относится к электроизмерениям и может быть использовано для измерений средний значений импульсов произвольной формы и длительности.

Цель изобретейия - повьшение точности измерений путем изменения времени усреднения в соответствии с длительностью усредняемого импульса тока.

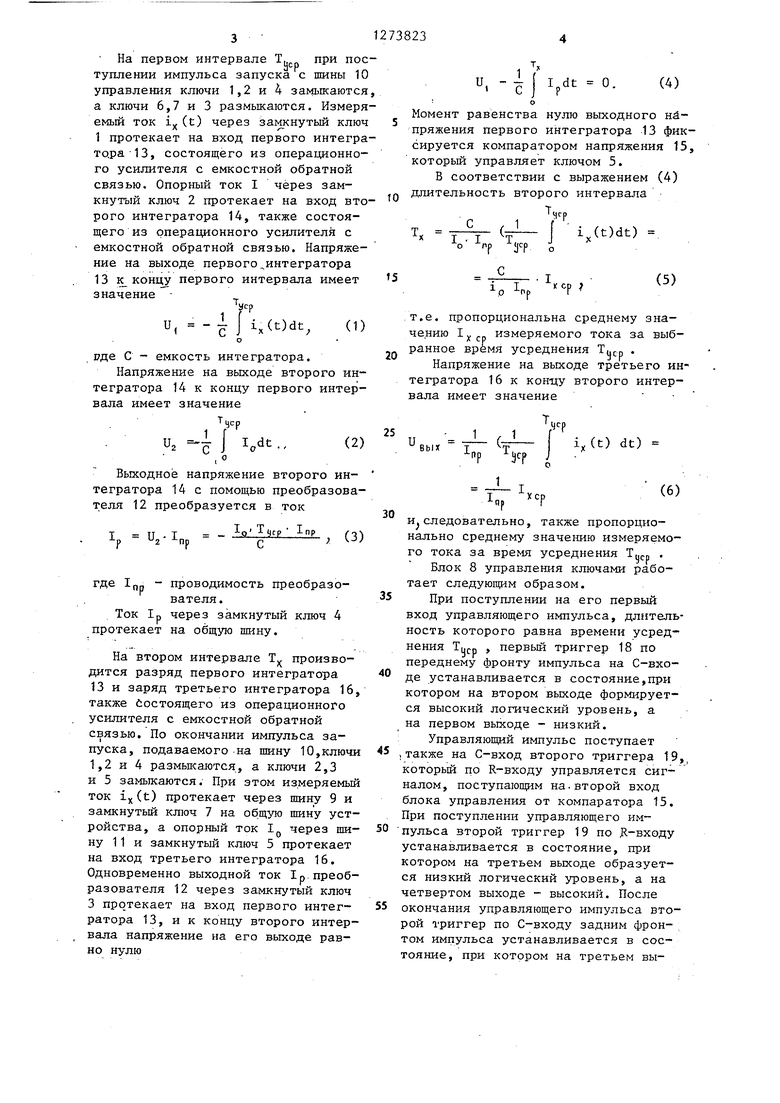

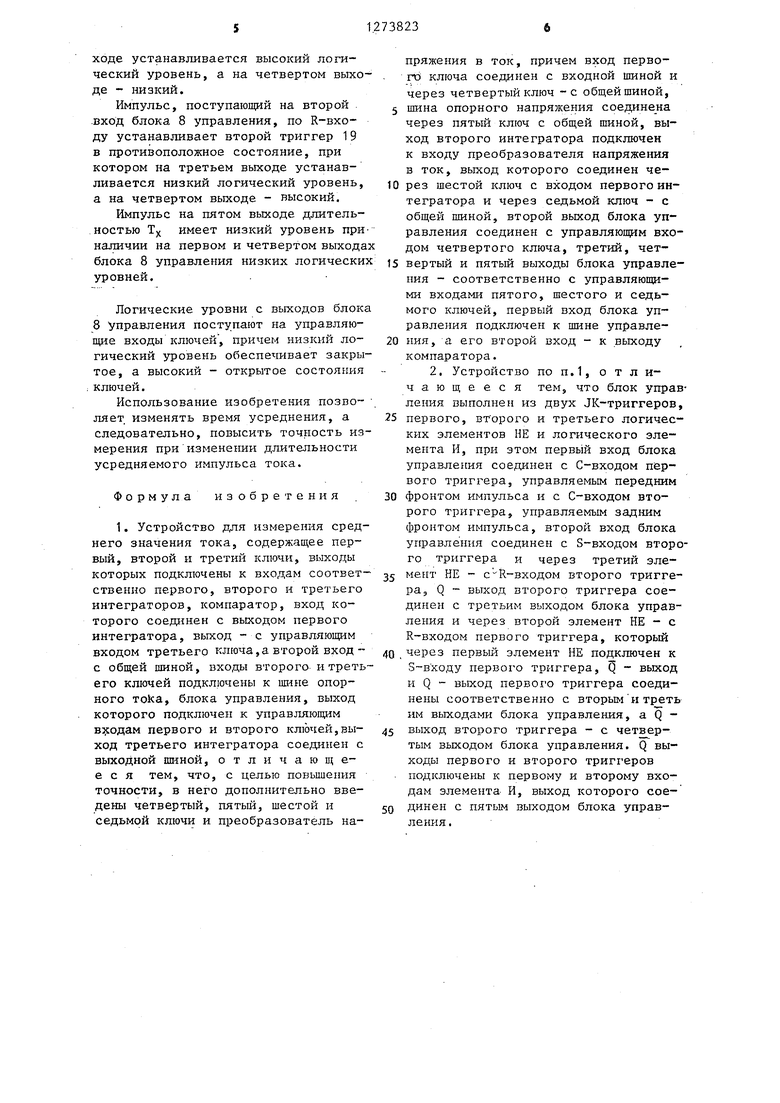

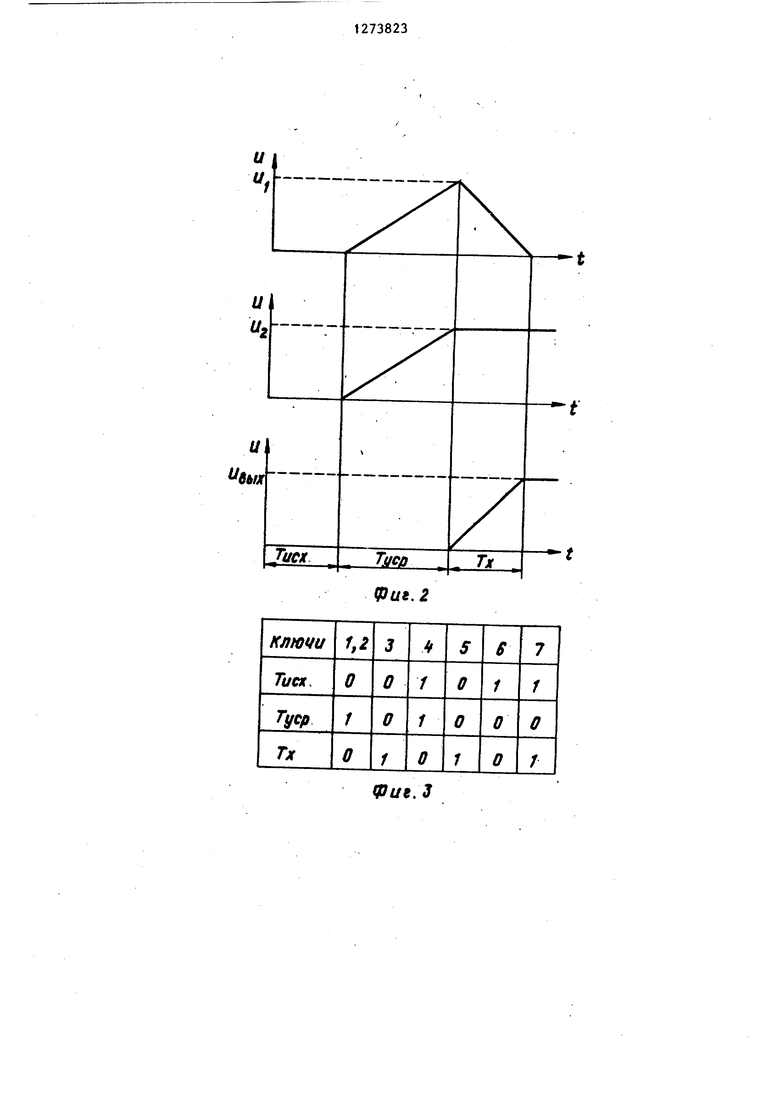

На фиг.1 приведена структурная схема устройства, на фиг.2 - временные диаграммы его работы; на фиг. 3таблица состояния ключей/ на фиг.4электрическая принципиальная схема блока управления.

Устройство для измерения среднего значения тока содержит первый 1, второй 2, третий 3, четвертый 4, пятый 5, шестой 6, седьмой 7 ключи, блок 8 управления, входную сигнальную шину 9, шину 10 управления, шину 11 опорного тока, преобразователь 12, напряжения в ток, первый 13, второй 14 интеграторы, компаратор 15 напряжения, третий интег1)атор 16, выходную шину 17.

Входная сигнальная шина 9 соединена через седьмой ключ 7 с общей шиной, а через первый ключ 1 - с входом второго интегратора 14,выход которого подключен к входу компаратора 15 напряжения. Шина 11 опорного тока подключена через второй ключ 2 к входу первого интегратора 13, через пятый ключ 5 - к входу третьего интегратора 16, выход которого соединен с выходной шиной 17 и через шестой ключ 6 - с общей шиной.

I

Выход первого интегратора 13 соединен с входом преобразователя 12 напряжения в ток, выход которого через третий ключ 3 соединен с входом второго интегратора 14, а через четвертый ключ 4 - с общей шиной. Первый вход блока 8 управления соединен с шиной 10 управления, а его второй вход - с выходом компаратора 15 напряжения и управляющим входом пятого ключа 5. Первый выход блока 8 управления соединен с управляющим входом седьмого ключа 7, второй выход - с управляющими входами первог 1 и второго 2 ключей, третий, четвертый и пятый выходы - соответственно с управляющими входами третьего 3, четвертого 4 и шестого 6 ключей.

Блок 8 управления (фиг.З) содержит первый 18 и второй 19 JK-триггеры, первый 20, второй 21 и третий 22 логические элементы НЕ и логический элемент И 23. Первый вход блока 8 управления соединен с С-вхо-. дом первого триггера 18, управляемым передним фронтом импульса, и с С-входом второго триггера 19, управляемым задним входом импульса. Второй вход блока 8 управления соединен с S-входом второго триггера 19

и через третий элемент НЕ 22 R-входом второго триггера 19, Q выход второго триггера 19 соединен с третьим выходом блока 8 управления и через второй элемент НЕ 21 с R-входом первого триггера 18,ко- торый через первый элемент НЕ 20 подключен к S-входу первого триггера 18, Q-выход и Q-выход первого триггера

18соединены соответственно с первым и вторьм выходами блока 8 управления . Q-выход второго триггера

19соединен с четвертым выходом блока 8 управления, Q-выходы первого

18 и второго 19 триггеров подключены к первому и второму входам элемента И 23, выхрд которого соединен с пятым выходом блока 8 управленияГ

Устройст-во для измерения среднего значения тока работает следующим образом.

В исходном состоянии Т ключи 1,2,3,5 разомкнуты, а ключи 6,7,4 замкнуты. Измеряемый ток ij((t) и опорный ток 1д через входную сигнальную шину 9 и шину 11 опорного тока соответственно и замкнутые ключи 6,7 протекают на общую шину (см, таблицу на фиг. 26, где О - разомкнутое состояние ключей, 1 - замкнутое состояние).

Рабочий цикл устройства начинается, когда через шину управления 10 на первый вход блока 8 управления поступает импульс запуска с длительностью Тур , равной времени усреднения. Полный цикл работы устройства можно разделить на два интервала: интервал Тц(р , в течение которого выполняется интегрирование измеряёмого и опорного токов, и интервал TK, в течение которого вьщеля; ется среднее значение измеряемого тока. На первом интервале Т, при пос туплении импульса запуска с шины 10 управления ключи 1,2 и 4 заь1ыкаются а ключи 6,7 и 3 размыкаются. Измеря емый ток ix(t) через замкнутый ключ 1 протекает на вход первого интегра тара-13, состоящего из операционного усилителя с емкостной обратной связью. Опорный ток I через зам кнутый ключ 2 протекает на вход вто рого интегратора 14, также состоящего из операционного усилителя с емкостной обратной связью. Напряжение на выходе первого,интегратора 13 к концу первого интервала имеет значение , 4

i,,(t)dt (1)

рде С - емкость интегратора.

Напряжение на выходе второго интегратора 14 к концу первого интервала имеет значение

т,.

1 Т

и, - J i,dt

Выходное напряжение второго интегратора 14 с помощью преобразователя 12 преобразуется в ток

IP, Т9ср

- пр

IP U,-Inp

где 1рр - проводимость преобразователя.

Ток IP через замкнутый ключ 4 протекает на общую шину.

На втором интервале Tj производится разряд первого интегратора 13 и заряд третьего интегратора 16, также Состоящего из операционного усилителя с емкостной обратной связью. По окончании импульса запуска, подаваемого на шину 10,ключи 1,2 и 4 размьжаются, а ключи 2,3 и 5 замыкаются. При этом измеряемый ток ix(t) протекает через шину 9 и замкнутый ключ 7 на общую шину устройства, а опорный ток I(j через шину 11 и замкнутый ключ 5 протекает на вход третьего интегратора 16. Одновременно выходной ток 1р.преобразователя 12 через замкнутый ключ 3 протекает на вход первого интегратора 13, и к концу второго интервала напряжение на его выходе равно нулю

т.е. пропорциональна среднему значению I)( cp измеряемого тока за выбранное время усреднения .

Напряжение на выходе третьего интегратора 16 к кон-цу второго интервала имеет значение

Т

(.

i(t) dt)

вык

rtp ijjcp

1 ,

(6)

Хс

Р

пр

и.следовательно, также пропорционально среднему значеютш измеряемого тока за время усреднения .

Блок 8 управления ключами работает следующим образом. 5 При поступлении на его первый

вход управляющего импульса, длительность которого равна времени усреднения Тц.р , первый триггер 18 по переднему фронту импульса на С-вхо де устанавливается в состояние,при котором на втором выходе формируется высокий логический уровень, а на первом выходе - низкий.

Управляющий импульс поступает 5 .также на С-вход второго триггера 19,, который цо R-входу управляется сигналом, поступающим на-второй вход блока управления от компаратора 15. При поступлении управляющего им0 пульса второй триггер 19 по Д-входу устанавливается в состояние, при котором на третьем выходе образуется низкий логический уровень, а на четвертом выходе - высокий. После окончания управляющего импульса второй триггер по С-входу задним фронтом импульса устанавливается в состояние, при котором на третьем вы,-М Ipdt 0. Момент равенства нулю выходного напряжения первого интегратора 13 фиксируется компаратором напряжения 15, который управляет ключом 5. В соответствии с выражением (4) длительность второго интервала . rV (fi- f s) о c I i. In.

ходе устанавливается высокий логический уровень, а на четвертом выходе - низкий.

Импульс, поступающий на второй . -ВХОД блока 8 управления, по R-BXOду устанавливает второй триггер 19 в противоположное состояние, при котором на третьем выходе устанавливается низкий логический уровень, а на четвертом выходе - высокий.

Импульс на пятом выходе длительностью Т)( имеет низкий уровень приналичии на первом и четвертом выхода блока 8 управления низких логически уровней.

Логические уровни с выходов блок 8 управления поступают на управляющие входы ключей, причем низкий логический уровень обеспечивает закрытое, а высокий - открытое состояния ;ключей.

Использование изобретения позволяет, изменять время усреднения, а следовательно, повысить точность измерения приизменении длительности усредняемого импульса тока.

Формула изобретения

1. Устройство для измерения среднего значения тока, содержащее первый, второй и третий ключи, выходы которых подключены к входам соответственно первого, второго и третьего интеграторов, компаратор, вход которого соединен с выходом первого интегратора, выход - с управляющим входом третьего ключа,а второй входс общей шиной, входы второго и третьего ключей подключены к ш-1не опорного Toka, блока управления, выход которого подключен к управляющим входам первого и второго ключей,выход третьего интегратора соединен с выходной пленой, отличающееся тем, что, с целью повьшения точности, в него дополнительно введены четвертый, пятьш, шестой и седьмой ключи и преобразователь напряжения в ток, причем вход первого ключа соединен с входной шиной и через четвертый ключ -с общей шиной, шина опорного напряжения соединенна через пятый ключ с общей шиной, выход второго интегратора подключен к входу преобразователя напряжения в ток, выход которого соединен через шестой ключ с входом первого интегратора и через седьмой ключ - с общей шиной, второй выход блока управления соединен с управляющим входом четвертого ключа, третий, четвертый и пятый выходы блока управления - соответственно с управляющими входами пятого, шестого и седьмого ключей, первый вход блока управления подключен к шине управления, а его второй вход - к выходу компаратора.

2. Устройство по П.1, о т л ичаюш, ееся тем, что блок управления выполнен из двух JK-триггеров,

первого, второго и третьего логических элементов НЕ и логического элемента И, при зтом первый вход блока управления соединен с С-входом первого триггера, управляемым передним

фронтом импульса и с С-входом второго триггера, управляемым задним фронтом импульса, второй вход блока угфавления соединен с S-входом второго триггера и через третий злеMefiT НЕ - c-R-входом второго триггера, Q выход второго триггера соединен с третьим выходом блока управления и через второй элемент НЕ - с R-входом первого триггера, который

через первый элемент НЕ подключен к 5 входу первого триггера, Q - выход и Q - выход первого триггера соединены соответственно с вторым и треть им выходами блока управления, а Q выход второго триггера - с четвертым выходом блока управления. Q выходы первого и второго триггеров подключены к первому и второму входам элемента И, выход которого сое-

динен с пятым выходом блока управления .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения среднего значения тока | 1988 |

|

SU1550432A1 |

| Устройство измерения отклонения сопротивления от заданного значения | 1990 |

|

SU1737360A1 |

| Измеритель длительности импульсов | 1990 |

|

SU1714535A1 |

| Аналого-цифровой преобразователь интегральных характеристик напряжений | 1984 |

|

SU1233283A1 |

| Способ измерения среднего значения напряжения произвольной формы и устройство для его осуществления | 1983 |

|

SU1150561A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1989 |

|

SU1695503A1 |

| ИСТОЧНИК ПОСТОЯННОГО ТОКА | 2005 |

|

RU2313121C2 |

| Интегратор | 1988 |

|

SU1728871A1 |

| Множительно-делительное устройство | 1977 |

|

SU696444A1 |

| Аналого-цифровой преобразователь совмещенного интегрирования | 1991 |

|

SU1785075A1 |

Изобретение относится к области электроизмерений. Может быть использовано для измерений средних BJ(OS Вх.1 значений импульсов произвольной формы и длительности. Цель изобретения - повышение точности измерений. ;Для этого в устройство, содбржащее ключи 1, 2, 3, интеграторы 13,14,16j компаратор 15, шину 11 опорного тока, блок управления 8, выходную шину 17, введены ключи 4,5,6,7,преобразователь 12 напряжения в ток.Блок 8 управления содержит два JK-триггера, три логических элемента НЕ,логический элемент И. В материалах изобретения приведена электрическая принципиальная схема блока управления. Устройство позволяет изменять Ш время усреднения в соответствии с длительностью усредняемого импуль,са тока, а следовательно, повысить точность измерения. 1 з.п. ф-лы. 4 ил. ю 00 00 ю

fpue. J

фиг. Ч

| Устройство для преобразования переменного напряжения в постоянное | 1972 |

|

SU473958A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-11-30—Публикация

1984-12-27—Подача