Уср

сл ел

к

аз

а

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вибрационных испытаний лентопротяжных механизмов кассетных магнитофонов | 1991 |

|

SU1770981A1 |

| Адаптивное устройство измерения частоты | 1990 |

|

SU1812516A1 |

| СВЧ СИНТЕЗАТОР ЧАСТОТ | 2015 |

|

RU2580068C1 |

| Устройство демодуляции телевизионного сигнала системы Секам | 1989 |

|

SU1688458A1 |

| Устройство для измерения температуры (его варианты) | 1983 |

|

SU1151834A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1984 |

|

SU1216834A1 |

| Цифровой формирователь частотно-модулированных сигналов с низким уровнем искажений | 2021 |

|

RU2765273C1 |

| Устройство для выделения @ -зубца электрокардиосигнала | 1985 |

|

SU1297797A1 |

| Генератор пилообразного напряжения | 1978 |

|

SU783965A1 |

| Стабилизатор переменного напряжения | 1988 |

|

SU1534434A1 |

Изобретение может быть использовано в системах обработки и приема информации с фазовым ее представлением. Цель - повышение быстродействия-достигается введением в импульсно-фазовый детектор ключа 7, конденсатора 8, дифференциального усилителя 9, компараторов 10, 11 напряжения, Д-триггеров 12, 13, шин положительного 17 и отрицательного 18 опорных напряжений, источника 14 тока, элемента 15 отвода тока, интегратора 16 и ждущего мультивибратора 6. Импульсно-фазовый детектор содержит также генератор 1 линейно изменяющегося напряжения, ключ 2, выходной усилитель 4, конденсатор 3 и формирователь 5 импульсов. 2 ил.

™А

Изобретение относится к импульсной технике и может быть использовано в системах обработки и приема информации с фазовым ее представлением, а также в системах фазовой автоподстройки частоты.

Цель изобретения - повышение быстродействия устройства.

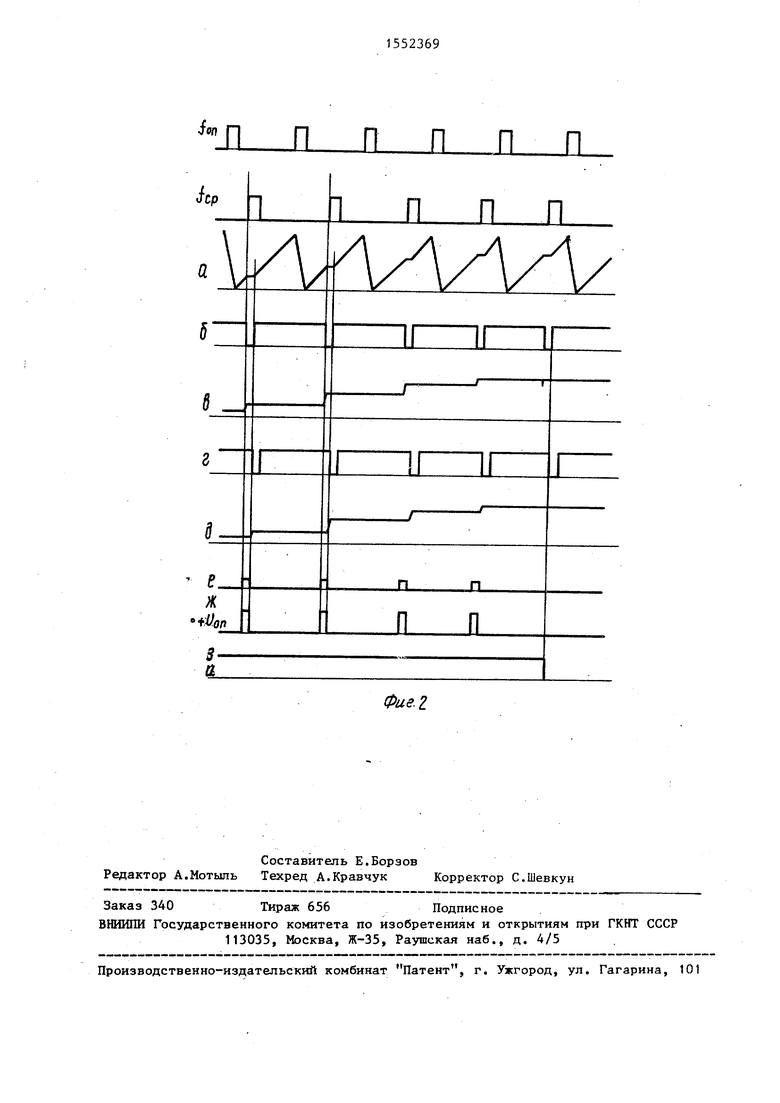

На фиг.1 приведена функциональная схема импульсно-фазового детектора; на фиг.2 - временные диаграммы его работы.

«.Импульсно-фазовый детектор содержит генератор 1 линейно изменяющегося напряжения, ключ 2, конденсатор 3, выходной усилитель 4, формирователь 5 импульсов, ждущий мультивибратор 6, ключ 7, конденсатор 8, дифференциальный усилитель 9, компараторы 10 и 11 напряжений, D-триг- геры 12 и 13, источник 14 тока,элемент 15 отвода тока, интегратор 16, шину 17 положительного опорного напряжения, шину 18 отрицательного опорного ьапряжения. При этом последовательно соединены генератор 1 линейно изменяющегося напряжения, ключ 2 и выходной усилитель 4, вход которого соединен через конденсатор 3 с общей шиной, а выход - с первым входом-интегратора 16, входом ключа

Iи первым входом дифференциального усилителя 9, второй вход которого соединен с выходом ключа 7 и через конденсатор 8 с общей шиной, а выход с первыми входами компараторов 10 и

IIнапряжений, вторые входы которых соединены соответственно с шиной 17 положительного опорного напряжения и шиной 18 отрицательного опорного напряжения, а выходы - с информационными входами соответственно D- триггеров 12 и 13, тактовые входы которых соединены с выходом формирователя 5 импульсов, управляющими входами генератора 1 линейно изменяющегося напряжения, ключа 2 и входом ждущего мультивибратора 6, а выход - соответственно с входами источника

14 тока и элемента 15 отвода тока, выходы которых подключены к второму входу интегратора 16, выход которого соединен с выходной шиной устройства, а входы генератора 1 линейно изменяющегося напряжения и формирователя 5 импульсов соединены соответственно с шинами опорной и сравниваемой частот, причем выход

ждущего мультивибратора 6 соединен с управляющим входом ключа 7.

Ключи 2 и 7 могут быть выполнены, например, на интегральных микросхемах типа 590КН5, ждущий мультивибратор - на микросхеме 155АГЗ, включенной так, чтобы он срабатывал от положительного перепада, а на выQ ходе формировался отрицательный

от высокого уровня импульс. Выходной 4 и дифференциальный 9 усилители могут быть выполнены на микросхемах 544 и 574 серий с полевыми транзисторами

5 на входах для уменьшения разряда конденсаторов 3, 8 между импульсами. Компараторы 10 и 11 напряжений могут быть выполнены на микросхемах 521 САЗ, а D-триггеры 12 и 13 - на микросхе0 мах 155ТМ2.

Кроме того, источник 14 тока может быть выполнен, например,в виде стабилизатора вытекащего тока на транзисторе и резисторах, управля5 емого от логического перепада транзисторно-транзисторной логики, а элемент 15 отвода тока - в виде стабилизатора втекающего тока, та же управляемого, как и источник 14 тока.

n Эти элементы могут быть выполнены и на микросхемах 170 серии. Интегратор 16 может быть выполнен в простейшем случае из соединенных последовательно трех резисторов и конденсатора, включенных между его первым входом и общей шиной, при этом объединенные выходы первого и второго резисторов подключены к выходу интегратора 16, а объединенные выводы

второго и третьего резисторов - к

0

его второму входу, причем для величин сопротивлений резисторов должно выполняться условие R,, Rj,, R. Формирователь 5 импульсов формирует

5 импульс стабильной длительности по каждому импульсу сравниваемой частоты и может быть выполнен так же, как и ждущий мультивибратор 6. Генератор 1 линейно изменяющегося напряжения может быть выполнен по любой известной схеме при соблюдении двух условий: импульсом опорной частоты выходное напряжение генератора устанавливается равным нулю, а импульсом сравниваемой частоты фиксируется на достигнутом к этому мр- менту уровне.

Импульсно-фазовый детектор работает следующим образом.

5

0

5

5

Пусть сравниваемая частота fcp ниже опорной частоты Г0 , При постулении на вход генератора 1 импульса опорной частоты его выходное напряжение устанавливается на начаиь- ном уровне, а после окончания импулса fon формируется линейно изменяющееся пилообразное напряжение (фиг.2а). При поступлении импульса частоты сравнения fcp на вход формирователя 5 импульсов на его выходе формируются коммутационные сигналы (фиг.2б) соответственной длительности, которые фиксируют напряжение генератора 1 и замыкают ключ 2, после чего накопительный конденсатор

3заряжается до уровня,присутствующего на выходе генератора 1 (фиг.2г). Напряжение на выходе ключа 2 и на выходе выходного усилителя

4соответствует уровню напряжения генератора 1, который остается постоянным до поступления следующего импульса fср .

Предположим, что исходный уровень напряжения на накопительном конденсаторе 8 (фиг.2д) ниже уровня напряжения на выходе выходного усилителя 4. Вследствие этого напряжение на выходе дифференциально- гс усилителя 9 во время действия импульса, поступающего с выхода формирователя 5 импульсов, равняется разнице между исходным уровнем напряжения на конденсаторе 8 и уровнем напряжения на выходе выходного усилителя 4 (фиг.2г), которая поступает на компараторы 10 и 11 напряжений, где сравниваются с опорными напряжениями -HJon и -Uofl . При исходном напряжении на конденсаторе 8 меньшем, чем напряжение на выходе выходного усилителя 4, выходное напряжение дифференциального усилителя 9 положительное (фиг.Зж) и превышает уровень срабатывания компаратора 10 напряжения. Вследствие этого на выходе компаратора 10 появляется импульс логической 1, который положительны перепадом импульса, поступающего от формирователя 5 импульсов, переписывает логическую 1, присутствующую на информационном входе первого D- триггера 12 на его выход, и тем самым включает источник 14 тока. Импульс с выхода формирователя 5 импульсов своим отрицательным перепа523696

дом также запускает ждущий мультп .иб ратор 6, после чего на его нмходе формируется отрицательный логический импульс (фиг.2в), который поступает на управ шющин вход ключа 7 и замыкает его. Накопительный конденсатор 8 заряжается до уровня напряжения, присутствующего на информационном

Ю входе ключа 7, который подкпючен к выходу выходного усилителя 4 (фиг.2д), после чего напряжение на выходе дифференциального усилителя 9 становится равным нулю. Напряжение с вы- i

15 хода выходного усилнтепя 4 и ток источника 14 тока воздействуют на интегратор 16. Напряжение с выхода интегратора 16 поступает на управляющий вход генератора, управляемо20 го напряжением (ГУН), работающего в кольце СИСТРМЫ ФАЛЧ, и изменяет его частоту в сторону повышения.

При поступлении следующего импульса ЈСр цикл работы устройства

25 повторяется, только накопительный конденсатор 3 заряжается до нового уровня, который больше по сравнению с предыдущим, а напряжение на выходе интегратора 16 еще больше уве40 личивается и воздействует на ГУН, увеличивая его частоту, тем самым уменьшая частотное и фазовое рассогласование. Как видно из фиг.2, ускоряющее действие источника 14 то

35 ка продолжается до тех пор, пока напряжение на выходе дифференциального усилителя 9 во время действия импульса, поступающего от формирователя 5 импульсов,станет меньше

40 уровня +Uon срабатывания компаратора 10, после чего источник тока отключается и на входе интегратора 16 действует только напряжение с выхода выходного усилителя 4. Значение раз45 ности фаз между fot7 и Јс„ , до которого продолжается непрерывное действие ускоряющего источника 14 тока, можно определить по формуле

50

,

5

где п

иВых и„

размах выходного напряжения генератора 1; уровень срабатывания компараторов 10 и 11 напряжений .

Когда частота сравнения Јср выше опорной частоты fon , устройство работает так же, только на выходе дифференциального усилителя 9 присутствует отрицательное напряжение (напряжения на фиг.Зг, д имеют спадающий характер), которое сравнивается компаратором 11 напряжения с опорным напряжением - и через D-триг гер 13 включает элемент 15 отвода тока, выходной ток которого имеет отрицательную полярность и уменьшает напряжение на выходе интегратора 16, тем самым уменьшая частоту ГУН, работающего в замкнутом кольце системы ФАПЧ. Непрерывное ускоряющее действие элемента 15 отвода тока продолжается до тех пор, пока уровень напряжения на выходе дифференциального усилителя 9 (во время действия импульса от формирователя импульсов) станет меньше опорного напряжения, после чего элемент 15 отвода тока отключается и на интегратор 16 воздействует только выходное напряжение усилителя 4. Для уменьшения разряда конденсатора интегратора 16 входное сопротивление устройств,подключаемых к его выходу, например ГУН, должно быть достаточно высоким. Разряду этого конденсатора через выходное сопротивление усилителя 4 препятствует большая величина сопротивления R4 в интеграторе 16. Для устойчивой работы устройства элементы в интеграторе 16 должны быть подобраны так, чтобы за период опорной частоты разность фаз между опорной и сравниваемой частотами, возникающая из-за саморазряда конденсатора в интеграторе 16, не превышала значений АЦ1 .

Таким образом, введение в им- пульсно-фазовый детектор новых элементов и связей позволяет увеличить его быстродействие за счет формированного заряда или разряда конденсатора в выходном интеграторе устройства, тем самым повысить крутизну выходной характеристики детектора, что особенно важно при его работе в

системах фазовой автоподстройки частоты.

Формула изобретения

ь

Импульсно-фазовый детектор, содержащий соединенные последовательно генератор линейно изменяющегося напряжения, первый ключ и выходной усилитель, вход которого через первый конденсатор соединен с общей шиной, и формирователь импульсов, вход кото5 рого соединен с шиной сравниваемой частоты, а выход - с управляющими входами первого ключа и генератора линейно изменяющегося напряжения, вход которого соединен с шиной опоро ной частоты, отличающийся тем, что, с целью повышения быстродействия, в него дополнительно введены вторые ключ и конденсатор, диффе- ренциальный усилитель, два компара5 тора напряжения, два D-триггера, шины положительного и отрицательного опорных напряжений, источник тока и элемент отвода тока, интегратор и ждущий мультивибратор, вход которого

0 соединен с выхдом формирователя импульсов и тактовыми входами D-триг- геров, а выход - с управляющим входом второго ключа, вход которого соединен с выходом выходного усилитее ля, первым входом интегратора и первым входом дифференциального усилителя, второй вход которого соединен с выходом ключа и через второй конденсатор с общей шиной, а выход - с

0 первыми входами первого и второго

компараторов напряжений, вторые входы которых соединены соответственно с шинами положительного и отрицательного опорных напряжений, а выходы 5 с информационными входами первого и второго D-триггеров соответственно, входы которых соединены соответственно с входами источника тока и элемента отвода тока, выходы котоg рых подключены к второму входу интегратора, выход которого соединен с выходной шиной устройства.

Son

П П П П П П

hp

1

1

а 5

Ј я +#«

и.

Л П П

I I

п

пп

Фае. 2

| Демодулятор сигналов с фазовоимпульсной модуляцией | 1983 |

|

SU1137576A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Импульсно-фазовый детектор | 1976 |

|

SU610293A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-03-23—Публикация

1987-04-27—Подача