Изобретение относится к области телевидения и может быть использовано в сверхбольших интегральных схемах обработки сигнала цветности системы Секам.

Целью изобретения является уменьшение времени переходного процесса при демодуляции сигнала системы Секам в моменты передачи защитных пакетов частот демодулированных поднес/щи х при одновременном увеличении ю мости и стабильности демодуляции.

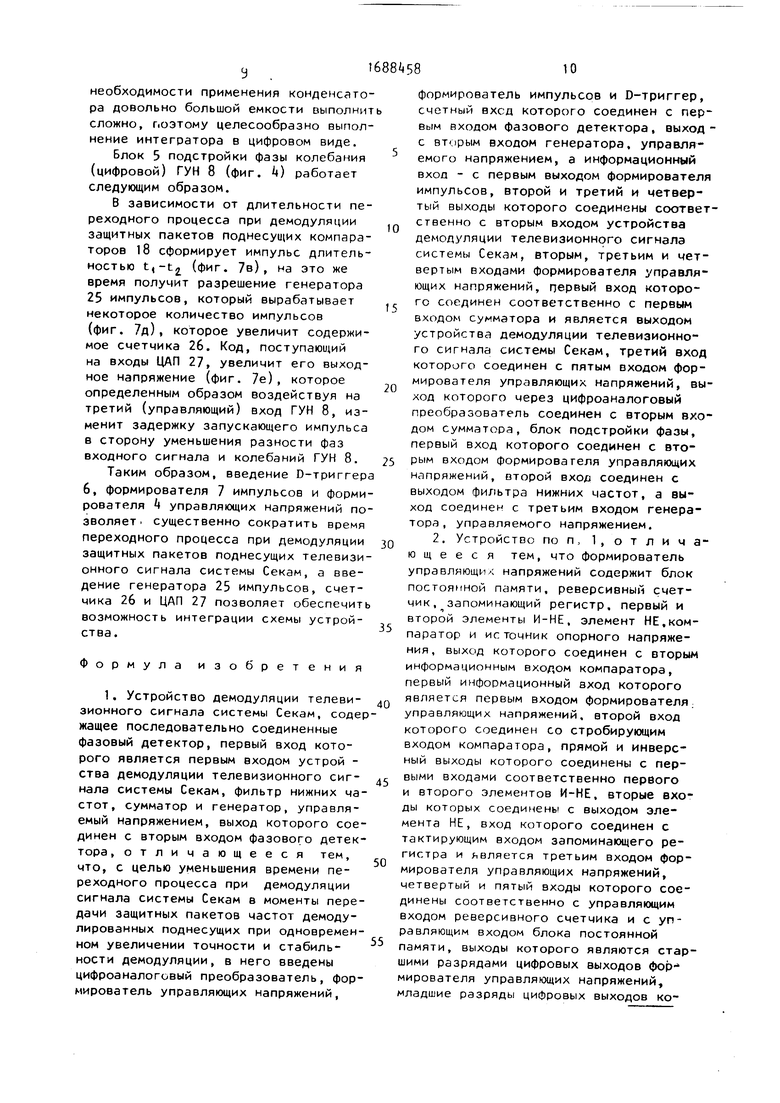

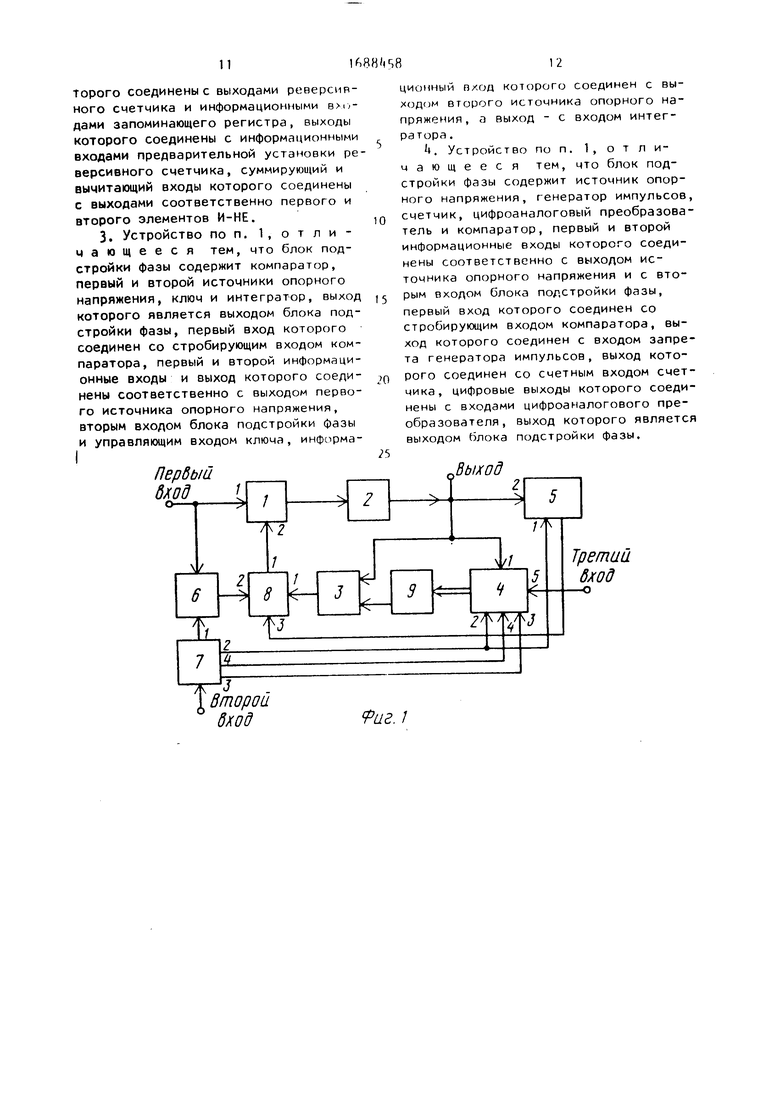

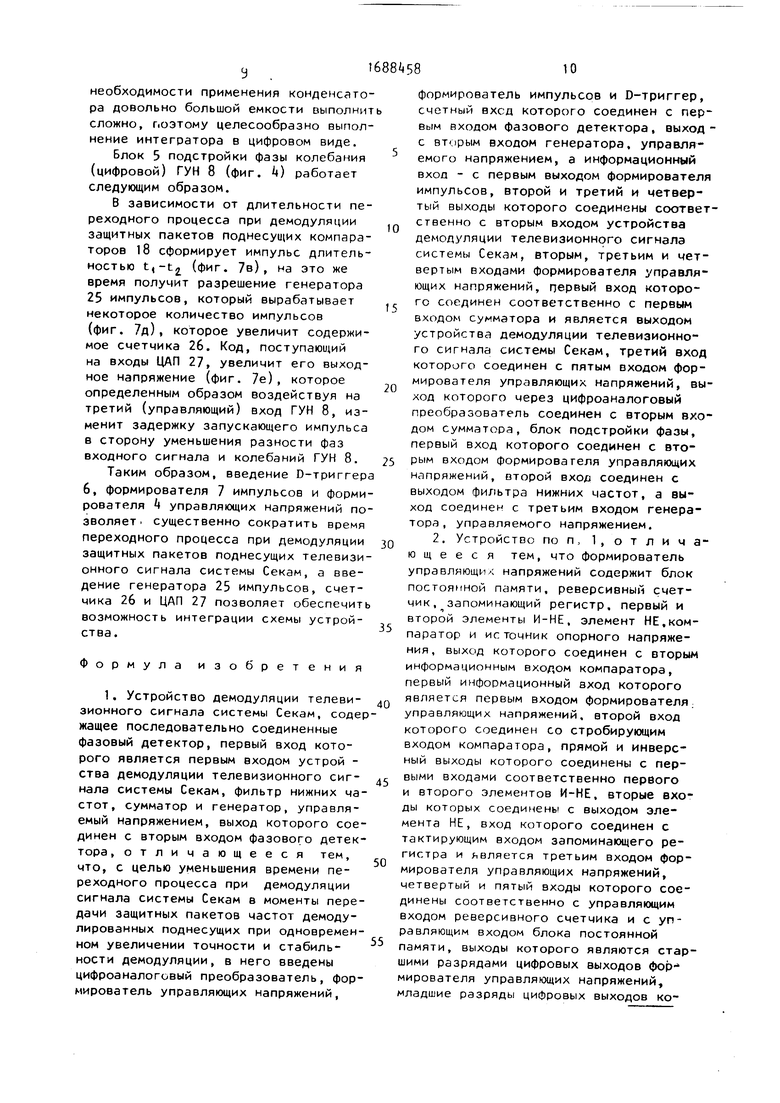

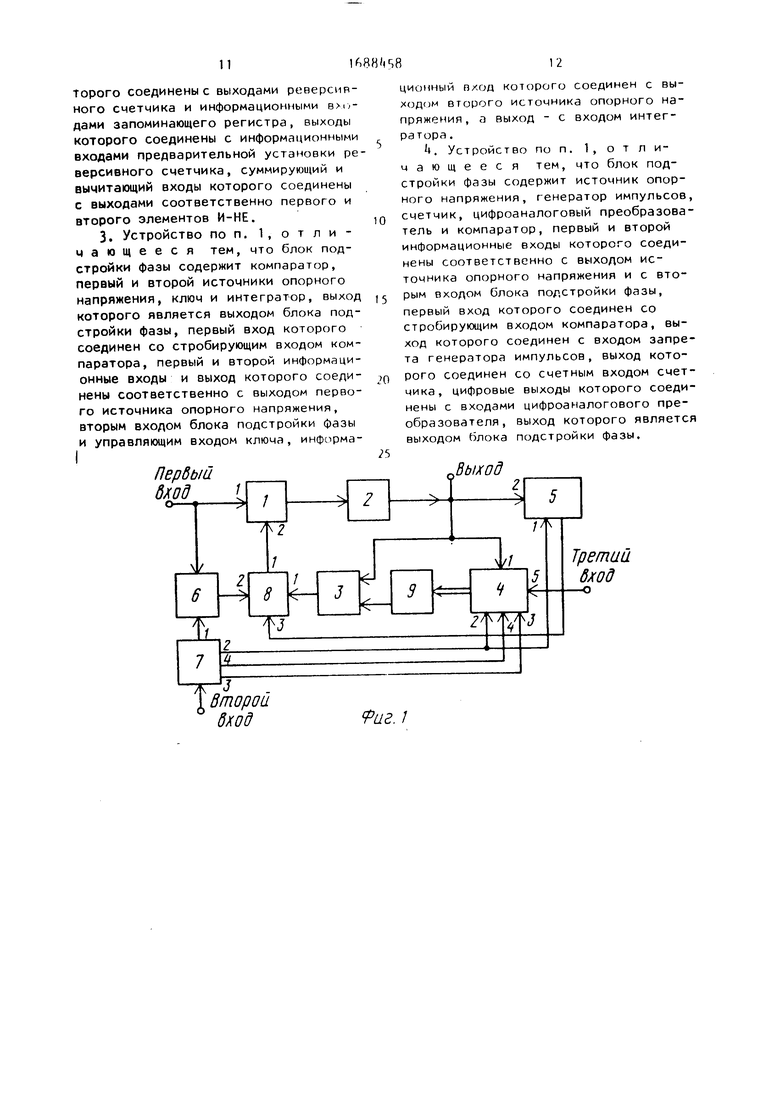

На фиг. 1 представлена структурно; схема устройства демодуляции телевизионного сигнала системы Секам; на фиг. 2 - схема формирователя управляющих напряжений; на фиг. 3 - схема блока подстройки фазы (первый вариант); на фиг. Ц - схема блока подстройки фазы (второй вариант); на фиг. 5, 6 - диаграммы, иллюстрирующие работу устройства демодуляции телевизионного сигнала системы Секам; на фиг. 7 - диаграммы, иллюстрирующие работу блока подстройки фазы.

Устройство демодуляции телевизионного сигнала системы Секам (фиг. 1) содержит фазовый детектор 1, выход

0

оо

00 4- СЛ

00

которого соединен с входом фильтра 2 нижних частот. Выход фильтра 2 нижни частот соединен с первыми входами сумматора 3 и формирователя k управляющих напряжений, вторым входом блока 5 подстройки фазы и является выходом устройства. Сигнал с первого входа устройства поступает также на счетный вход D-триггера 6. С второго входа устройства сигнал SSC поступает на вход формирователя 7 импульсов, первый вход которого соединен с информацонным входом D-триггера 6, выход D- триггера 6 соединен с вторым входом генератора управляемого напряжения (ГУН) 8, выход которого соединен с вторым входом фазового детектора 1, второй выход формирователя 6 импуль

5

компаратора 13, прямой и инверсный выходы которого соединены с первыми входами соответственно первого и второго элементов И-НЕ 15 и 16. Вторые входы элементов И-НЕ 15 и 16 соединены с выходом элемента НЕ 17, а выходы соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика 11. Третий вход формирователя k соединен с входом элемента НЕ 17 и тактирующим входом запоминающего регистра 12.

Блок 15 подстройки фазы (фиг.З) (первый вариант) содержит компаратор 18, стробирующий вход которого является первым входом блока 5, выход компаратора 18 соединен с управляющим входом ключа 19, информационный

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь цветоразностных сигналов декодирующего устройства СЕКАМ | 1986 |

|

SU1345378A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ПЕРСОНАЛЬНОГО КОМПЬЮТЕРА С ТЕЛЕВИЗИОННЫМ ПРИЕМНИКОМ | 1992 |

|

RU2039373C1 |

| ТЕЛЕВИЗИОННЫЙ СПОСОБ ОБНАРУЖЕНИЯ ПОДВИЖНЫХ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2011 |

|

RU2451419C1 |

| Цифровой телевизионный приемник | 1983 |

|

SU1321384A3 |

| Устройство формирования цветоразностных сигналов телевизионного приеника СЕКАМ | 1988 |

|

SU1732497A1 |

| УСТРОЙСТВО ВОСПРОИЗВЕДЕНИЯ СИГНАЛА ЦВЕТНОСТИ В ТЕЛЕВИЗИОННОМ СИГНАЛЕ | 2000 |

|

RU2216877C2 |

| Цифровой корректор временных искажений телевизионных сигналов системы СЕКАМ для видеомагнитофонов | 1984 |

|

SU1277428A1 |

| Устройство автоматической стабилизации амплитуды видеосигнала | 1990 |

|

SU1757124A1 |

| Способ цифрового управления многофазным инвертором | 1989 |

|

SU1683154A1 |

| Цифровой синтезатор частоты с частотной модуляцией | 1989 |

|

SU1771068A1 |

Изобретение относится к телевидению. Цель изобретения - уменьшение времени переходного процесса при демодуляции сигнала системы Секам в моменты передачи защитных пакетов частот демодулированных п од f-з сущих при одновременном увеличении точности и стабильности демодуляции. Устройство демодуляции телевизионного сигнала системы Секам содержит фазовый детек1 гор 1. фильтр 2 нижних частот, сумматор 3, формирователь 4 управляющих напряжений, блок 5 подстройки фазы, D-триггер 6, формирователь 7 импульсов, генератор управляемого напряжения (ГУН) 8, цифроаналоговый преобразователь 9. Синхронный запуск ГУН 8 и формирование ступенцатого напряжения на его управляющем входе, сдвигающего на нужный уровень выходное напряжение устройства сокращает время переходного процесса до минимума, которое равно времени установления выходного напряжения ГУН 8 после его повторного запуска. Введение D-триг- гера„6, формирователей 7, 4 позволяет сократить время переходного процесса при демодуляции защитных пакетов поднесущих телевизионного сигнала. Устройство по п. 2, 3, 4 отличается выполнением соответственно формирователя 4, блока 5, и блока 5 (второй вариант). 3 з.п. ф-лы, 7 ил. СЛ

сов соединен с вторым входом формиро- 2„ вход которого соединен с выходом вто30

вателя k управляющих импульсов и первым входом блока 5 подстройки фазы, выход блока 5 подстройки фазы соединен с третьим входом ГУН 8, первый вход которого соединен с выходом сум- 25 матора 3, третий и четвертый выходы формирователя 7 импульсов соединены соответственно с третьим и четвертым входами формирователя управляющих напряжений. Выходы формирователя Ц управляющих напряжений через ЦАП 9 соединены с вторым входом сумматора 3. С третьего входа устройства сигнал цветовой синхронизации (СЦС) поступает на плтый вход формирователя управляющих напряжений.

Формирователь k управляющих напряжений (фиг. 2) содержит блок 10 постоянной памяти-, управляющий вход которого является пятым входом формирователя k. Выходы блока 10 постоянной памяти являются старшими разрядами цифровых выходов формирователя k, младшие разряды цифровых выходов которого соединены с выходами реверсивного счетчика 11 и информационными входами запоминающего регистра 12С Выходы запоминающего регистра 12 соединены с информационными входами предварительной установки реверсивного счетчика 11, вход разрешения предварительной установки которого является четвертым входом формирователя 1. Первый и второй входы формирователя k соединены соответственно с первым информационным и стробиру- ющим входами компаратора 13. Выход источника 1 опорного напряжения соединен с вторым информационным входом

рого источника 20 опорного напряжения. Выход первого источника 21 опор- ного напряжения соединен с первым информационным входом компаратора 18, второй информационный вход которого является вторым входом блока 5. Выход ключа 19 соединен с входом интегратора 22, выход которого является выходом блока 5.

Ьлок 5 подстройки фазы (фиг. М (второй вариант) содержит компаратор 23, стробирующий вход которого является первым входом блока 5. Источник 2k опорного напряжения соединен с первым информационным входом компара- 35 тора 23, второй информационный вход которого является вторым входом блока 5 г Выход компаратора 23 соединен с входом запрета генератора 25 импульсов. Выход генератора 25 импульсов соединен со счетным входом счетчика 26, Цифровые выходы счетчика 26 соединены с входами ЦАП 27, выход которого является выходом блока 5.

Устройство демодуляции телевизионного сигнала системы Секам работает следующим образом.

Усиленный и ограниченный по уровню сигнал системы Секам поступает с первого входа устройства на первый вход фазового детектора 1 и счетный вход D-триггера 6, на второй вход фазового детектора 1 поступает сигнал с выхода первого ГУН 8. При этом на выходе фазового детектора 1 появляется напряжение, величина которого пропорциональна разности фаз сходного сигнала и сигнала ГУН 8. Демоду- лированное напряжение через ФНЧ 2

40

45

50

5S

„ вход которого соединен с выходом вто0

5

рого источника 20 опорного напряжения. Выход первого источника 21 опор- ного напряжения соединен с первым информационным входом компаратора 18, второй информационный вход которого является вторым входом блока 5. Выход ключа 19 соединен с входом интегратора 22, выход которого является выходом блока 5.

Ьлок 5 подстройки фазы (фиг. М (второй вариант) содержит компаратор 23, стробирующий вход которого является первым входом блока 5. Источник 2k опорного напряжения соединен с первым информационным входом компара- 5 тора 23, второй информационный вход которого является вторым входом блока 5 г Выход компаратора 23 соединен с входом запрета генератора 25 импульсов. Выход генератора 25 импульсов соединен со счетным входом счетчика 26, Цифровые выходы счетчика 26 соединены с входами ЦАП 27, выход которого является выходом блока 5.

Устройство демодуляции телевизионного сигнала системы Секам работает следующим образом.

Усиленный и ограниченный по уровню сигнал системы Секам поступает с первого входа устройства на первый вход фазового детектора 1 и счетный вход D-триггера 6, на второй вход фазового детектора 1 поступает сигнал с выхода первого ГУН 8. При этом на выходе фазового детектора 1 появляется напряжение, величина которого пропорциональна разности фаз сходного сигнала и сигнала ГУН 8. Демоду- лированное напряжение через ФНЧ 2

0

5

0

S

поступает на выход устройство, а также на второй информационный вход компаратора 18 (второй вход блока 5 подстройки фазы). Первые входы сумматора 3 и фоомирователя Ц управляющих напряжений.

Во время прихода строчного импульса сигнал на первом входе фазового детектора 1 отсутствует, обратная связь через систему ФАПЧ разрывается и ГУН 8 вырабатывает колебания с частотой, соответствующей нулевой настройке ГУН 8 (момент времени t{ фиг. 5). В этот же момент на информа ционный вход D-триггера 6 поступает с уровнем Лог. 1, выделяемый формирователем 7 импульсов из трехуровневого строчного импульса (SSC), поступающего с второго входа устройства. Длительность этого сигнала сотавляет около 6 мкс и является достаточной, чтобы окончание сигнала совпало с приходом первых нескольких колебаний пакета поднесущей (момент времени Ц фиг. 5а,б,в). Сигнал с уровнем Лог. 1 переписывается с информационного входа D-триггера 6 на его выход по первому положительному фронту на его счетном входе, напри мер в момент времени t2 (фиг. 5,г), соответствующий переднему фронту строчного синхроимпульса, начиная с момента времени t ГУН 8, на старт- стопный вход которого поступает уровень Лог.1.выключается и его запуск произойдет лишь в момент появления на его старт-стопном входе уровня Лог.О (момент времени t фиг. 5г) , причем запуск ГУН 8 произойдет в момент прихода первого положительного фронта на счетный вход D-триггера 6 после окончания импульса Лог. 1 на его информационном входе (момент времени t, на фиг, 5в) и почти соответствует нулевой фазе поднесущей. Таким образом, независимо от того в какой фазе поднесущей закончится импульс на информационном входе D-триггера 6, колебания на выходе ГУН 8 после его запуска будут в каждой строке находиться в фазе с поднесущей с небольшой разницей фаз, примерно 10-15 не, что соответствует 15-20 град.

Подобный способ запуска ГУН 8 синфаэно с приходящими колебаниями поднесущей почти исключает выброс напряжения на выходе детектора и значи

10

20

15 тельно сокращает время переходного процесса.

Формирователь k управляющих на- создает напряжение в цифро вом г,иде, которое, воздействуя на ГУН 8 через ЦАП 9 и сумматор 3, смещает демодуляционную характеристику устройства таким образом, чтобы в каждой строке напряжение на выходе устройства в моменты демодуляции защитных пакетов было равно нулю ипи определенному заданному уровню. В дальнейшем в течение активной части строки демодуляция входного сигнала производится относительно этого уровня. Сигналы цветовой синхронизации, подаваемые с третьего входа устройства на пятый вход формирователя 4 управляющих напряжений, синхронизируют подачу уровней напряжений в соответствии с цветом приходящей строки .

Ьольшая часть напряжения, выра- 25 батываемого формирователем 4 управляющих напряжений, формируется выходными кодами блока постоянной памяти 10, поступающими на входы старших разрядов ЦАП 9, с выхода которого 30 постоянное напряжение, суммируясь с выходным напряжением устройства, поступает на первый (управляющий) вход ГУН 8. Переключение кодов блока 10 постоянной памяти для строк с синим или Красным цветом производится сигналами цветовой синхронизации с третьего входа устройства (в моменты времени t ( фиг. 6,е).

Таким образом, наличие синхрон- 4д ного запуска ГУН 8 и формирование

ступенчатого напряжения на его управ- шяющем входе, сдвигающего на нужный уровень выходное напряжение устройства, сокращает время переходного 45 процесса до минимума, который равен времени установления выходного напряжения ГУН 8 после его повторного запуска и составляет около 500 не.

Точная привязка к заданному уров- 0 ню площадок демодулированных подне- сущих осуществляется следующим образом.

Демодулированный и отфильтрованный от высокочастотных составляющих сигнал с выхода устройства поступает на первый вход сумматора 3 и первый информационный вход компаратора 13, второй информационный вход которого подключен к источнику 1А опорного

5

напряжения. Величина напряжения источника 1 4 опорного напряжения определяет уровень привязки, и в частном случае может быть равна нулю. Компаратор 13, стробируемый импульсами (фиг. 6б) в момент времени (фиг. 6а) сравнивает выходное напряжение с опорным. В зависимости от результата сравнения прямой или инверсный выходы компаратора 13 разрешают прохождение одного импульса в момент времени иг- г) на суммирующий или вычитающий входы реверсивного счетчика 11, изменив его содержимое. Выходы реверсивного счетчика 11 объединены с входами параллельной записи запоминающего регистра 12 и подключены к входам младших разрядов ЦАП 9- В случае превышения уровня напряжения на выходе устройства над уровнем источника 1 опорного напряжения, компаратор 13 разрешает прохождение счетных импульсов (фиг. 6г), поступающих с выхода элемента НЕ 17, через элемент И-НЕ 15 на суммирующий вход реверсивного счетчика 11, содержимое которого при этом увеличивается. В результате увеличивается напряжение на управляющем входе ГУН 8, частота выходного напряжения которого также растет. Напряжение на выходе устройства будет уменьшаться до тех пор, пока не станет ниже уровня источника опорного напряжения Теперь компаратор 13 разрешает прохождение импульсов (фиг. 6г) через элемент И-НЕ 16 на вычитающий вход реверсивного счетчика 11, и процесс привязки повторяется аналогично, но в обратном направлении.

В. схеме привязки устройства в синих и красных строках использован один реверсивный счетчик 11 и запоминающий регистр 12, который состоит из двух последовательно соединенных регистров, причем по положительному фронту происходит запись в первый регистр, а по отрицательному - записанная информация появляется на выходе второго регистра. В момент времени t- (фиг. 6в) содержимое запоминающего регистра 12 появляется на его выходе, а, следовательно, на входе реверсивного счетчика 11. В момент времени t, (фиг 6в) содержимое реверсивного счетчика 11 переписывается в запоминающий регистр 12. Запись из запоминающего регистра 1 в ревер5

0

5

0

5

0

5

0

5

сивный счетчик 11 производится в момент времени t 2 (фиг. 6д).

Таким образом, результат процесса привязки, например, в красных строках, запоминается в момент времени t6, а запись результата процесса привязки в реверсивный счетчик 11 произойдет через строку в момент времени 1.

Выше указывалось, что применение запуска ГУН 8 синхронно с входным сигналом позволяет уменьшить сдвиг фаз между входными сигналами и колебаниями ГУН 8 до 10-15 не. Уменьшить эту величину практически до нуля позволяет применение элементов 18-22 и выполнение ГУН 8 с встроенным ждущим одновибратором и третьим (управляющим) входом.

Блок 5 подстройки фазы колебания ГУН 8 (фиг. 3) при его повторном включении работает следующим образом. В момент времени t (фиг. 7а) прихода защитного пакета поднесущей на стробирующий вход компаратора 18 подается стробирующий импульс длительностью Ц-ty (фиг. 6в) . Компаратор 18 становится активным и сравнивает напряжение на выходе устройства с напряжением первого источника 21 опорного напряжения, в данном случае принятым равным нулю. При наличии переходного процесса на выходе устройства длительностью t.-t (фиг. 76) на выходе компаратора 1о формируется импульс (фиг. 7в) примерно такой же длительности t,-r2, открывающий ключ 19, который пропускает напряжение от второго источника 20 опорного напряжения на вход интегратора 22, выход которого подключен к входу регулировки задержки ждущего одновиб- ратора 28, находящегося в ГУН 8, который формирует задержку импульса, запускающего ГУН 8 в пределах времени полупериода цветовой поднесущей. При нормальной работе блока 5 изменение напряжения на выходе интегратора 22 соответственно изменяет задержку запускающего импульса в сторону увеличения или уменьшения, но таким образом, что разность фаз между входным сигналом и колебание запущенного ГУН 8 при этом уменьшится (интервал меньше, чем интервал t,-t фиг. 7г).

При интегрализации схемы устрой- i ства аналоговый интегратор 22 ввиду

необходимости применения конденсатора довольно большой емкости выполнит сложно, поэтому целесообразно выполнение интегратора в цифровом виде.

Блок 5 подстройки фазы колебания (цифровой) ГУН 8 (фиг. М работает следующим образом.

В зависимости от длительности переходного процесса при демодуляции защитных пакетов поднесущих компараторов 18 сформирует импульс длительностью t,-tЈ (фиг. 7в), на это же время получит разрешение генератора 25 импульсов, который вырабатывает некоторое количество импульсов (фиг. 7д), которое увеличит содержимое счетчика 26. Код, поступающий на входы ЦАП 27, увеличит его выходное напряжение (фиг. 7е), которое определенным образом воздействуя на третий (управляющий) вход ГУН 8, изменит задержку запускающего импульса в сторону уменьшения разности фаз входного сигнала и колебаний ГУН 8.

Таким образом, введение D-триггера 6, формирователя 7 импульсов и формирователя Ц управляющих напряжений позволяет, существенно сократить время переходного процесса при демодуляции защитных пакетов поднесущих телевизионного сигнала системы Секам, а введение генератора 25 импульсов, счетчика 26 и ЦАП 27 позволяет обеспечить возможность интеграции схемы устройства.

Формула изобретения

10

15

20

5

0

5

0

5

0

5

формирователь импульсов и D-триггер, сметный вхсд которого соединен с первым входом фазового детектора, выход- с вторым входом генератора, управляемого напряжением, а информационный вход - с первым выходом формирователя импульсов, второй и третий и четвертый выходы которого соединены соответственно с вторым входом устройства демодуляции телевизионного сигнала системы Секам, вторым, третьим и четвертым входами формирователя управляющих напряжений, первый вход которого соединен соответственно с первым входом сумматора и является выходом устройства демодуляции телевизионного сигнала системы Секам, третий вход которого соединен с пятым входом формирователя управляющих напряжений, выход которого через цифроаналоговый преобразователь соединен с вторым входом сумматора, блок подстройки фазы, первый вход которого соединен с вторым входом формирователя управляющих напряжений, второй вход соединен с выходом фильтра нижних частот, а выход соединен с третьим входом генератора, управляемого напряжением.

5

0

циинный вход которого соединен с выходом второго источника опорного напряжения, а выход - с входом интегратора .

. Устройство по п. отличающееся тем, что блок подстройки фазы содержит источник опорного напряжения, генератор импульсов, счетчик, цифроаналоговый преобразователь и компаратор, первый и второй информационные входы которого соединены соответственно с выходом источника опорного напряжения и с вторым входом блока подстройки фазы, первый вход которого соединен со стробирующим входом компаратора, выход которого соединен с входом запрета генератора импульсов, выход которого соединен со счетным входом счетчика, цифровые выходы которого соединены с входами цифроаналогового преобразователя, выход которого является выходом блока подстройки фазы.

9ЈоfyriiwaxttduvH xriftKHwgDdufi (н/ешодос/яыйоф

Щ/о

Ы

U

91

Ј1

Si

//

ндогпд

пердыи Вход

Первый вход

„ оВторой

дход

Фиг.З

Выхсд

Фиг. 6

t

Фа 7

| СПОСОБ ПРОИЗВОДСТВА ВОДКИ "РУССКАЯ ВЫДЕРЖКА" | 2009 |

|

RU2415911C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1991-10-30—Публикация

1989-10-23—Подача