12

рез фазовращатель на iaO° 23. Кроме того, колебания с ГОС 7 на дополнительные синфазный и квадратурный ПК 8 и 9 поступают через переключатель 11 мощности, управляемый импульсаьш с формирователя 3 импульсов . В результате опорные колебания на них проходят либо непосредственно,либо через фазовращатель на 180 12, т.е. при нечетных посыпках

Изобретение относится к радиотехнике и может быть использовано да1я детектирования многочастотных взаимоортогональных сигналов.

Цель изобретения -повышение помехоустойчивости .

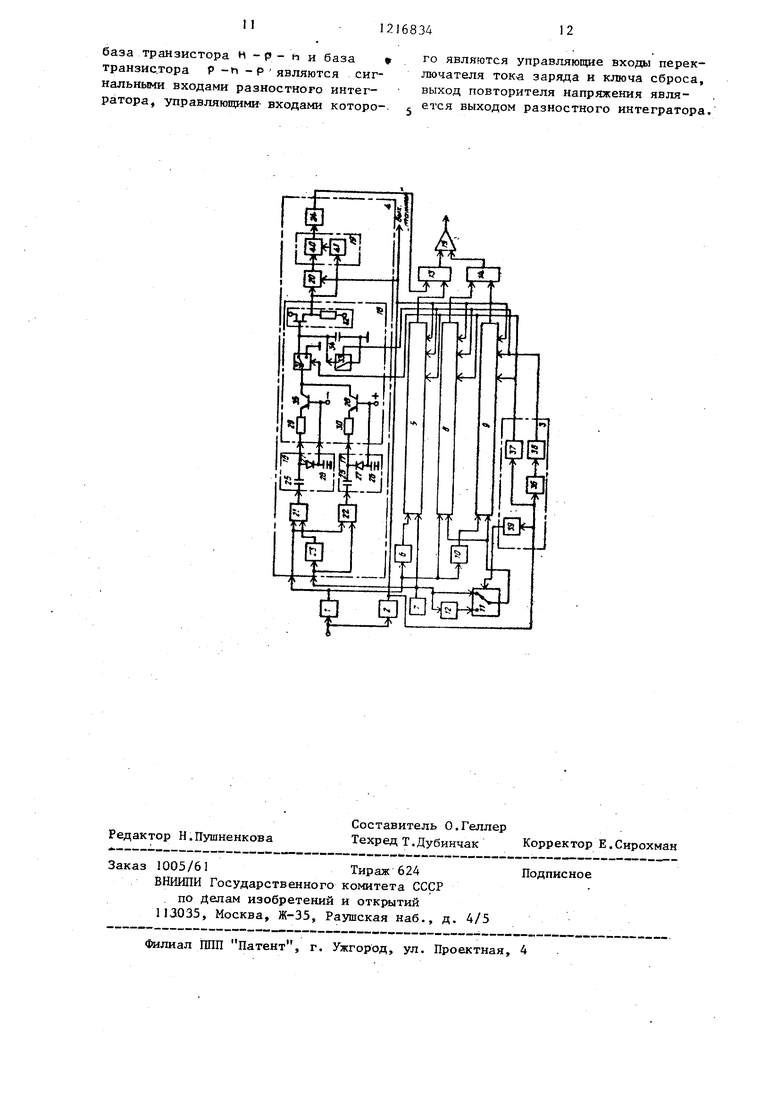

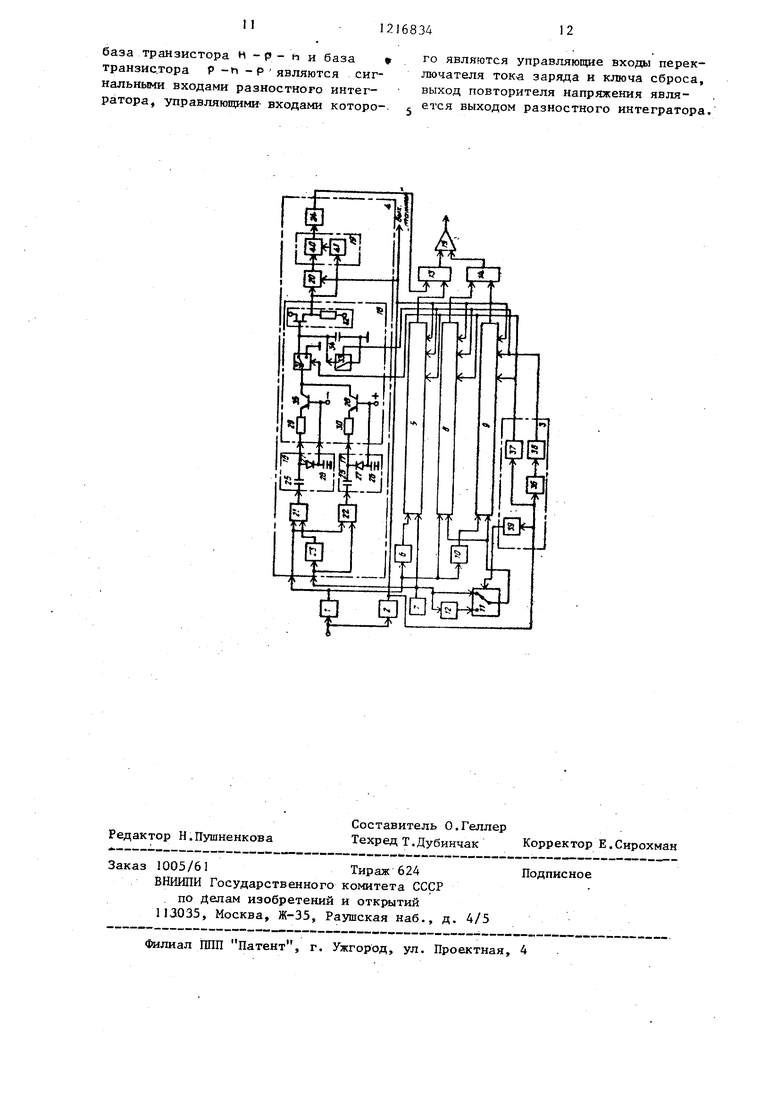

.На чертеже изображена структурная электрическая схема предложенного демодулятора. .

Демодулятор сигналов с фазораз- ностной модуляцией содержит распределитель 1 мощности, блок 2 синхронизации, формирователь 3 импульсов, основной синфазный подканал 4, основной квадратурный подканал 5j первый фазовращатель на 90 6, генератор 7 опорных сигналов, дополнительный синфазный подканал 8, дополнительный квадратурный подканал 9, второй фазовращатель на 90° 10, переключатель 11 мощности, фазовращатель на 180 12, первьй и второй сумматоры 13 и 14, компаратор 1

Каждый основной и дополнительный синфазный и квадратурные подканалы содержат первый и второй детекторы 16 и 17, разностный интегратор 18, вычитатель 19, блок 20 памяти, первый и второй сумматоры 21 и 22 мощности, фазовращатель 23, вьтрямитель 24. Каждый детектор содержит первый и второй конденсаторы 25 к 26 VI диод 27.

Разностный интегратор 18 содержит транзистор р-п-р 28, первый и второй резисторы 29 и 30, переключатель 31 тока заряда, повторитель 32 напряжения, ключ 33 сброса, интегрирующий конденсатор 34,транзистор г -Р-«35. Формирователь импульсов содержит инвертор 36, пер34

изменяется знак у проекций канального сигнала., С ПК 4 и 5 сигналы поступают на сумматор 13, а с ПК 8 и 9 - на сумматор 14. С сумматоров 14 сигналы поступают на компаратор 15. Знаки напряжения на. выходе компаратора 15., т.е. на информационном выходе демодулятора, соответств тот знакам символов переданной информации. 4 з.п. ф-лы. 1 ил.

вый и второй ждущие мультивибраторы 37 и 38, делитель 39 частоты.

Вычитатель содержит сумматор 40 и инвертир 41.

Демодулятор работает следующим образом.

На вход демодулятора поступает групповой сигнал s (t), который представляет собой сумму N-канальных сигналов. Каждый из канальных сигналов имеет частоту tjj, , амплитуду Sy и фазу М. Посылки ка- нальньлх сигналов различаются между собой только фазами , поэтому

фазы канальных сигналов будем обозначать М к п Д индекс h означает номер посылки.

С учетом вышеуказанногогрупповой сигнал на п-ой посылке Sfl(t)

можно записать как сумму

N

s,{U 5, sinCi tt YK.PI)- к,-1

Демодулятор выделяет нз этой суммы один канальный сигнал, частота которого совпадает с частотой генератора 7 опорных сигналов uJg дан- ного демодулятора.

Блок 2 синхронизации выявляет границы посылок групповогосигнала, т.е. моменты смены фазы. В соответствии с выявленными границами посылок формирователь 3 импульсов выра- батыш1ет .последовательность управляющих импульсов,.поступающих на управляющие входы синфазных и квадратурных подканалов 4, 8 и 5, 9 демодулятора. При этом сначала пода

ется импульс от блока 2 синхронизации, соответствующий, границе между посылками. Во время действия этого импульса.происходит запись в бло 20 памяти- результата обработки очередной посылки из разностного интегратора 18. Одновременно срабатвает ждущий мультивибратор 37, который подключает переключатель 31 тока заряда к. заземленной шине. Задний фронт импульса, от блока 2 синхронизации через, инвертор 36 запускает ждущий мультивибратор 38, который замыкает ключ 33 сброса и происходит разряд интегрирующего коденсатора 34. После возврата в исходное состояние ждущего- мультивибратора 38 и ключа 33 сброса возвращается в исходное состояние ждущий мультивибратор- 37 и переключатель 31 тока заряда. Начинается обработка следующей сигнальной пось ки. Длительность неустойчивого состояния ждущего мультивибратора 37 выбрана равной длительности защитного промежутка, причем длительност посылки равна сумме интервала ортогональности группового сигнала и длительности защитного промежутка. Поэтому длительность заряда интегрирующего конденсатора 34 равна интервалу ортогональности.

Входной многочастотный групповой сигнал поступает также через распределитель 1 мощности на входы сумматоров 21 к 22 мощности, на другие входы которых поступает, колебание от генератора 7 опорных сигналов, причем фаза опорного колебания на первом входе сумматора 21 мощности отличается на 180 от фазы этого колебания на втором входе сумматора 22 мощности.

На выходе сумматора 22 мощности будет сумма группового сигнала Sc(t) и опорного колебания Sb(t) S(,sinbL)ot, т.е.

s;(t) + Sc(t),

а напряжение на выходе сумматора 21 мощности равно разности

si(t) - s(t), .

так как групповой сигнал на вход сумматора 21 мощности-поступает в противофазе.

В результате детектирования этих сигналов на детекторах 16 и 17 появится ток 1 через резистор. 29 и ток через резистор 30 разностного

-

12168344

интегратора 18. Низкочастотные сое- тавл5пощие этих токов при выполнении условия, что амплитуда опорного колебания значительно больше группового : сигнала, равны

,-„-t tДs c s;),),

14

где о( Ир- коэффициенты, зависящие. от характеристик диода 27, а 5 и S - амп-т1туды группового сигнала и опорного колебания.

Диалогично ток 1 равен

Iz--o CoC Sc s;)-p -ScCU-.SoCt)R

io

В этих выражениях знак минус для тока 1 определяется направлением включения диода 27, а знак минус перед вторым членом этого выражения определяется тем, что на первый вход сумматора 21 мощности опорное колебание подается в противофазе по сравнению с опорным колебанием на втором входе сумматора 22 мощности.

Ток заряда 1 интегрирующего.конденсатора 34 практически равен сум0

ic-I,-U--( Э,

Iv И I.

Rie

т.е.

oL.

50

)(s .s;)

fe)

Учитывая, что S S и обозначая

&,

49

30

Э

Т

Sc(t) SoCt),

oi 1 cJ. i ,uoL

° Z9 t SO P.

запишем

т -AOL . ,A u g -So

Этот ток заряжает интегрирукнций конденсатор 34 в течение интервала ортогональности Т, который определяется состоянием переключателя 31 тока заряда. Напряжение U на интег- рирующем конденсаторе 34 в конце заряда будет

т

lUc-g |СДо(. sincj t X о

у SKSiH()

При интервале между частотами группо- вого сигнала-, кратном 21Г/Т, результат накопления заряда на интегрирующем конденсаторе 34 определяется параметрами только того канального

сигнала, частота которого совпадает с частотой опорного колебания. При этом

Uc-p(AO(

-Sp

Второй член этой суммы пропорционален амплитуде и косинусу фазы выделяемого L -го канального сигнала, т.ё.-.Нроекции канального сигнала на опорное колебание,. Обозначим синфазную проекцию канального сигнала .Хр, т.е. J-. cosH e Xg:, тогда

.ис--Хе- йог-5„,

Полученное напряжение U запишется в блоке 20 памяти, после чего ключ 33 сброса разрядит интегрирующий конденсатор 34.

Рассмотрим теперь, обработку одного канального сигнала на двух (п-1)-й и п-й посылках сигнала.

На Cn-l )-й посылке на интегрирующем конденсаторе 34 накопится напряжение Х,,+ -f jTUd-S,.

Отметим, что второй член этой сум Nbi независим от номера посылки.

Напряжение (U(,) запишется в блок 20 памяти. На следующей п-й посылке в интегрирующем конденсаторе 34 накопится напряжение

So.

и

Т EQi M

Напряжение на выходе вычитателя 19 райно разности

UH- , х,- х,.

После выпрямителя 27 получим абсолютную величину разности проекций Х и Xf соседних посылок данного канального сигнала.

Аналогичные процессы иуоисхидят в квадратурном подканале 5. Однако вследствие того, что групповой сигнал поступает на вход квадра- (Турного подканала 5 через фазовращатель на 90 6, дающий фазовый сдвиг на 90 , на.интегрирующем конденсатре 34 разностного интегратора 18 этого квадратурного подканала 5 накопится напряжение

(Uc)

KfeoAP

-.(uct-So + p So SE )

Второй член этой суммы пропорци- 1 онал:ен квадратурной проекции канального сигнала Yj. В результате,на вы- ходе вычитателя 19 квадратурного подканала 5 получим величину

(

)кБад

Y - У h п-1

ш

Выпрямитель 24 сформирует абсолютную величину разности квадратурных проекций

На выходе сумматора 13 получим сумму

ix, - Х„,| + Ни - Y,,f.

Рассмотрим теперь процессы в дополнительных синфазном и квадратурном подканалах 8 и 9. Опорное колебание на их опорные входы проходит через переключатель 11 мощности. Состояние переключателя 11 мощности определяется импульсами от формирователя 3 импульсов, причем на четных посылках переключатель 11 мощности находится, например, в правом положении, а на нечетных посылках - в левом положении. Это приводит к изменению знаков на противоположные у проекций

канального сигнала на нечетных по/,

сылках (из-за сдвига фазы опорного

колебания на 180°j. В результате, если п-я посылка окажется нечетной, получим для синфазного подканала 8, что

(и, - и.,),-. -х. - X.. . -(X. +

ч- Хп-,)

дом п Хп-1- -(г,

ЕСЛИ же п-я посылка окажется четной, а .(п-1)-я нечетной, тогда получим

(и,- )n п + n-i- На выходе выпрямителей 24 дополнительных синфазного и квадратурного подканалов 8 и 9 всегда получаем сумму проекций, а на выходе сумматора 14 получим сумму

|Хп+ Х,,|+

Yn + Vil

Напряжение на выходе компаратора 15 будет положительным., если

К, 1Ун Уи-11 1 у,-Хии1 |Ун% 1

Этот случай соответствует нулевой разности фаз между п-й и (п-1)-й посылками. Если разность фаз между

посылками на передаче 180, тогда разность проекций окажется больше их суммы.

Таким образом, знаки напряжения на выходе компаратора 15 соответствует знакам символов переданной информации по 1-ому канальному сигналу.

При детектировании сигналов путе нелинейной обработки в диодных детекторах 16 и 17 на сигнальных выходах диодных детекторов 16 и 17 помимо полезного сигнала возникает еще постоянное напряжение, обусловленное детектированием опорного колебания, которое в данном случае значительно больше полезного сигнала. Полезный сигнал на кажд посылке представляет собой также постоянное напряжение.

Вследствие того, что сигнал представляет собой постоянное напряжени его невозможно вьщелить обычными методами.

Постоянная составляющая напряжения, обусловленная детектированием опорного колебания, на выходах диодных детекторов 16 и 17 имеет противоположные полярности вследствие различного включения диодов 27. Токи через транзисторы и-Р-м и p-h-p 35 и 28 разностного интегратора 18, вызванные этой составляющей, протекают в противоположных направлениях и взаимно компесируются в их коллекторной цепи. Постоянные составляющие токов, обуслоленных детектированием полезного сигнала, будут протекать в одинаковых направлениях и сложатся в коллекторной цепи транзисторов и -р -п и р-м -р 35 и 28 разностного интегратора 18. Таким образо в коллекторной цепи транзисторов п-р - и и р -п -р 35 и 28 происходит компенсация постоянных составляющих, обусловленных детектированием опорного колебания в детекторах 16 и 17 и сложение постоянных токов, обусловленных детектированием полезного сигнала.

Вследствие этого составляющая, обусловленная детектированием опорнго колебания, проявляется только из за различия в йараметрах диодов 27, транзисторов h-p-ri и р-п-Р 35 и 28 и сумматоров 21 и 22 мощности. Однако даже такой остаток иекомпен10

15

0

5

0

5

0

5

0

сированной постоянной составляющей, обусловленной детектированием опорного колебания, может оказаться близким к величине полезного сигнала. Попытка устранить разброс параметров указанных компонентов привела бы к значительному ухудшению технологичности аппаратуры.

В предлагаемом демодуляторе влияние нескомпенсированной постоянной составляющей устраняется тем, что на выход каждого .синфазного и квадратурного подканала 4, 8 и 5, 9 поступает всегда разность проекций канальных сигналов, поступивших на их выходы.

Формула изобретения

1. Демодулятор сигналов с фазо- разностной модуляцией, содержащий распределитель мощности, выход которого соединен с сигнальным входом основного синфазного подканала, с входом первого фазовращателя на 90° и с входом второго фазовращателя на 90°, выход первого фазовращателя на 90° подключен к сигнальному входу основного квадратурного показателя, .опорный вход которого соединен с выходом генератора опорных сигналов и с опорным входом основного синфазного подканала, выход которого соединен с первым входом первого сумматора, второй вход которого подключен к выходу основного квадратурного подканала, управляющий вход, которого соединен с управляющим входом основного синфазного подканала и с выходом блока синхронизации, выход первого сумматора соединен с первым входом компаратора, второй вход которого подключен к выходу второго сумматора, отличающийся тем, что, с целью повышения помехоустойчивости, в него введены дополнительные синфазный и квадратурный подканалы, формирователь импульсов, переключатель мощности и фазовращатель на 180 , вход которого подключен к выходу генератора опорных сигналов и к первому входу переключателя мощности, выход которого соединен с опорным входом дополнительного синфазного подканала и с опорным входом дополнительного квадратурного подканала.

сигнальный вход которого соединен с выходом второго фазовращателя на 90, вход которого подключен к сигнальному входу дополнительного синфазного подканала, управляющий вход которого соединен с управляющим входом дополнительного квадратурного подканала с выходом блока синхронизации и с входом формирователя импульсов, первый выход которого соединен с управляющим.- входом переключателя мощности, второй вход которого.подключен к выходу фазовращателя на 180 , npii этом второй и третий выходы формирователя импульсовподключены соответственно к первому и второму дополнительным управляющим входам основных синфазного и квадратурного прдканалов и к первому и второму дополнительным управляющим входам дополнительных синфазного и квадратурного подканалов,; выходы которы подключены соответственно к первому и второму входам второго сумматора, а вход распределителя мощ- , ности соединен с входом блока синх- : ронизации.

2. Демодулятор по п.1, отличающийся тем, что каждый основной и дополнительный синфазные и квадратурные подканалы содержат вьш рямитель, вычитатель, блок памяти, разностный интегратор, два детектора, два сумматора мощности и фазовращатель ,.выход которого соедине с первым входом первого сумматора мощности, второй вход которого сединен с первьм входом второго суммтора мощности, второй вход которого подключен к входу фазовращателя, выходы первого и второго сумматоров мощности подключены к. входам соответственно первого и второго детекторов, выходы которых соединены с соответствующими сигнальными входами разностного интегратора, выход которого соединен с первы входом вычитателя и с первым входом блока памяти, выход которого соединен с входом вьтрямителя, выход которого является выходом каждого основного и дополнительного синфазных и квадратурных подканаловi сигнальным, опорным, управляющим, первым дополнительным и вторым дополнительным входами которого- являются соответственно второй вход первого

0

5

0

5

0

5

5

5

сумматора мощности, вход фазовращателя, второй вход блока памяти, первый и второй управляющие входы разностного интегратора.

3.Демодулятор по п.1, о т -л и-, чающийся тем, что- формирователь импульсов содержит два ждущих мультивибратора инвертор

и делитель частоты, вход которого подключен к входу первого ждущего yльтивибpaтopa и к входу инвертора, выход которого подключен к входу второго ждущего мультивибратора, при этом выход делителя частоты , выход первого ждущего мультивибратора и выход второго ждущего мультивибратора являются соответственно первым, вторым и третьим выходами формирователя импульсов, входом которого является вход делителя частоты.

4.Демодулятор по п.2, о т л и- чающийся тем, что каждый из детекторов содержит первый и второй конденсаторы и диод, анод (катод) которого соединен с первым выводом первого конденсатора, первый вывод второго конденсатора соединен с катодом (анодом) диода второй вывод второго конденсатора соединен с земляной шиной, при этом второй вывод первого конденсатора является входом детектора, ; выходами которого являются анод и катод диода.

5.Демодулятор по п.2, о т л и- чающийся тем, что разностный интегратор содержит два резистора, транзистор п - р - п , транзистор Р-h -р , переключатель . тока заряда, интегрирующий конденсатор, ключ сброса и повторитель напряжения, вход которого подключен к первому выводу интегрирующего ковденсатора., к первому выходу ключа сброса и к первому выходу перек пючателя тока заряда, сиг- нальнгзш вход которого соединен с коллекторами транзистора п -р -п

и транзистора Р -v -f , эмиттеры которых подключены к первым выводам соответственно первого и второго резисторов, второй выход переклю- .чателя тока заряда, второй вывод интегрирующего конденсатора.и второй выход ключа сброса подключены .к земляной пшне,,при этом вторые выводы первого и второго резисторов.

база транзистора Н -р- и и база го являются управляющие входы перектранзис.тора Р -п - Р являются сиг-лючателя заряда и ключа сброса,

нальными входами разностного интег-выход повторителя напряжения являратора, управляющими- входами которо-с выходом разностного интегратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для детектирования фазоманипулированных сигналов | 1982 |

|

SU1051737A1 |

| Устройство синхронизации несущей частоты | 1985 |

|

SU1356249A1 |

| УСТРОЙСТВО для ИЗМЕРЕНИЯ МОЩНОСТИ:!оюзя-°-^'-^^•^?ПНП-.ТслНл^;::^:^:;:| | 1972 |

|

SU351170A1 |

| Устройство для корреляционного приема фазоманипулированных сигналов с подстройкой частоты | 1984 |

|

SU1221762A1 |

| Устройство для когерентного приема фазоманипулированных сигналов | 1972 |

|

SU443455A1 |

| Устройство для полосовой адаптивной коррекции сигналов относительной фазовой модуляции | 1982 |

|

SU1100736A1 |

| УСТРОЙСТВО ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ С ИСПОЛЬЗОВАНИЕМ ШИРОКОПОЛОСНЫХ ШУМОПОДОБНЫХ СИГНАЛОВ ПРИ КОДОВОМ РАЗДЕЛЕНИИ КАНАЛОВ | 2001 |

|

RU2221344C2 |

| Устройство формирования и обработки широкополосных сигналов | 2018 |

|

RU2691733C1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU949838A1 |

| Устройство для адаптивного приема дискретных сигналов | 1982 |

|

SU1109940A1 |

Изобретение относится к радиотехнике и обеспечивает повьшение помехоустойчивости. N канальных сигналов, поступающих на вход демодулятора, отличаются только фазой fK . Из суммарного сигнала выделяется канальный сигнал, частота которого совпадает с частотой генератора опорных сигналов (ГОС)7 . Блок 2 синхрони- зации определяет моменты смены фазы во входном сигнале. Его импульсы, соответствующие границам посылок, поступают на тактовый выход демодулятора, на синфазные и квадратурные подканалы (ПК) 4,8 и 3,9 и на формирователь 3 импульсов, импульсы которого поступают на управляющие входы ПК 4,8 и 5,9. Входной групповой сигнал через распределитель 1 мощности поступает на сумматоры мощности (см) 21 и 22 подканалов 4 и 8 непосредственно,а на СМ 21 и 22 подканалов 5 и 9 - через соот- О ветствующие фазовращатели на 90 6 и 10. На другие входы СМ 21, 22 поступают колебания ГОС 7, причем на СМ 21 опорные колебания проходят чекл ff

Редактор Н.Пушненкова

Заказ 1005/61Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ППП Патент, г. Ужгород, ул. Проектная, 4

Составитель О.Геллер

Техред Т.Дубинчак Корректор Е.Сирохман

| Заездный A.M | |||

| и др | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Печь для сжигания твердых и жидких нечистот | 1920 |

|

SU17A1 |

| Демодулятор сигналов с фазоразностной модуляцией | 1980 |

|

SU946007A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-03-07—Публикация

1984-08-28—Подача