Изобретение относится к электротехнике и предназначено для использования при построении экономичных источников трехфазного переменного напряжения на основе инверторов.

Целью изобретения является повышение надежности.

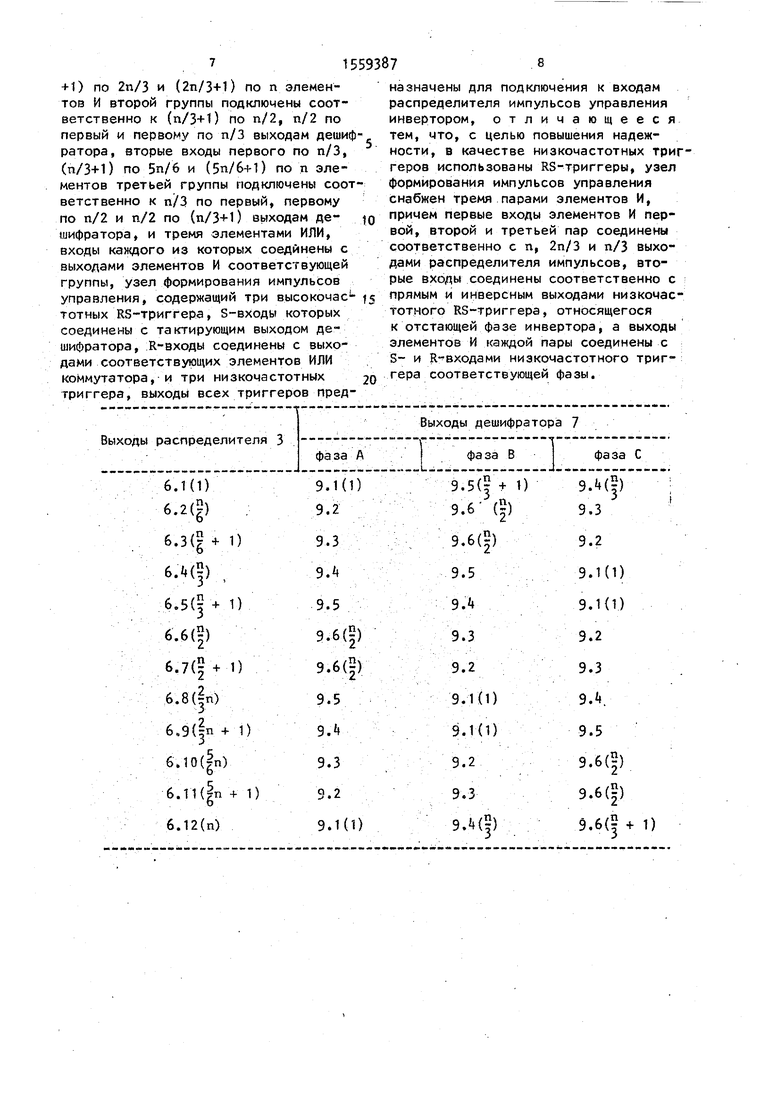

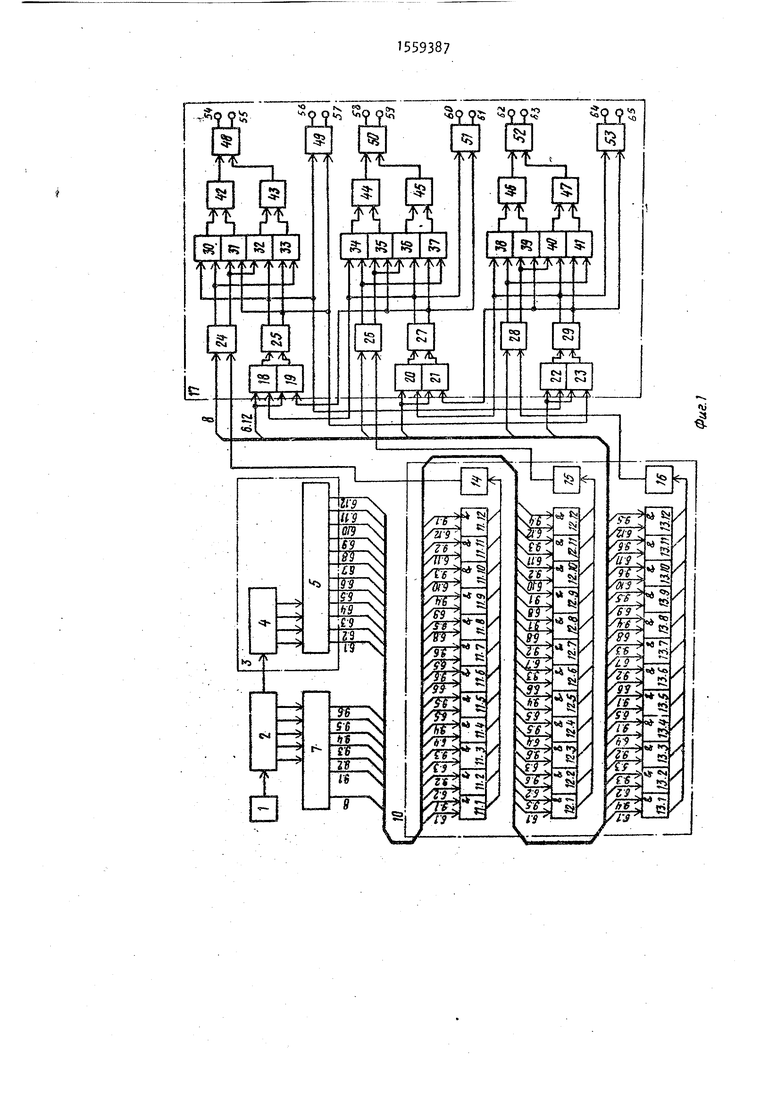

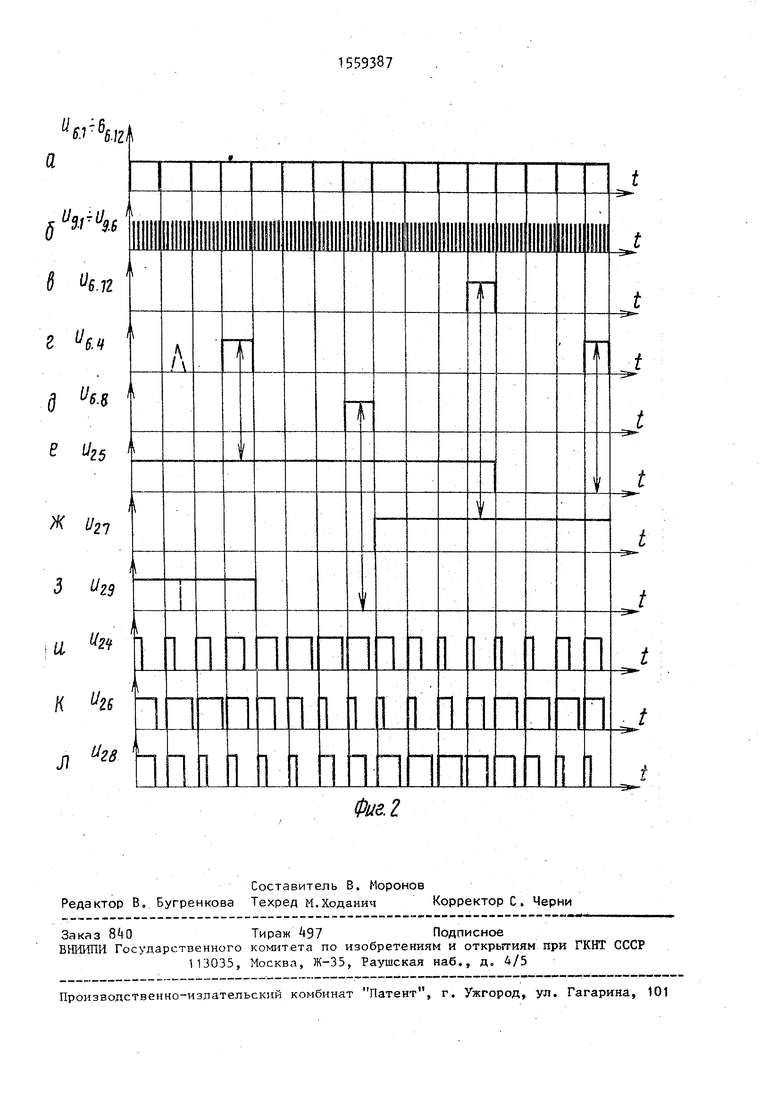

На фиг.1 представлена функциональная схема устройства для управления трехфазным инвертором; на фиг. 2 - временные диаграммы сигналов, иллюстрирующие работу устройства.

Устройство содержит генератор 1 импульсов, счетчик 2 импульсов, ч 12-звенный распределитель 3 импульсов, состоящий из последовательно включенного четырехразрядного двоичного счетчика 4 импульсов и дешифратора 5 с выходами 6,1-6,12, являющимися одновременно выходами распределителя 3: дешифратор 7 шести импульп сов, длительность которых соотносится между собой по синусоидальному закону, с тактирующим выходом 8 и модуляционными выходами 9.1-9.6, коммутатор 10 с группами элементов И 11-13 и элементами ИЛИ 14-16, узел 17 формирования импульсов управления с тремя парами фазных стробирующих элементов И 18-23, с дюочирующими триггерами 24-29, из которых триггеры 25, 26 и 28 являются высокочастотными, а триггеры 25, 27 и 29 - низко- частотными элементами И 30-41, элементами ИЛИ 42-47 и развязывающими усилителями 48-53 мощности. Позициями 54-65 на схеме обозначены клеммы для подключения базовых цепей транзисторов управляемого инвертора. В последнем в выходные диагонали однофазных мостов в лючены трансформато- рьц вторичные обмотки которых соединены в звезду с образованием фаз А, В, С. Генератор 1, счетчик 2 и распределитель 3 включены последовательно. Входы дешифратора 7 соединены (с выходами счетчика 2„ Первые входы элементов 11.1,.11.2,12.1...12.2, 13.1...13,12 подключены к выходам 6.1..6.12 распределителя 3« Вторые входы элементов 11.1.. 11.6 и - ...,11.12 подключены соответст- иенно к выходам 9.1...9.6 и 9-6 „,.9. дешифратора 7 Вторые входы элементов 12.1, 12.2, 12.3...12,8, 12,9.о 12,12 подключены соответственно к выходам 9.5,, 9,6...9.1 и 9.1.. 9,- ;, дешифратора 7. Вторые входы элементов 13.1...13.4, 13.5...13.10 и 13.11,13.12 подключены соответственно к выходам 9.4...9.1, 9.1...9.6 и 9-6...9.5 дешифратора 7. Входы элементов 14-16 соединены с выходами соответственно элементов 11.1... 1 1.1 12Л..,12,12, 13.1...13.12. R-входы триггеров 2k, 26 и 28 соединены с тактирующим выходом 8 дешифратора 7Э a S-входы - с выходами соответственно элементов ИЛИ 14-16, Первые входы элементов И 18-23 соединены соответственно с выходами 6.12, 6,4 и 6.8 распределителя 3. Вторые входы элементов И 18-23 соединены соответственно с прямыми инверсными выходами триггеров 27, 29 и 25. R-входы триггеров 25, 27 и 29 соединены соответственно с выходом элементов 18, 20 и 22, а S-входы - с выходами элементов 19, 21 и 23. Первые входьи элементов 30, 33 и 31 32 подключены соответственно к выходам триггера 2k, первые входы элементов 34 37 и 35, 36 подключены к выходам триггера 26, первые входы элементов 38, 41 и 39г 40 подключены к выходам триггера 8, вторые входы элементов 30, 33 и 31 32 с выходами триггера 25, вторые входы элементов 34, 37 и 35, 36 - с выходами триггера 27, вторые входы элементов 38, 41 и 39, 40 - с выходами триггера 29. Входы элемента 42 подключены к выходам элементов 30 и 31, входы элемента 43 - к выходам элементов 32 и 33, входы элемента 44 - к выходам элементов 34 и 35, входы элемента 45 - к выходам элементов 36 и 37, входы элемента 46 - к выходам элементов 8

0

5

0

5

0

5

0

5

0

5

и 39, входы элемента 47 - к выходам элементов 40 и 41, Входы усилителей 48, 50 и 52 соединены с выходами соответственно элементов 42 и 43, 44 и 45, 46 и 47. Входы усилителей 49, 51, 53 подключены к выходам соответственно триггеров 25, 27 и 29, Выходы усилителей 48-53 соединяются с базовыми цепями транзисторов инвертора.

Устройство работает следующим обра зом.

Генератор 1 вырабатывает на своем выходе последовательность импульсов с частотой fG кратной частоте fv синусоидального напряжения на выходе инвертора. В данном случае при fv 500 Гц выбрана fQ 384 кГц. Счетчик 2 в процессе своего функционирования осуществляет деление частоты fq на 32, так что его последний разряд переключается с частотой 12 кГц. Счетчик 4 обеспечивает счет до 12. На выходах 6„К..6.12 распределителя 3 (дешифратора 5) последовательно формируются импульсы Uj 1- иб(1(фиг. 2а}, продолжительность каждого из которых соответствует единичному временному интервалу. Общая продолжительность двенадцати временных интервалов, формируемых в пределах одного цикла счета, составляет 1 мс и соотTv

ветствует полупериоду г- выходного

напряжения инвертора.

Счетчик 2 считает до 32, причем начало его счета и полное заполнение (самообнуление) совпадают с началом и концом единичного временного интервала йинт. В дешифраторе 7 Для процесса формирования импульсов управления используется один тактирующий выход 8 и шесть модуляционных выходов 9.1... 9.6. При определении последних производится априорный подбор шести натуральных чисел (градаций), отличающихся друг от друга в порядке следования по синусоидальному закону. Ec-t ли, в частности, амплитуда выходного синусоидального напряжения характеризует число 32, соответствующее емкости счетчика 2 и общему количеству выходов дешифратора 7, то подобный ряд будет выглядеть следующим образом; 4, 12, 19, 25, 29, 31. Нетрудно убедиться в том, что использование в дешифраторе 7 модуляционных выходов 9.1...9.6 с такими порядковыми номерами обеспечивает возможность формирования для каждого из двенадцати временных интервалов на выходах егс- пределителя 3 шести длительностей (от начала интерзала до моментов появления импульсов на соответствующих выходах дешифратора 7) соотносящихся между собой по синусоидальному закону (фиг. 2, б). С помощью коммутатора 10 осуществляется разнесение импульсов, сформированных дешифратором 7 по временным интервалам, которые формирует распределитель 3. При этом синусоидальный характер приобретает уже изменение длительностей от интервала к интервалу, причем для каждой из трех фаз выходного напряжения интервалу, причем для каждой из трех фаз выходного напряжения инвертора. В таблице указаны использованные в устройстве сочетания выходов распределителя 3 и дешифратора 7, обеспечивающие с помощью элементов И-13 коммутатора 10 получение тоех совокупностей импульсов, сдвинутых друг относительно друга на 120°.

В узле 17 осуществляется формирование низкочастотных и высокочастот- ных импульсов управления для каждой из фаз инвертора,, Последовательности симметричных низкочастотных импульсов U25s

U

27 5

U

13

(фиг. 2, е, ж, з),

следующих с частотой 500 Гц, вырабатывается триггерами 25, 27 и 29. Через три пары фазных стробирующих элементов 8 и 29, 20 и 21, 22 и 23 поступают сигналы на R-еходы триггеров 25, 27 и 29 соответственно с выходов 7.12, 6 Л, 6.8 распределителя 3, а на S-входы - соответственно с прямых и инверсных выходов триггеров 27, 29 и 25, относящихся к отстоящим фазам инвертора. Длительность каждого из низкочастотных импульсов управления соответствует полупериоду

TV

-- выходного напряжения инвертора.

последовательности высокочастотных импульсов Uj4 5 U-i6 ijs представляющие собой псевдосинусоидальные сигналы, высабэтываются триггерами 2b, 26 и 28, к одним входам которых запускающие сигналы подводятся с тактирующего выхода 8 дешифратора 7, а к другим входам - с выходов соответственно элементов . Несущая частота псевдосинусоидальных сигналов равна 12 кГц. С помощью элемен

59387«

тов 30,..1 и k2. . производится

разнесение фазных последователь. тей высокочастотных импульсов U,

10

It

un U29 Ha разные полупериоды низкочастотных импульсов U25, , Ui7 с образованием в конечном счете двухпо- лупериодных псевдосинусоидальных си(- налов. Развязывающие усилители 8-53 мощности, помимо усиления сигналов управления, обеспечивают гальваничес«- кую развязку всех четырех управляющих цепей.

Усиленные низкочастотные сигналы 55 с выходов усилителей А8-53 используются для управления транзисторами инвертора.

Единичные сбои в работе формирующих низкочастотных триггеров 25 27 и 29 не приводят к устойчивому расфа- зированию системы трехфазного напряжения, поскольку уже на следующем после сбоя такте устанавливаются исходные фазовые соотношения.

Иллюстрация воздействия помехи, возникающей, например, на выходе 6,k дешифратора 5, показана на фиг. 2 г, з пунктиром. На Фиг. 2, Bf г, д стрелками отмечены стробирующие сиг- налы.

Повышение надежности устройства обеспечивается за счет стробирования переключающих импульсов с выхода рас пределителя 3 и синхронизации работы устройства в каждом периоде.

20

25

30

35

0

5

0

Формула изобретения

Устройство дпя управления трехфазным инвертором, содержащее последовательно включенные генератор импульсов, счетчик импульсов и п-звенный (п - четное число, кратное трем) распределитель импульсов, дешифратор п/2 импульсов, длительность которых соотнесена между собой по синусоидальному закону, с тактирующим выходом первого разряда, входы дешифратора соединены с выходами счетчика импульсов, коммутатор с тремя п-звенными группами элементов И, первые входы которых в каждой группе подключены к одноименным выходам распределителя импульсов, вторые входы с первого по n/2-й и с (п/2+1)-й по n-й элементов И первой группы подключены соответственно к первому по п/2 и к п/2 по первый выходам дешифратора, вторые входы с первого по п/6, (п/6+

+ 1) по 2п/3 и (2n/3+l) no n элементов И второй группы подключены соответственно к (п/3+1) по п/2, п/2 по первый и первому по п/3 выходам дешифратора, вторые входы первого по п/3, (п/3+1) по 5п/6 и (5п/6-И) по n элементов третьей группы подключены соответственно к п/3 по первый, первому по п/2 и п/2 по (п/3+1) выходам де- шифратора, и тремя элементами ИЛИ, входы каждого из которых соединены с выходами элементов И соответствующей группы, узел формирования импульсов управления, содержащий три высокочас1- тотных RS-триггера, S-входы которых соединены с тактирующим выходом дешифратора, R-аходы соединены с выходами соответствующих элементов ИЛИ коммутатора, и три низкочастотных триггера, выходы всех триггеров предназначены для подключения к входам распределителя импульсов управления инвертором, отличающееся тем, что, с целью повышения надежности, в качестве низкочастотных тригеров использованы RS-триггеры, узел формирования импульсов управления снабжен тремя парами элементов И, причем первые входы элементов И первой, второй и третьей пар соединены соответственно с п, 2п/3 и п/3 выходами распределителя импульсов, вторые входы соединены соответственно с прямым и инверсным выходами низкочастотного RS-триггера, относящегося к отстающей фазе инвертора, а выходы элементов И каждой пары соединены с S- и R-входами низкочастотного триггера соответствующей фазы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления трехфазным транзисторным инвертором | 1985 |

|

SU1288867A1 |

| Устройство для управления транзисторным мостовым инвертором | 1982 |

|

SU1102009A1 |

| Устройство для управления транзисторным мостовым инвертором | 1986 |

|

SU1515295A1 |

| Способ управления трехфазным мостовым инвертором и устройство для управления трехфазным мостовым инвертором | 1981 |

|

SU1032592A1 |

| Способ управления трехфазным мостовым инвертором,работающим на двигатель переменного тока,и устройство для его осуществления | 1984 |

|

SU1270850A1 |

| Преобразователь частоты | 1981 |

|

SU1069104A1 |

| Способ управления трехфазным мостовым инвертором | 1985 |

|

SU1356158A1 |

| Устройство для регистрации потоков подвижных объектов | 1984 |

|

SU1193704A1 |

| Цифровой измеритель температуры | 1982 |

|

SU1111038A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ЛИНЕЙНО-ЧАСТОТНО-МОДУЛИРОВАННОГО СИГНАЛА | 1996 |

|

RU2110145C1 |

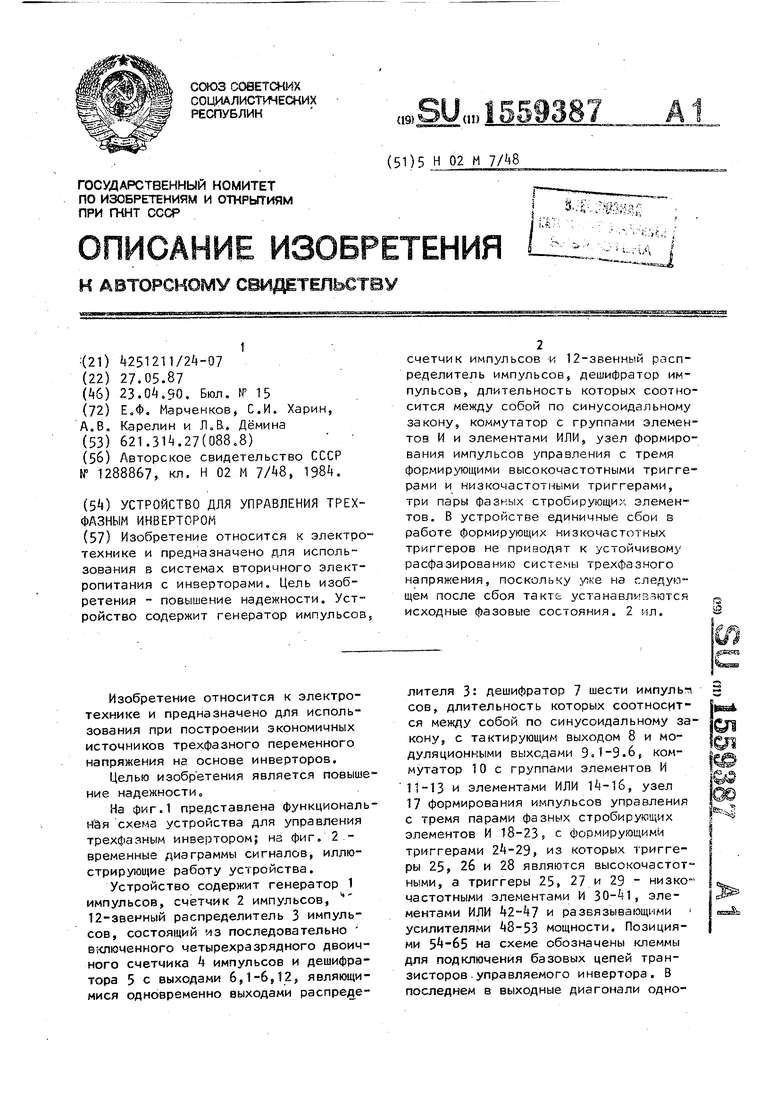

Изобретение относится к электротехнике и предназначено для использования в системах вторичного электропитания с инверторами. Цель изобретения - повышение надежности. Устройство содержит генератор импульсов, счетчик импульсов и - звенный распределитель импульсов, дешифратор импульсов, длительность которых соотносится между собой по синусоидальному закону, коммутатор с группами элементов И и элементами, узел формирования импульсов управления с тремя формирующими высокочастотными триггерами и низкочастотными триггерами, три пары фазных стробирующих элементов И. В устройстве единичные сбои в работе формирующих низкочастотных триггеров не приводят к устойчивому расфазированию системы трехфазного напряжения, поскольку уже на следующем после сбоя такте устанавливаются исходные фазовые состояния. 2 ил.

1)

1}

О 1)

+ 1)

9Л

D )

.Гбб./2

а

s

в %72

г иб.ч

S и е «25

Ж 1/21

3 и29

,ц %

К %

л

ига

t

| Устройство для управления трехфазным транзисторным инвертором | 1985 |

|

SU1288867A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1990-04-23—Публикация

1987-05-27—Подача