Изобретение относится к автоматике и вычислительной технике, в частности к устройствам функционального преобразования сигналов, и может быть использовано для интегрирования входного электрического сигнала.

Целью изобретения является повышение точности интегрирования.

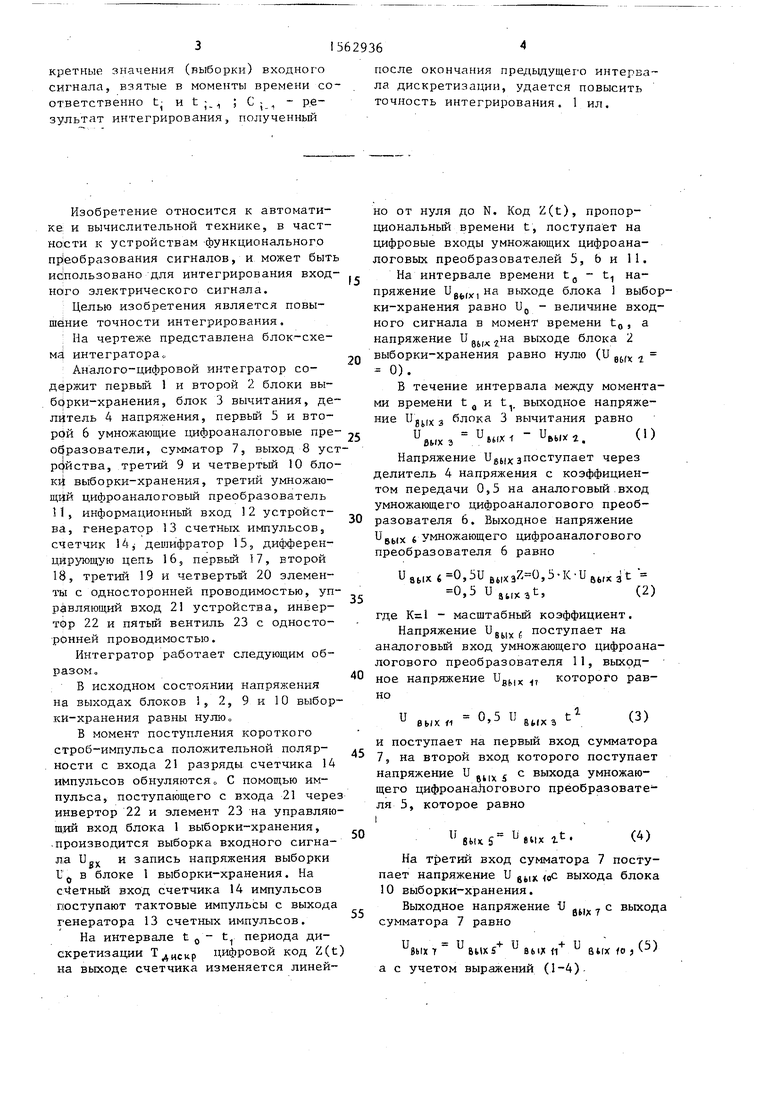

На чертеже представлена блок-схема интегратора.

Аналого-цифровой интегратор содержит первьй 1 и второй 2 блоки выборки-хранения, блок 3 вычитания, делитель 4 напряжения, первый Ь и второй 6 умножающие цифроаналоговые преобразователи, сумматор 7, выход 8 устройства, третий 9 и четвертый 10 блоки выборки-хранения, третий умножающий цифроаналоговый преобразователь 11, информационный вход 3 2 устройства, генератор 13 счетных импульсов, счетчик 14, дешифратор 15, дифференцирующую цепь 16S первьй 17, второй 18, третий 19 и четвертьй 20 элементы с односторонней проводимостью, управляющий вход 21 устройства, инвертор 22 и пятый вентиль 23 с односторонней проводимостью.

Интегратор работает следующим образом

В исходном состоянии напряжения на выходах блоков , 2, 9 и 10 выборки-хранения равны нулю

В момент поступления короткого строб-импульса положительной полярности с входа 21 разряды счетчика 14 импульсов обнуляются С помощью импульса, поступающего с входа 21 через инвертор 22 и элемент 23 на управляющий вход блока 1 выборки-хранения, производится выборка входного сигнала Ugx и запись напряжения выборки I 0 в блоке 1 выборки-хранения. На счетный вход счетчика 14 импульсов поступают тактовые импульсы с выхода генератора 13 счетных импульсов.

На интервале t 0 - t периода дискретизации Тдискр цифровой код Z(t) на выходе счетчика изменяется линейно от нуля до N. Код Z(t), пропорциональный времени t, поступает на цифровые входы умножающих цифроана- логовых преобразователей Ь, b и 11.

5

0

5

0

5

0

На интервале времени t

напряжение ив(,ГХ1 на выходе блока 1 выборки-хранения равно UQ - величине входного сигнала в момент времени t0, a напряжение U вмх 2на выходе блока 2 выборки-хранения равно нулю (U 86fx г - 0).

В течение интервала между моментами времени t0 и tv выходное напряжение Ugyxs блока 3 вычитания равно

ивих э иьях-г . (О

Напряжение иВЬ|ХЗпоступает через делитель 4 напряжения с коэффициентом передачи 0,5 на аналоговый вход умножающего цифроаналогового преобразователя 6. Выходное напряжение Ueb(X j умножающего цифроаналогового преобразователя 6 равно

U8bix 0,5UBtlX3Z 0,, 0,5 Uatlxat,(2)

где - масштабный коэффициент. Напряжение U8blx поступает на аналоговый вход умножающего цифроаналогового преобразователя 11, выходное напряжение UBblx 1T которого равно

Л

1Т t- U ВЫХ 11 U J U ВКХ Э L

(3)

и поступает на первый вход сумматора 7, на второй вход которого поступает напряжение U eux 5 с выхода умножающего цифроаналогового преобразователя 5, которое равно

50

11 вы 5 Ь «их г1

(4)

На третий вход сумматора 7 поступает напряжение U 8ЫК 0с выхода блока 10 выборки-хранения.

Выходное напряжение V flt|J( с выхода сумматора 7 равно

U.

ивь. и йшю,(Ь)

ВЫХ 1

а с учетом выражений (1-4)

,b

+ U

С вихГ11 etixi

6МХ 2

t + Ь в(,|х to ,

Напряжение Ueb(X 7поступает на выход 8 устройства и вход блока 9 выборки-хранения. При заполнении разрядов счетчика в момент времени t1 на выходе дешифратора 15 формируется положительный импульс длительностью 2 .который поступает на дифференцирующую цепь 16. В момент t положительного фронта на выходе последнего формируется короткий строб-импульс положительной полярности, который поступает через элементы 18 и 19 на управляющие входы выборки бло- ков 2 и 9 выборки-хранения соответственно . В период действия положительного строб-импульса в блок 2 выборки-хранения записывается выборка U1, поступающая с выхода блока I выборки-хранения . Одновременно в блоке 9 выборки-хранения записывается напряжение ишх t, поступающее с выхода сумматора 7.

В момент времени t, + Ј на выходе дифференцирующей цепи I6 формируется короткий строб-импульс отрицательной полярности, который через элементы I7 и 20 производит выборку входного сигнала U8x в момент времени t и его запись в блоке I выборки- хранения , одновременно выходное напряжение U

8ых 9

блока 9 выборки-хранения

записывается в блок Ю выборки-хране- ния и поступает на третий вход сумматора 7.

Следующим импульсом генератора 13 разряды счетчика 14 устанавливаются в нулевые состояния, процесс формирования цифрового кода Z(t) на входах умножающих цифроаналоговых преобразователей 5, 6 и 11 на интервале времени t, - t 2 - Тдискр происходит аналогично описанному процессу. На интер

вале

tv t выходные напряжения блоков 1, 2, 9 и 10 выборки-хранения равны соответственно URMX1 и,;

ио ибыхэ ивых о-ивы 7.1 , где 1, ,110 - значения дискретных выборок в моменты времени t,, 10, a Ue(,,X7,i результат интегрирования входного сигнала на интервале предыдущей выборки t о - t ,,

Выходное напряжение U xв каждом такте является интегралом входного

сигнала U

й

т.е.

(b)

ВЫ

; J uM(t),5(U.-Ui.1 )tz +

+ и

t +

с н,

(7)

где U. л U,

t-1

-. - Ч,

Ч -t;-,

дискретные значения (выборки) входного сигнала, взятые в моменты времени соответственно t: и причем т

-Лиск р

результат интегрирования, полученный после окочания предыдущего интервала дискретизации.

t-t

Формула изобретения

20

5

Аналого-цифровой интегратор, содержащий генератор счетных импульсов, выход которого соединен со счетным входом счетчика, выход которого

5 подключен к цифровому входу первого умножающего цифроаналогового преобразователя, отличающийся тем, что, с целью повышения точности интегрирования, в него введены втоQ Р°й и третий умножающие цифроаналого- вые преобразователи, первый, второй, третий и четвертый блоки выборки-хранения, дешифратор, дифференцирующая цепь, блок вычитания, делитель напряжения, сумматор, первый, второй, третий, четвертый и пятый элементы с односторонней проводимостью и инвертор, причем информационный вход первого блока выборки-хранения является

Q информационным входом интегратора, а

0

5

выход первого блока выборки-хранения соединен с информационным входом второго блока выборки-хранения и с первым входом блока вычитания, второй вход которого подключен к выходу второго блока выборки-хранения и аналоговому входу первого умножающего цифроаналогового преобразователя, выход блока вычитания через делитель напряжения подключен к аналоговому входу второго умножающего цифроаналогового преобразователя, выход которого соединен с аналоговым входом третьего умножающего цифроаналогового преобразователя, цифровые входы второго и третьего умножающих цифроаналого- вых преобразователей объединены и подключены к выходу счетчика и входу дешифратора, выход которого через диф71562936 8

ференцирующую цепь соединен с входамиключей к управляющему входу интегратопервого, второго, третьего и четвер- ра первый, второй и третий входы

того элементов с односторонней про-сумматора соединены соотве.тственно с

водимостыо, выходы которых подключенывыходами первого и третьего умножающих

к управляющим входам соответственноцифроаналоговых преобразователей и -с

первого, второго, третьего и четвер-выходом четвертого блока выборки-хратого блоков выборки-хранения, входнения, выход сумматора является выхообнуления счетчика через включенныедом интегратора и подключен к инпоследовательно инвертор и пятый эле- JQформационному входу третьего блока

мент с односторонней проводимостьювыборки-хранения, выход которого соесоединен с управляющим входом первогодинен с информационным входом четверблока выборки-хранения, а также под-того блока выборки-хранения.

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь угла поворота вала в код | 1989 |

|

SU1633492A1 |

| Экстраполятор | 1987 |

|

SU1515180A1 |

| Двухкоординатный преобразователь перемещения в код | 1988 |

|

SU1837390A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1985 |

|

SU1242801A1 |

| Преобразователь угла поворота вала в код | 1985 |

|

SU1293842A1 |

| Способ измерения времени установления выходного сигнала цифроаналоговых преобразователей и устройство для его осуществления | 1987 |

|

SU1494216A1 |

| Аналого-цифровой низкочастотный фазометр | 1990 |

|

SU1780042A1 |

| НИЗКОЧАСТОТНЫЙ ИЗМЕРИТЕЛЬ ФАЗОВОГО СДВИГА | 1992 |

|

RU2024028C1 |

| Экстраполятор | 1988 |

|

SU1564653A2 |

| Функциональный преобразователь нескольких переменных | 1986 |

|

SU1387022A1 |

Изобретение относится к автоматике и вычислительной технике, в частности к устройствам функционального преобразования сигналов, и может быть использовано для интегрирования входного электрического сигнала. Целью изобретения является повышение точности интегрирования. Аналого-цифровой интегратор содержит первый 1 и второй 2 блоки выборки-хранения, блок 3 вычитания, делитель 4 напряжения, первый 5 и второй 6 умножающие цифроаналоговые преобразователи, сумматор 7, выходную клемму 8, третий 9 и четвертый 10 блоки выборки-хранения, третий умножающий цифроаналоговый преобразователь 11, входную клемму 12, генератор 13 счетных импульсов, счетчик 14, дешифратор 15, дифференцирующую цепь 16, вентили 17 - 20 и 23, шину 21 управления и инвертор 22. За счет реализации данным устройством алгоритма, описываемого выражением UвыхI=Uвх(T) DT=0,5(UI-UI-1)T2+UI-1 T+CI-1, где UI и UI-1 - дискретные значения (выборки) входного сигнала, взятые в моменты времени соответственно TI и TI-1

CI-1 - результат интегрирования, полученный после окончания предыдущего интервала дискретизации, удается повысить точность интегрирования. 1 ил.

| Авторское свидетельство СССР № , кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аналого-цифровой интегратор | 1985 |

|

SU1277144A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-07—Публикация

1988-07-18—Подача