со 00

м

о

кэ

Изобретение относится к вычислительной технике и автоматике и может быть применено в гибридных вычислительных машинах и специализ:1рованнык системах управления для реализации произвольных функциональных зависимостей нескольких переменных.

Цель изобретения - повышение быстродействия.

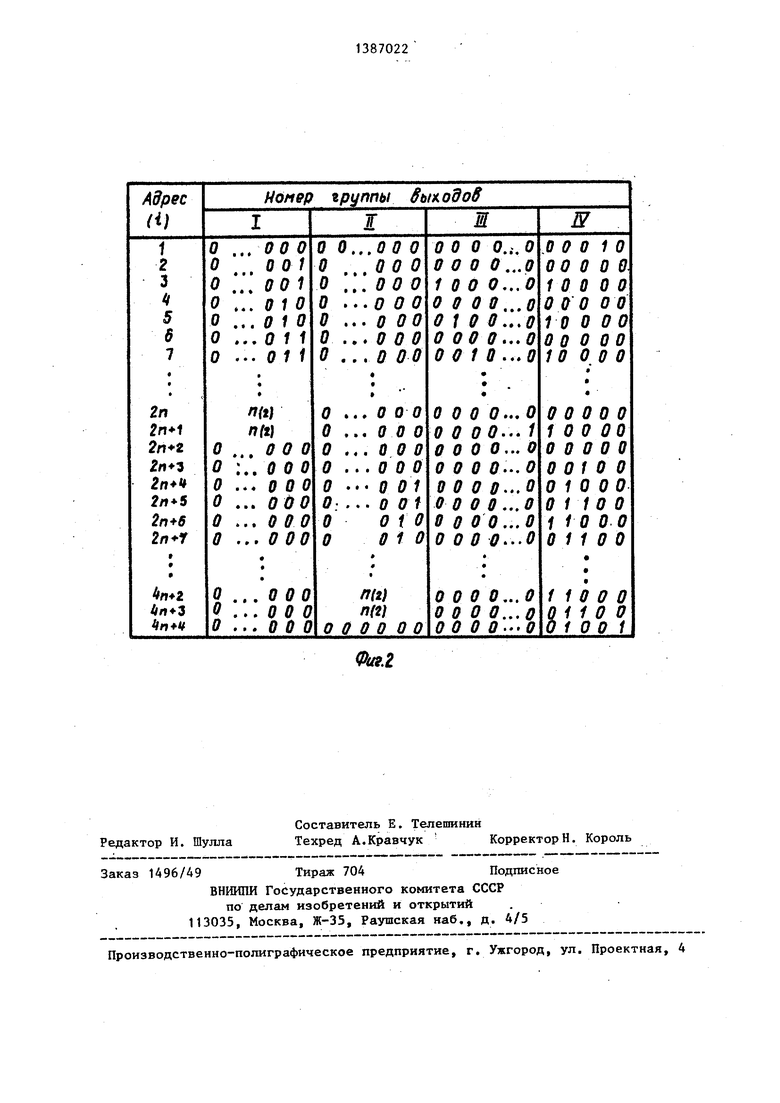

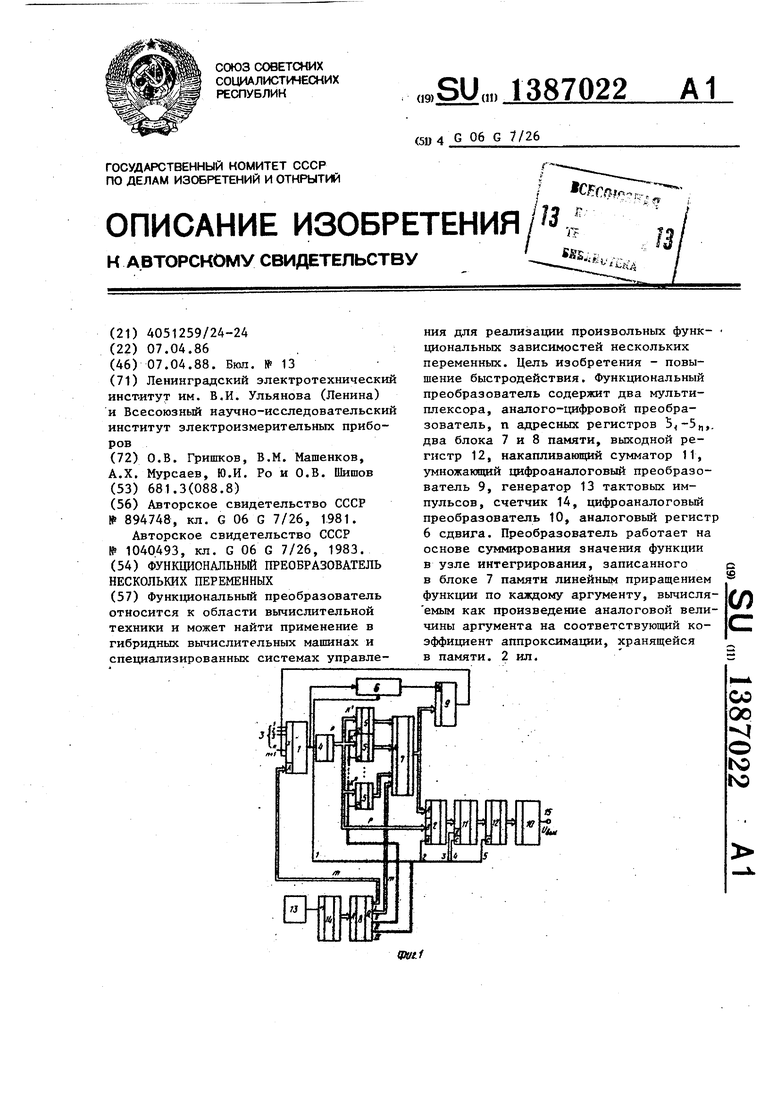

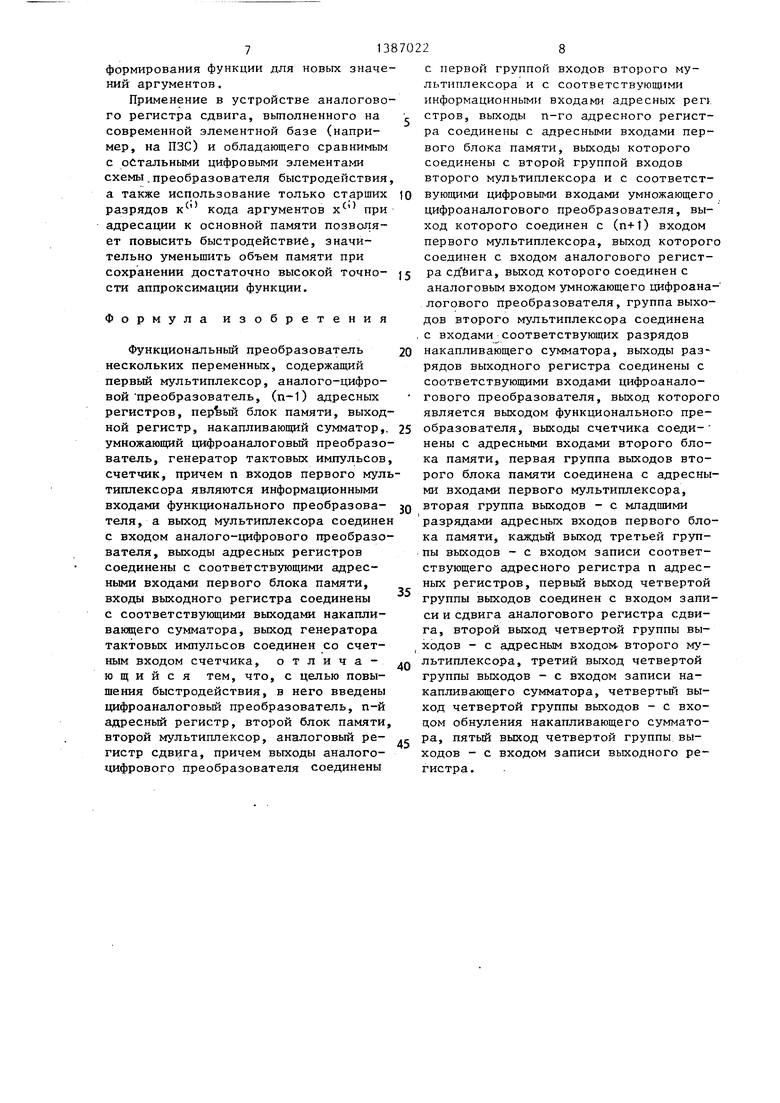

На фиг. 1 приведена структурная схема преобразователя; на фиг, 2 - таблица управля ющих кодов, записанных во втором блоке памяти.

Функциональный преобразователь не- скольких переменных содержит первый аналоговый 1 и второй цифровой 2 мультиплексоры, группу п информационных аналоговых входов 3, аналого-цифровой преобразователь (АЦП) 4, п адресных регистров 5,-5,, аналоговый регистр 6 сдвига, первый 7 и второй 8 блоки памяти два цифроаналоговых преобразователя (ДАЙ) 9 и 10, накапливающий сумматор 11, выходной регистр 12, гене ратор 13 тактовых импульсов, счетчик 14, аналоговый выход 15 преобразователя.

В первый блок 7 памяти записываютс значения функции и коэффициенты накло на кусочно-линейной аппроксимации по каждому аргументу в узлах интерполяции. Второй блок 8-памяти служит для формирования управляющих сигналов по Организации работы устройства. Запи- санные в нем коды приведены в таблице (фиг. 2). Разрядность первой и второй группы выходов второго блока 8 памяти равна m - ближайшему целому числу, большему значения , где п - число переменных функции, реализуемой устройством, разрядность третьей группы выходов второго блока памяти 8 равна п, разрядность четвертой группы выходов второго блока па- мяти равна пяти. В ячейках второго блока 8 памяти, -соответствующих разрядам первой группы выходов, записаны двоичные зквиваленты чисел

jENTa/2)

1о

при i ё (2п+1)

в противном случае

где i - адрес (порядковый номер) ячейки памяти второго блока памя-ее

NU:

ENT(i-2n-2)/2 при

4п+4

Ов остальных случаях

В ячейках, соответствующих разрядам третьей группы выходов, записаны нулевые коды во всех ячейках имеющих четные адреса, а также в ячейках с адресами, превьшающими (2п+1), в остальных ячейках этой группы выходов записана единица в разряде, номер

которого вычисляется как

а ).

0 5

0 с 0 5

е

в ячейках, соответствующих выходу первого разряда кода четвертой группы выходов второго блока 8 памяти, записана единица по всем нечетным адресам с третьего по (2пч-1) и по всем четным с (2п+6)- по (4п+2) , а по остальным адресам занесены нули.

В ячейках, соответствующих выходу второго разряда кода четвертой группы выходов, записана единица по всем ад7 ресам, начиная с (2п+4), а по остальным адресам - нуль.

В ячейках третьего разряда кода четвертой группы выходов второго блока 8 памяти единица записана по всем нечетным адресам, начиная с (2п+3), а по остальным адресам - нули.

В ячейках четвертого разряда кода четвертой группы выходов единица за-- писана только по первому адресу, в ячейках пятого разряда - только по последнему адресу, а по остальным адресам в ячейки этих разрядов записаны нули.

Устройство работает следующим образом.

Устройство производит вычисление функции п переменных с использованием ее кусочно-линейной аппроксимации с равномерным расположением узлов интерполяции по осям арг,,ументов х , где i - номер аргумента функции, ,п.

Всякая функция (x

0

/V tx«, ,

Х. ) в окрестности точки ei

xgj , . .., , где ej(i T7m) - номер участка аппроксимации по i-й оси. аргумента, п-мерного пространства кусочно-линейно аппроксимируется к виДУ.,-.,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для ввода аналоговых данных | 1986 |

|

SU1335972A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1985 |

|

SU1305851A1 |

| Цифровой функциональный преобразователь | 1989 |

|

SU1695321A1 |

| Универсальный цифровой преобразователь координат | 1980 |

|

SU924701A1 |

| Устройство для воспроизведения функций двух переменных | 1987 |

|

SU1517046A1 |

| Цифровой режекторный фильтр | 1988 |

|

SU1608786A1 |

| Гибридный функциональный преобразователь | 1984 |

|

SU1203546A2 |

| Гибридный функциональный преобразователь | 1987 |

|

SU1464180A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Передающее устройство адаптивной телеизмерительной системы | 1989 |

|

SU1679517A1 |

Функ1щональный преобразователь относится к области вычислительной техники и может найти применение в гибридных вычислительных машинах и специализированных системах управления для реализации произвольных функ- циональных зависимостей нескольких переменных. Цель изобретения - повышение быстродействия. Функциональный преобразователь содержит два мультиплексора, аналого-цифровой преобразователь, п адресных регистров ,, два блока 7 и 8 памяти, выходной регистр 12, накапливающий сумматор 11, умножающий цифроаналоговый преобразователь 9, генератор 13 тактовых импульсов, счетчик 14, цифроаналоговый преобразователь 10, аналоговый регистр 6 сдвига. Преобразователь работает на основе суммирования значения функции в узле интегрирования, записанного в блоке 7 памяти линейным приращением функции по каждому аргументу, вычисля- емым как произведение аналоговой величины аргумента на соответствующий коэффициент аппроксимации, хранящейся в памяти. 2 ил. сл

ти.

В ячейках, соответствуннцих, разрядам второй группы выходов, записаны двоичные эквиваленты чисел

(О

„(П .-«1 .... л J

.,...е„ ((xy:

- Сп

де f(x

e,,e.

31387022

C l

, вц лна чение функции в узле интерполяции; - коэффициент наклона аппроксимирующей функции по оси i-го аргуге е

с

г т ву сд си г ти ны

мента, зависящий от номеров участков аппроксимации & по каждой 0 оси аргумента.

Вьфажение (1) преобразуем к следующему виду, на основании которого функ.ционирует предлагаемое устройство:

ts

fcx ;;

х ; )

а

е,,....,е

,

.+а

би М

1, , ЕП

е,,....,еи

.(

..

(2)

где

(x

(1)

е,

.(1

. x-)f(xy

«1

. («

м

ху )-а- , X

ьпвч.ч,€и

01

-...-а

(11 С„..,е

,( е; :

„(I

В пятом такте по управляющему с налу с первого разряда четвертой группы выходов второго блока 8 пам ти напряжение U из первой ячейки

30 аналогового регистра 6 сдвига пере писывается во вторую, а в первую я йку записывается напряжение U . О новременно по управляющему сигналу второго разряда третьей группы вых

40

В функцион альном преобразователе переменные х задаются входными аналоговыми, напряжениями U . Каждый такто- )вын импульс с генератора 13 тактовых импульсов увеличивает на единицу выходной код счетчика 14, по которому определяется адрес управляющей информации, считываемой из второго блока 8 памяти и задаваемой на другие элемен- с дов второго блока 8 памяти старшие

ты устройства. Коэффициент пересчета -

счетчика 14 определяется числом тактов., необходимых для осуществления вьиисления функции п переменных, и равен (4п+4). Таким образом, после поступления на вход счетчика 14 числа импульсов, равного числу тактов работы устройства, выходной код счетчика 14 сбрасывается в нуль, что определяет цикличность работы устройства.

Рассмотрим один цикл работы устройства.

В первом такте работы устройства по управляющему сигналу с четвертого разряда четвертой группы выходов второго блока 8 памяти сумматор 11 обнуляется. Во втором такте на первой группе выходов второго блока 8 памяти, связанной с адресными входами первого мультиплексора 1, появляется код, определяющий передачу на выход первого мультиплексора напряжения и с первого входа группы входов 3 устройства - входа первого ар45

50

55

разряды кода АЦП 4 напряжения и запоминаются во втором адресном регистре 5.

Так повторяется п раз и к концу (2п+1)-го такта значения всех аргу ментов функции запоминаются в ячей ках аналогового регистра сдвига, п чем в п-й ячейке запоминается первь аргумент, а в первой - значение последнего аргумента. В каждом адрес регистре 5 с этого момента старшие разряды кеда АЦП 4 соответствующего ему аргумента.

Если число разрядов к каждого i-ro адресного регистра 5 выбрано таким, что значение равно числ участков аппроксимации вычисляемой функции по оси i-ro аргумента х то числовой эквивалент кода, записа ный в i-й адресный регистр, равен н меру участка аппроксимации 1; по iоси аргумента . При этом код на выходах всех адресных регистров 5 однозначено определяет необходимый

гумента .. Это напряжение поступает на вход АЦП 4, который преобразует его в двоичный код.

В третьем такте по управляющему сигналу с первого разряда четвертой

группы выходов второго блока 8 памяти напряжение u записывается в первую ячейку аналогового регистра 6 сдвига, одновременно по управляющему сигналу с первого разряда третьей группы выходов второго блока 8 памяти, связанной с входами записи адресных регистров 5, к старших разрядов

ts кода АЦП А запоминаются в первом адресном регистре 5,

В четвертом такте на первой группе выходов второго блока 8 памяти появляется код, управляющий переда20 чей на выход первого мультиплексора 1 напряжения u с второго входа группы входов устройства - вход второго аргумента . Это напряжение поступает на вход АЦП 4, который преобразу25 ет его в двоичный код.

В пятом такте по управляющему сигналу с первого разряда четвертой группы выходов второго блока 8 памяти напряжение U из первой ячейки

30 аналогового регистра 6 сдвига переписывается во вторую, а в первую ячейку записывается напряжение U . Одновременно по управляющему сигналу с второго разряда третьей группы выхос дов второго блока 8 памяти старшие

0

с дов второго блока 8 памяти старшие

-

5

0

5

разряды кода АЦП 4 напряжения и запоминаются во втором адресном регистре 5.

Так повторяется п раз и к концу (2п+1)-го такта значения всех аргументов функции запоминаются в ячейках аналогового регистра сдвига, причем в п-й ячейке запоминается первьй аргумент, а в первой - значение последнего аргумента. В каждом адресном регистре 5 с этого момента старшие разряды кеда АЦП 4 соответствующего ему аргумента.

Если число разрядов к каждого i-ro адресного регистра 5 выбрано таким, что значение равно числу участков аппроксимации вычисляемой функции по оси i-ro аргумента х , то числовой эквивалент кода, записанный в i-й адресный регистр, равен номеру участка аппроксимации 1; по iй оси аргумента . При этом код на выходах всех адресных регистров 5 однозначено определяет необходимый

1 ,

5

узел итерполяции { I,, 1, .. l 5iвычисляемой функции.

Для каждого узла интерполяции в первый блок 7 памяти занес .ны величи

ны

. («)

е,

,, X g) и 4 , X

rt. -t)

:Г )

t,n. Порядок выбора, этих величин из блока 7 памяти для .реализации вычислений по выражению (2) определяется последовательностью смены кодов второй группы выходов второго блока памяти. Таким образом, в следующем ()-м такте код с второй группы выходов второго блока 8 памяти определяет считывание из первого блока 7 памяти кода величины «(х / , ,,,,

.11/иЛ i 11

х, ,, . . ,, Xg ) ДЛЯ запомненного в регистрах 5 узла интерполяции. Одновременно сигнал второго разряда четвертой группы выходов второго блока 8 памяти, поступаю1дий на адресньй вход второго мультиплексора 2, определяет прохождение на выход второго мультиплексора 2 сигналов с его первой группы входов. Поэтому код из первого бло ка 7 памяти через второй мультиплексор 2 поступает на входы сумматора 11, где он суммируется с его содержимым в следующем (2п+3)-м такте по управляющему сигналу с третьего разря- да четвертой группы выходов второго блока 8 памяти, поступающему на вход записи суютатора 11. В первом такте работы устройства сумматор обнулен, поэтому в нем запоминается код велиЧ1-1НЫ.

В следующем (2п+4)-м такте код второй группы выходов второго блока 8 памяти определяет считывание из первого блока 7 памяти кода величи- ,,..,,е„ и передачу его на цифровые входы умножающего ДАЛ 9, в кото- ром этот код умножае Рся на напряжение и с выхода аналогового регист

ра 6 сдвига. Одновременно код первой группы выводов второго блока 8 памяти устана вливает передачу на выход первого мультиплексора 1 сигнала с (п+1)-го входа, таким образом, полученное произведение с выхода второго умножающего ЦАП 9 поступает на АЦП 4 и оцифровывается. Код с выходов АЦП 4 поступает на вторую группу входов второго мультиплексора 2 и под действием разрешения управляющего сиг нала с второго разряда четвертой группы выходов второго блока 8 памяти далее на сумматор 11,

В следуюг1,ем (2п+5)-м такте по управляющему сигналу с третьего разряда четвертой группы выходов второго блока 8 памяти этот код, равный произ- веденргю коэ{1зфициента аппроксимации а л {, на напряжение u , суммируь ,.«. (/rt

ется с содержимым сумматора 11.

В следующем (2п+6)-м такте код второй группы выходов второго блока б памяти определяет выборку из первого блока 7 памяти кода величины.а , одновременно по управляющему сигналу с первого разряда Четвертой группы выходов второго блока 8 памят и производится сдвиг напряжений, записанных в аналоговом регистре 6 сдвига, на одну ячейку вправо, таким образом в п-й ячейке оказывается напряжение

и

(г

поэтому на вход АЦП 4 с (n+D-r

входа первого, мультиплексора 1 поступает и преобразуется в код напряжение, величина которого равна произведению ,В еличины коэффициента аппроксимации а g на напряжение . Оцифрованное напряжение с выходов АДП 4 через второй г гультиплексор 2 поступает, на сумматор 11 и в следующем (2п+7)-м также суммируется с. его содержимым по управляющему сигналу с третьего разряда четвертой группы выходов второго блока 8 памяти.

В дальнейшем процесс формирования кодов произведений коэффициентов аппроксимации ai ,, на соответствующие

1 -ч „ ,. г,

им значения напряжении U и суммирования их в сумматоре 11 повторяется для всех остальных аргументов.

Таким образом, к концу (4п+3)-го такта в сумматоре 11 образуется код значения аппроксимирующей фу нкции

.(

в точке {X , ..., X

В (4п+4)-м такте по управляющему сигналу с пятого разряда четвертой группы выходов второго блока. 8 памяти, определяющего состояние входа записи выходного регистра, код суммы с выходов сумматора 11 записывается в выходной регистр 12 и далее поступает на цифровые входы ЦАП 10, на выходе которого образуется аналоговый сигнал, величина которого, равна значению искомой функции и который сохраняется неизменным до смены кода в выходном регистре 12 в следующем цикле преобразования.

После этого счетчик 14 обнуляется, с этого момента начинается новый цикл

XV )+. ..+ai о„ X

кц ... с,,,.,, к я

inl ,Лп) )

7138702

формирования функции для новых значений аргументов,

Применение в устройстве аналогового регистра сдвига, вьтолненного на современной элементной базе (например, на ПЗС) и обладающего сравнимым с остальными цифровыми элементами схемы,преобразователя быстродействия,

а также использование только старших разрядов к кода аргументов х при адресации к основной памяти позволяет повысить быстродействие, значительно уменьшить объем памяти при сохранении достаточно высокой точно- сти аппроксимации функции.

Формула изобретения

Функциональный преобразователь нескольких переменных, содержащий первый мультиплексор, аналого-цифровой преобразователь, (п-1) адресных регистров, перЪый блок памяти, выходной регистр, накапливающий сумматор,. 25 образователя, выходы счетчика соединены с адресными входами второго блока памяти, первая группа выходов второго блока памяти соединена с адресными входами первого мультиплексора, вторая группа выходов - с младшими разрядами адресных входов первого блока памяти, каждый выход третьей группы выходов - с входом записи соответствующего адресного регистра п адресных регистров, первый выход четвертой группы выходов соединен с входом записи и сдвига аналогового регистра сдвига, второй выход четвертой группы выходов - с адресным входом- второго мультиплексора, третий выход четвертой группы выходов - с входом записи накапливающего сумматора, четвертый выход четвертой группы выходов - с вхо- цом обнуления накапливающего сумматора, пятый выход четвертой группы выходов - с входом записи выходного регистра.

умножающий цифроаналоговьй преобразователь, генератор тактовых импульсов, счетчик, причем п входов первого мультиплексора являются информационными входами функционального преобразова- JQ теля, а выход мультиплексора соединен с входом аналого-цифрового преобразователя, выходы адресных регистров соединены с соответствующими адресными входами первого блока памяти, входы выходного регистра соединены с соответствующими выходами накапли- ванлцего сумматора, выход генератора тактовых импульсов соединен со счетным входом счетчика, отличающийся тем, что, с целью повышения быстродействия, в него введены цифроаналоговый преобразователь, п-й адресный регистр, второй блок памяти, второй мультиплексор, аналоговый регистр сдвига, причем выходы аналого- цифрового преобразователя соединены

35

40

45

с первой группон входов второго мультиплексора и с соответствующими информационными входами адресных peri стров, выходы п-го адресного регистра соединены с адресными входами первого блока памяти, выходы которого соединены с второй группой входов второго мультиплексора и с соответствующими цифровыми входами умножающего цифроаналогового преобразователя, выход которого соединен с (п+1) входом первого мультиплексора, выход которог соединен с входом аналогового регистра сд йига, выход которого соединен с аналоговым входом умножающего цифроаналогового преобразователя, группа выходов второго мультиплексора соединена с входами соответствующих разрядов накапливающего сумматора, выходы разрядов выходного регистра соединены с соответствующими входами цифроаналогового преобразователя, выход которого является выходом функционального преJQ

35

JQ

40

JQ

45

| Функциональный преобразователь | 1980 |

|

SU894748A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Вычислительное устройство | 1982 |

|

SU1040493A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-04-07—Подача