| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1987 |

|

SU1434458A1 |

| Измеритель интервальной скорости | 1980 |

|

SU911412A1 |

| Преобразователь напряжение-временной интервал | 1981 |

|

SU991605A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1420537A1 |

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

| Измеритель отношения энергий импульсных акустических сигналов | 1979 |

|

SU890314A1 |

| Интегрирующий аналого-цифровой преобразователь | 1985 |

|

SU1279069A1 |

| Способ определения входного сопротивления усилителя заряда и устройство для его осуществления | 1984 |

|

SU1205060A1 |

| Интегрирующий электрометр | 1982 |

|

SU1104426A1 |

| Перемножитель электрических сигналов | 1990 |

|

SU1820396A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для формирования аналогового сигнала, пропорционального интегралу от входного сигнала. Целью изобретения является повышение точности устройства. Устройство содержит операционный усилитель 1, интегрирующий конденсатор 2, запоминающие конденсаторы 3 и 4, ключи 5-9 на полевых транзисторах. Устройство оказывается практически нечувствительным к неравенству емкостей запоминающих конденсаторов, в нем практически отсутствует эффект накопления погрешности в процессе последовательного деления сигнала. 2 ил.

го

Изобретение относится к автоматике и вычислительной технике, предназначено для формирования аналогового сигнала, пропорционального .интегралу от входного сигнала, и может найти применение в аналоговых и гибридных вычислительных устройствах, а также в специализированных устройствах обработки информации.

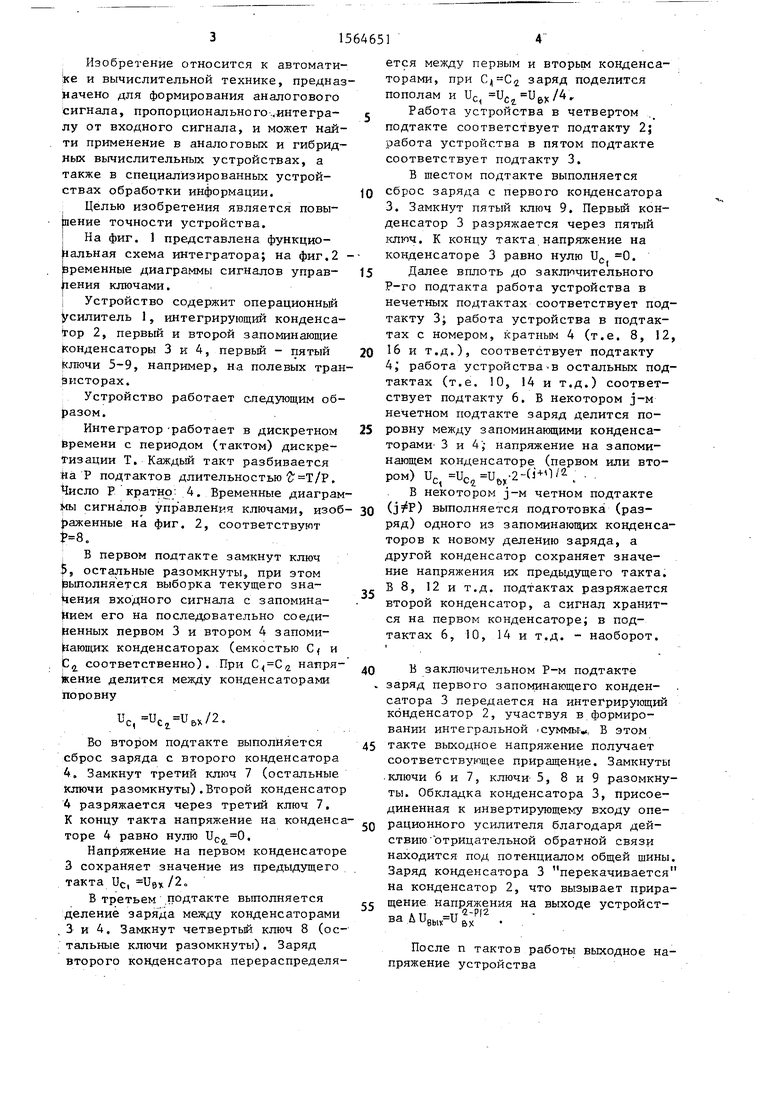

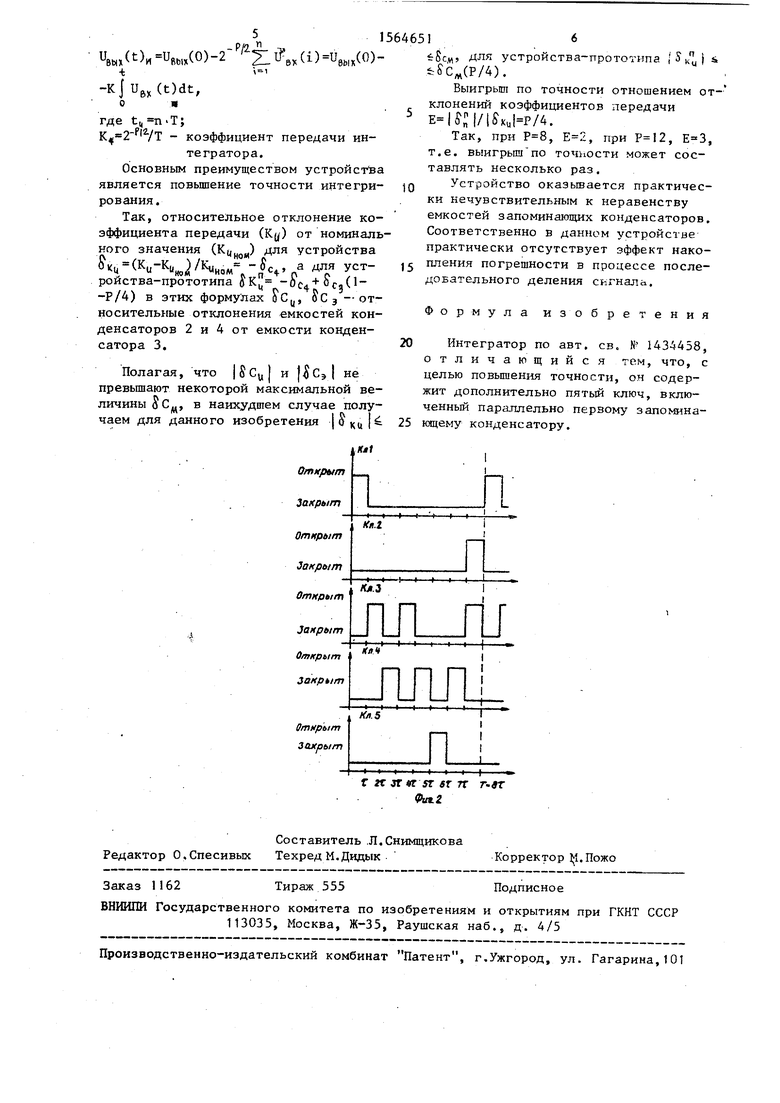

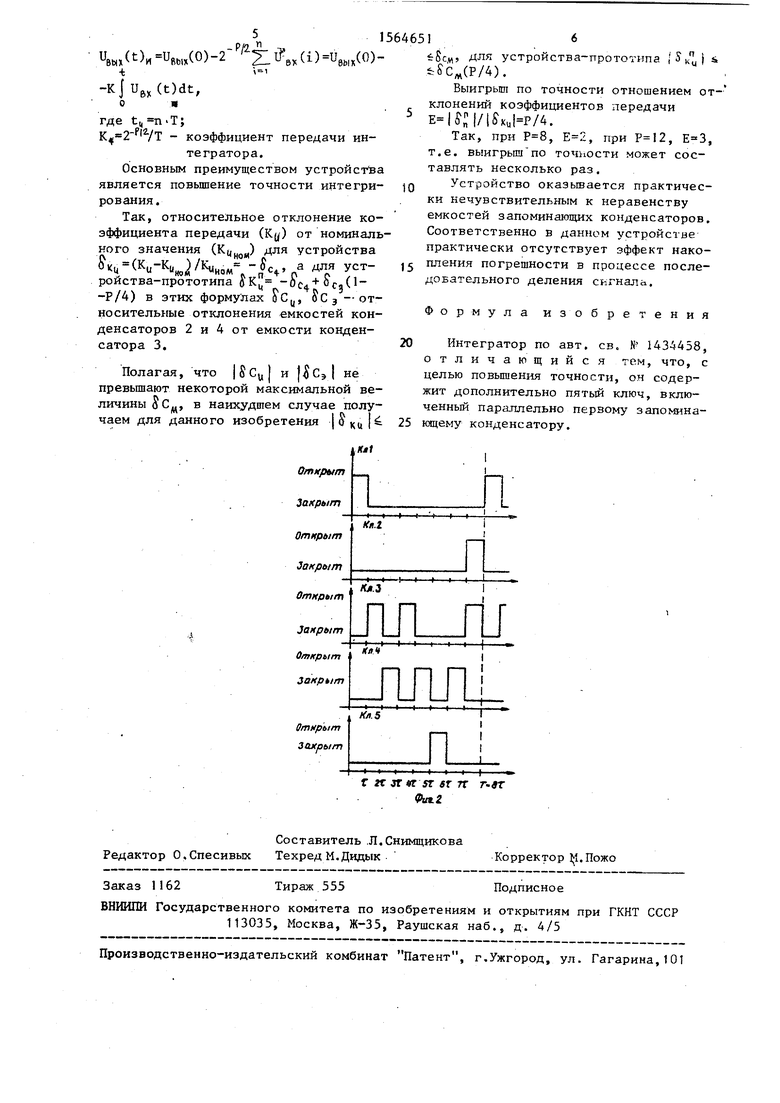

Целью изобретения является повы- Ьение точности устройства. 1 На фиг. 1 представлена функциональная схема интегратора; на фиг.2 - временные диаграммы сигналов управления ключами.

Устройство содержит операционный усилитель 1, интегрирующий конденсатор 2, первый и второй запоминающие конденсаторы 3 и 4, первый - пятый рогачи 5-9, например, на полевых транзисторах.

Устройство работает следующим образом.

Интегратор работает в дискретном бремени с периодом (тактом) дискретизации Т. Каждый такт разбивается На Р подтактов длительностью , %1сло Р кратно 4. Временные диаграммы сигналов управления ключами, изображенные на фиг. 2, соответствуют 8.

В первом подтакте замкнут ключ

Ј, остальные разомкнуты, при этом выполняется выборка текущего значения входного сигнала с запомина- )иием его на последовательно соеди- ренных первом 3 и втором 4 запоми- ающих конденсаторах (емкостью С( и Са соответственно). При напря- ение делится между конденсаторами поровну

Uc, иСг иьх/2.

Во втором подтакте выполняется сброс заряда с второго конденсатора 4. Замкнут третий ключ 7 (остальные ключи разомкнуты).Второй конденсатор 4 разряжается через третий ключ 7, К концу такта напряжение на конденсаторе 4 равно нулю .

Напряжение на первом конденсаторе 3 сохраняет значение из предыдущего такта UC| Ue /2„

В третьем подтакте выполняется деление заряда между конденсаторами 3 и 4. Замкнут четвертый ключ 8 (остальные ключи разомкнуты). Заряд второго конденсатора перераспределяется между первым и вторым конденсаторами, при заряд поделится пополам и Uc UC U&x/4r

Работа устройства в четвертом подтакте соответствует подтакту 2; работа устройства в пятом подтакте соответствует подтакту 3.

В шестом подтакте выполняется

сброс заряда с первого конденсатора 3. Замкнут пятый ключ 9. Первый конденсатор 3 разряжается через пятый ключ. К концу такта напряжение на конденсаторе 3 равно нулю Uc 0.

Далее вплоть до заключительного Р-го подтакта работа устройства в нечетных подтактах соответствует подтакту 3; работа устройства в подтактах с номером, кратным 4 (т.е. 8, 12,

16 и т.д.), соответствует подтакту 4; работа устройства.в остальных под- тактах (т.е. 10, 14 и т.д.) соответствует подтакту 6. В некотором j-м нечетном подтакте заряд делится поровну между запоминающими конденсаторами 3 и 4 , напряжение на запоминающем конденсаторе (первом или вто- ром) UCi-UCt-Uw.2-(i+ V.

В некотором j-м четном подтакте

() выполняется подготовка (разряд) одного из запоминающих конденсаторов к новому делению заряда, а другой конденсатор сохраняет значение напряжения их предыдущего такта. В 8, 12 и т.д. подтактах разряжается второй конденсатор, а сигнал хранится на первом конденсаторе; в подтактах 6, 10, 14 и т.д. - наоборот.

В заключительном Р-м подтакте . заряд первого запоминающего конденсатора 3 передается на интегрирующий конденсатор 2, участвуя в формировании интегральной суммы В этом

такте выходное напряжение получает соответствующее приращение. Замкнуты ключи 6 и 7, ключи 5, 8 и 9 разомкнуты. Обкладка конденсатора 3, присоединенная к инвертирующему входу операционного усилителя благодаря действию отрицательной обратной связи находится под потенциалом общей шины. Заряд конденсатора 3 перекачивается на конденсатор 2, что вызывает приращение напряжения на выходе устройст- ваЛивых и Р|2 .

После п тактов работы выходное напряжение устройства

и,

и

выи

5л1

(0)-2-P/VlT (i)Ufiblx(0)

-t

-Kju6x(t)dt,

оя

где .T;

К 2 Р|2/Т - коэффициент передачи интегратора.

Основным преимуществом устройства является повьшение точности интегрирования.

Так, относительное отклонение коэффициента передачи (К(/) от номинального значения (Кцне)|И) для устройства

Ц- ки-чЛ/Чо- - пс Ра ДТ Г

роиства-прототипа 6КМ -Oc4+°cj(l -Р/4) в этих формулах S Cy, $СЭ -относительные отклонения емкостей конденсаторов 2 и 4 от емкости конденсатора 3.

Полагая, что |§Си| и |$СЭ | не превышают некоторой максимальной величины $CW, в наихудшем случае получаем для данного изобретения QKU

Kit

Составитель Л.Снимщикова Редактор 0,Спесивых Техред М.ДидыкКорректор 1.Пожо

Заказ 1162

Тираж 555

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

0

5

5

0

Ј&см, для устройства-прототипа , $ к i s fr&CM(P/4).

Выигрыш по точности отношением от- клонений коэффициентов передачи .

Так, при , , при , , т.е. выигрыш по точности может составлять несколько раз.

Устройство оказывается практически нечувствительным к неравенству емкостей запоминающих конденсаторов. Соответственно в данном устройстве практически отсутствует эффект накопления погрешности в процессе последовательного деления сигнала,

Формула изобретения

Интегратор по авт. св„ N 1434458, отличающийся том, что, с целью повышения точности, оч содержит дополнительно пятый ключ, включенный параллельно первому запоминающему конденсатору.

г к зг т ST вг гг т-вт 9ut2

Подписное

| Интегратор | 1987 |

|

SU1434458A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-15—Публикация

1988-04-11—Подача