(Л

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Интегратор | 1988 |

|

SU1564651A2 |

| Функциональный преобразователь напряжения | 1986 |

|

SU1376108A1 |

| Интегратор | 1980 |

|

SU920756A1 |

| Операционный усилитель с периодической компенсацией смещения нуля | 1982 |

|

SU1024938A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU1015444A1 |

| Дискретно-аналоговая линия задержки | 1982 |

|

SU1115230A1 |

| Аналоговый интегратор | 1979 |

|

SU807326A1 |

| Интегратор | 1983 |

|

SU1088017A1 |

| Интегратор | 1985 |

|

SU1251112A1 |

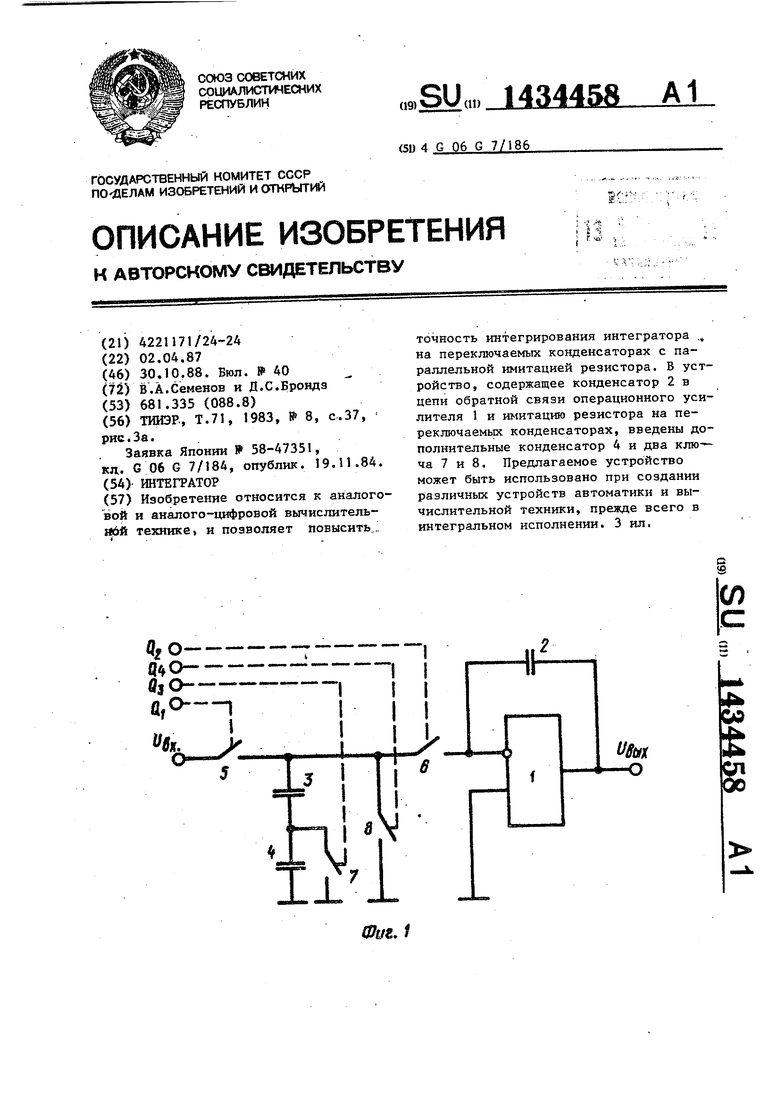

Изобретение относится к аналоговой и аналого-цифровой вычислитель- йбй технике и поэволяет повысить, точность интегрирования интегратора на переключаемых конденсаторах с параллельной имитацией резистора. В устройство, содержащее конденсатор 2 в цепи обратной связи операционного усилителя 1 и имитацию резистора на пе- реключаемьрс конденсаторах, введены дополнительные конденсатор 4 и два ключа 7 и 8. Предлагаемое устройство может быть использовано при создании различных устройств автоматики и вычислительной техники, прежде всего в интегральном исполнении. 3 ил.

4

СА

S

iPut. I

Изобретение относится к автом 1ти- ке и вычислительной технике, предназначено для формирования аналогового сигнала, пропорционального интег ралу от входного сигнала, и может найти применение в аналоговых и гибридных вычислительных устройствах, а также в специализированных устройствах обработки информации.

Целью изобретения является повышение точности интегрирования.

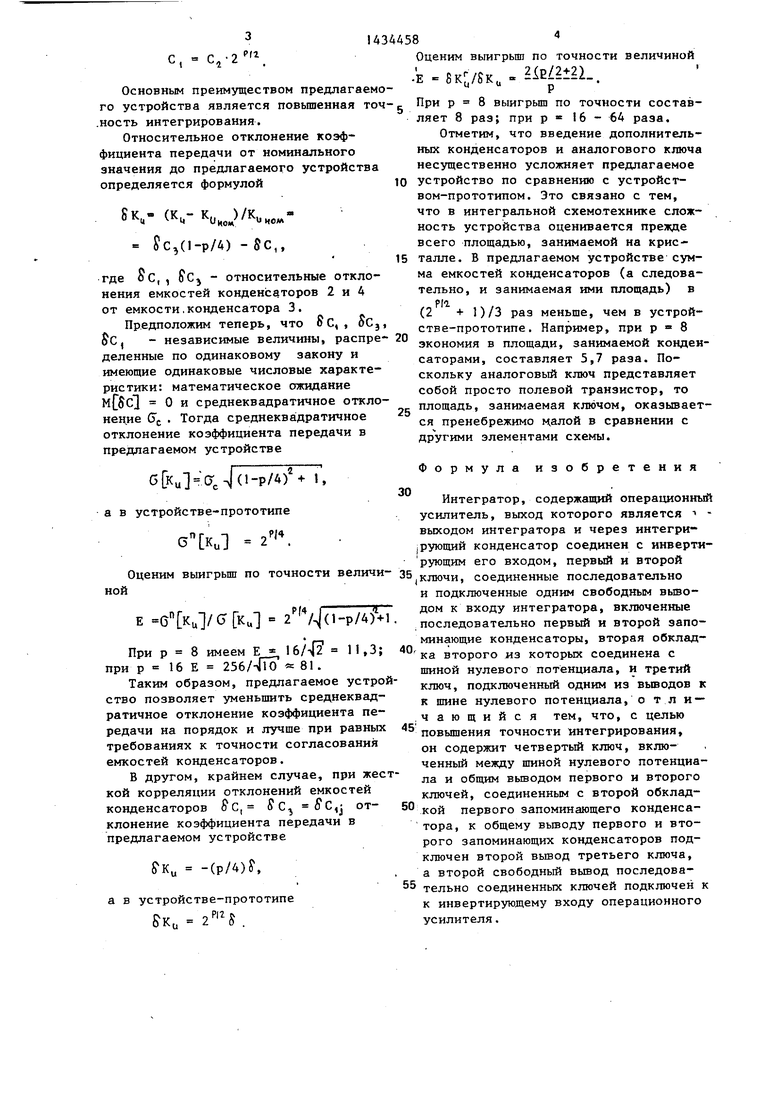

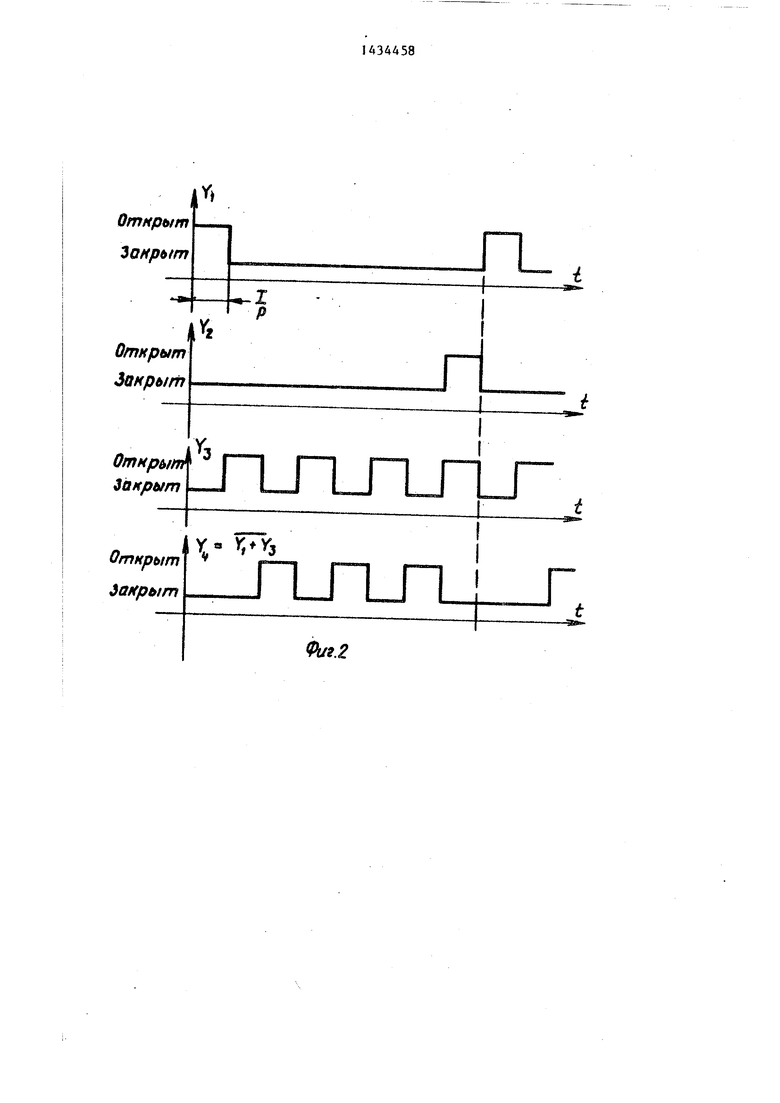

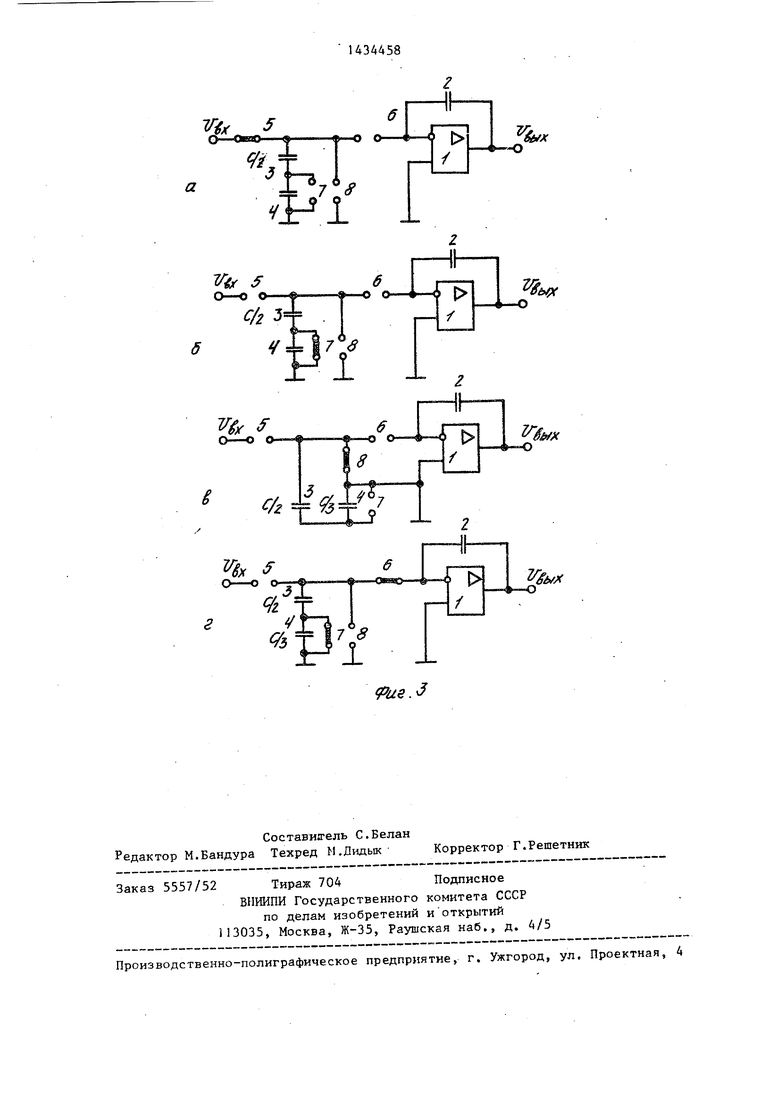

На фиг.1 представлена функциональная схема интегратора; на фиг.2 - временные диаграммы сигналов управ- ления ключами; на фиг.З - схемные конфигурации, возникающие на различных этапах работы предлагаемого устройства,.

Интегратор содержит операционный усилитель 1, интегрирующий конденсатор 2, первый и второй запоминающие конденсаторы 3 и 4, первый-четвер- тый ключи 5-8, например, на полевых транзисторах.

Интегратор работает в дискретном времени с периодом (TaKTOMj дискретизации Т. Каждый такт разбивается на р подтактов (р - четное), Временные диаграммы сигналов управления ключами, изображенные на фиг.2, соответствуют р 8.

В первом подтакте выполняется выборка текущего значения выходного сигнала с запоминанием его на последо вательно соединенных втором 3 и третьем 4 конденсаторах (С и С). Замкнут первый ключ 5 (остальные ключи разомкнуты) с образованием схемной конфигурции, изображенной на фиг,За. При С

и

Сг

напряжение на конденсаторе 3 Uex/2.

Во втором подтакте замкнут третий ключ 7 (остальные ключи разомкнуты) в образованием схемной конфигурации (см.фиг.36).Третий конденсатор 4 разряжается через открытый третий ключ 7. К концу такта напряжение на конденсаторе 4 равно нулю

и, О.

Напряжение на втором конденсаторе 3 сохраняет значение из предыдущего

такта 5

и

са

Uex/2.

Таким образом, в няется сброс заряда

В третьем подтакте осуществляется деление заряда между конденсаторами 3 и 4.

Замкнут четвертый ключ 8 (остальные ключи разомкнуты) с образованием схемной конфигурации (фиг.Зв). Заряд второго конденсатора 3 перераспределяется между вторым 3 и третьим

4 конденсаторами, делится пополам и

При

и,

С2

Си Ur.

С J заряд - Ue,/4.

Далее вплоть до заключительного р-го подтакта работа устройства в четных подтактах соответствует под- такту 2, а в нечетных - подтакту 3. При этом в некотором j-м нечетном подтакте заряд делится поровну между конденсаторами 3 и А. Напряжение на конденсаторе 2 к концу такта

и,

Сг

и,

с

и

,-{j+i)/

6)

В некотором J-M четном подтакте () выполняется подготовка (разряд) конденсатора 3 к новому делению заряда, а конденсатор 2 сохраняет значение напряжения из предыдущего такта.

I

В заключительном р-м подтакте заряд конденсатора 3 передается на конденсатор 2, участвуя в формировании интегральной суммы, В этом такте выходное напряжение получает соответствующее приращение.

Замкнуты ключи 6 и 7, кхпочи 3 и 8 разомкнуты. При этом образуется схемная конфигурацияJ изображенная на фиг.3г. Обкладка конденсатора 3, присоединенная к инвертирующему входу операционного усилителя, благодаря действию орицатёльной обратной связи находится под потенциалом общей гаи- s

5

ны. Заряд конденсатора 3

tt

перекачивается на конденсатор 2, что вызывает приращение напряжения на выходе устройства

--Р/

и

БЫХ

и

в«

50

Таким образом, коэффициент передачи предлагаемого интегратора описывается выражением (при С, С С,)

К,

-Р/1/Т

в устройстве-прототипе для обеспечения коэффициента передачи интегратора той же величины необходимо иметь

с.-2

p(i

Основным преимуществом предлагаемого устройства является повышенная том-с .ность интегрирования.

Относительное отклонение коэффициента передачи от номинального значения до предлагаемого устройства определяется формулой

10

15

8 к,- (к,- к

)/к„

и но/ « ИОДА

Jc,(i-pM) - Sc,,

где Sc,, - относительные отклонения емкостей конденсаторов 2 и А от емкости.конденсатора 3.

Предположим теперь, что Sc, , OCj,

Отметим, что введение дополнитель- иых конденсаторов и аналогового ключа несущественно усложняет предлагаемое устройство по сравнению с устройством-прототипом. Это связано с тем, что в интегральной схемотехнике сложность устройства оценивается прежде всего площадью, занимаемой на крис- 15 талле. В предлагаемом устройстве сумма емкостей конденсаторов (а следовательно, и занимаемая ими площадь) в

PI i

(2 + 1)/3 раз меньше, чем в устройстве-прототипе. Например, при р 8

л k- 1 о с 1U 1 П11С . IdllpiUnCp, iipn р о

SC, - независимые величины, распре- 20 экономия в площади, занимаемой конденделенные по одинаковому закону и имеющие одинаковые числовые характеристики: математическое ожидание О и среднеквадратичное отклонение . . Тогда среднеква:дратичное отклонеиие коэффициента передачи в предлагаемом устройстве

саторами, составляет 5,7 раза. Поскольку аналоговый ключ представляет собой просто полевой транзистор, то 2с площадь, занимаемая ключом, оказывается пренебрежимо налой в сравнении с дpVгими элементами схемы.

а в устройстве-прототипе

Интегратор, содержащий операцион усилитель, выход которого является выходом интегратора и через интегри рующий конденсатор соединен с инвер рующим его входом, первый и второй

ной

Оценим выигрьщ по точности величи- 35 ключи, соединенные последовательно

и подключенные одним свободным выво дом к входу интегратора, включенные последовательно первый и второй зап минающие конденсаторы, вторая обкла ка второго из которых соединена с щиной нулевого потенциала, и третий ключ, подключенный одним из выводов к шине нулевого потенциала, о т л и чающийся тем, что, с целью повышения точности интегрирования, он содержит четвертый ключ, включенный между шиной нулевого потенци ла и общим вьшодом первого и второг ключей, соединенным с второй обклад кой первого запоминающего конденса тора, к общему вьшоду первого и вто рого запоминающих конденсаторов под ключен второй вьшод третьего ключа, а второй свободный вывод последова- 55 тельно соединенных ключей подключен к инвертирующему входу операционног усилителя.

Е , (1-р/4)1

При р 8 имеем Е « 16/-( 11,3; при р 16 Е 256/-Ло «: 81 .

Таким образом, предлагаемое устройство позволяет уменьшить среднеквадратичное отклонение коэффициента передачи на порядок и лучше при равных требованиях к точности согласования емкостей конденсаторов.

В другом, крайнем случае, при жесткой корреляции отклонений емкостей конденсаторов &С, Sc ,j отклонение коэффициента передачи в предлагаемом устройстве

S KU -(p/4)S,

а в устройстве-прототипе

&К, 2

.т

моом-с

1А34458

Оценим выигрьш по точности ;E., .21

При р 8 выигрьпп по точности составляет 8 раз; при р 16-64 раза.

Отметим, что введение дополнитель- иых конденсаторов и аналогового ключа несущественно усложняет предлагаемое устройство по сравнению с устройством-прототипом. Это связано с тем, что в интегральной схемотехнике сложность устройства оценивается прежде всего площадью, занимаемой на крис- талле. В предлагаемом устройстве сумма емкостей конденсаторов (а следовательно, и занимаемая ими площадь) в

PI i

(2 + 1)/3 раз меньше, чем в устройстве-прототипе. Например, при р 8

k- 1 о с 1U 1 П11С . IdllpiUnCp, iipn р о

экономия в площади, занимаемой конденсаторами, составляет 5,7 раза. Поскольку аналоговый ключ представляет собой просто полевой транзистор, то площадь, занимаемая ключом, оказывается пренебрежимо налой в сравнении с дpVгими элементами схемы.

30

Формула изобретения

Интегратор, содержащий операционный усилитель, выход которого является - выходом интегратора и через интегрирующий конденсатор соединен с инвертирующим его входом, первый и второй

35 ключи, соединенные последовательно

0,

5

и подключенные одним свободным выводом к входу интегратора, включенные последовательно первый и второй запоминающие конденсаторы, вторая обкладка второго из которых соединена с щиной нулевого потенциала, и третий ключ, подключенный одним из выводов к к шине нулевого потенциала, о т л и - чающийся тем, что, с целью повышения точности интегрирования, он содержит четвертый ключ, включенный между шиной нулевого потенциала и общим вьшодом первого и второго ключей, соединенным с второй обкладкой первого запоминающего конденсатора, к общему вьшоду первого и второго запоминающих конденсаторов подключен второй вьшод третьего ключа, а второй свободный вывод последова- 5 тельно соединенных ключей подключен к к инвертирующему входу операционного усилителя.

0

| ТИЮР., Т.71, 1983, № 8, с.37, рис.За | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

1988-10-30—Публикация

1987-04-02—Подача