Изобретение относится к вычислительной технике, в частности к устройствам управления обменом информации, и может быть использовано для дог гупа нескольких источников к общему ресурсу.

Цель изобретения - расширение области применения устройства путем обеспечения возможности его работы в системах обмена с общим ресурсом, цикл обмена с которыми состоит из двух операций.

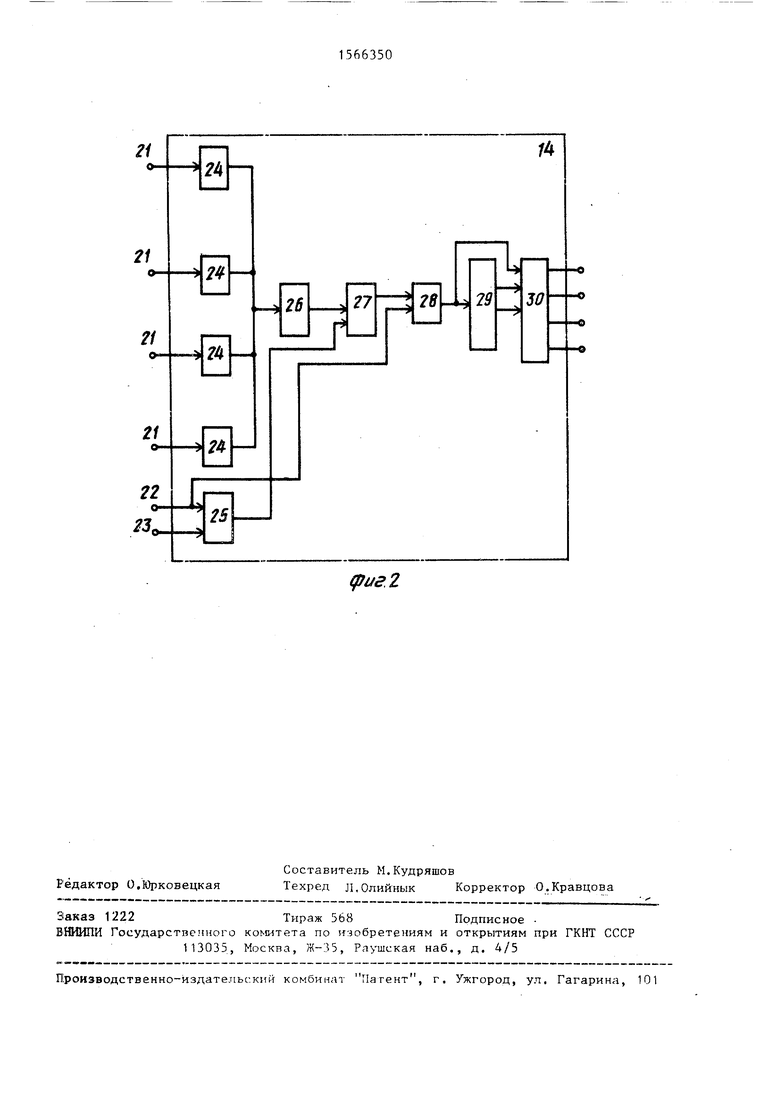

На фиг.1 показана схема устройства приоритета; на фиг.2 - схема бло- ка приоритета.

Устройство приоритета содержит каналы 1 , содержащие каждый элемент И-ИЛИ 2 триггеры 3 и 4, элемент ИЛИ 5, триггер 6, элементы 7 и 8 задержки, эле- мент И°9, триггер 10, элемент И 11, триггер 12, элемент ИЛИ 13. Устройство также содержит блок 14 приоритета, входы 15 запросов, входы 16 начальной установки, входы 17 запуска, от- ветные входы 18, входы 19 опроса, входы 20 разрешения записи, выходы 21 и тактовые входы 22 и 23.

Блок приоритета содержит передатчики 24, элемент И 25, приемник 26, триггер 27, элемент И-НЕ 28, дешифратор 30,

Устройство приоритета работает следующим образом.

В исходном состоянии после включения питания по сигналу начального установа, поступающему на входы 16 устройства, триггеры 3,4,6,10 и 12 устанавливаются в нулевое состояние. Так как триггер 12 устанавливается в нулевое состояние, то выходы передатчиков 24 блока приоритета в исход -ном состоянии находятся в единичном состоянии. На входах 22 и 23 устрой- ства присутствуют тактовые частоты. На информационном входе триггера 27 в исходном состоянии - логический нуль, а значит, триггер 27 блокировки также в нулевом состоянии. Это приводит к тому, что на выходе элемента И-НЕ 28 присутствует тактовая частота с входа 22, так как на перво входе элемента И-НЕ 28 присутствует сигнал с инверсного выхода триггера 27, Таким образом, в исходном состоянии на выходах блока 14 приоритета присутствуют сигналы опроса каналов 1 .

,.

0

5

Предположим, что одновременно на два канала поступает сигнал запроса (на входы 15 устройства).

Запросы поступают на установочный вход триггера 6. Значит, два триггера 6 в каналах устанавливаются по сигналам запроса в единичное состояние. На входы 17 должна быть подана логическая единица. Тогда по переднему фронту сигнала опроса с первого выхода дешифратора 30 устанавливается в единичное состояние сначала триггер 12 первого канала.„

После того, как установится в единичное состояние триггер 12 первого канала, на информационном входе триггера 27 устанавливается логическая единица, а затем по сигналу тактовых частот с выхода элемента И 25 триггер 27 устанавливается в единичное состояние. Инверсный выход триггера 27 запрещает прохождение тактовой частоты на выход элемента И-НЕ 28, а значит, на соответствующем выходе блока 14 устанавливается единичное состояние, а счетчик 29 устанавливается в следующее состояние. После этого на соответствующий выход 21 выдается сигнал разрешения работы с общим ресурсом.

В конце выполнения каждой функции на входе 18 присутствует сигнал о завершении функции.

Триггер 10 устанавливается в еди- . ничное состояние только после окончания выполнения второй функции, так как триггер 3 устанавливается в единичное состояние только по приходу сигнала с входа 19.

После того, как установится в единичное состояние триггер 10, на выходе элемента И 11 формируется импульс, который через элемент ИЛИ 13 поступает на вход сброса триггеров 12. Триггеры 12 и 3 первого канала устанавливаются в нулевое состояние. На тактовой частоте устанавливается в нулевое состояние триггер 27, так как на первом присутствует логический нуль. После этого на втором выходе блока 14 формируется импульс, который теперь уже устанавливает триггер 12 второго канала в единичное состояние. Далее устройство работает аналогичное

Ф о р м v т а и з о Ci р е т е н и я

1. Устройство приоритета содержащее блок приоритета, каналы, а в каждом каначе - два триггера и два элемента И, причем каждый запросный вход устройства соединен с единичным входом триггера одноименного канала, прямые выходы триггеров каналов соединены с информационными входами блока приоритета, каждьи выход группы выходов которого соединен с первым входом первого элемента И одноименного канала, выход первого элемента И каждого канала соединен с тактовым входом второго триггера своего канала, отличающееся тем что, с целью расширения области применения устройства путем обеспечения возможности его работы в системах обмена с общим ресурсом, цикл обмена с которыми состоит из двух операций, устройство содержит в каждом канале третий, четвертый, пятый триггеры, два элемента задержки, и три элемента ИЛИ, причем инверсный выход второго триггера в каждом канале соединен через первый элемент задержки

10

15

20

25

вого элемента ИЛИ г вот о каь левой вход пятого трш гера к канала соединен с одноименны ным входом устройства, едини ды третьего и четвертого три каждого канала соединены соо венно с одноименными входом входом разрешения записи уст второй вход первого элемента го канала соединен с одноим дом запуска устройства, еди ход первого триггера каждог соединен с единичным входом триггера своего канала, выхо рых триггеров каналов являют дами устройства, первый и вт товые входы устройства соед ветственно с первым и вторым выми входами блока приорите вой вход первого триггера со с выходом первого элемента И канала.

2. Устройство по п.1, о т ю щ е е с я тем, что блок п содержит группу передатчиков ник, триггер, элемент И, эне

с первым входом первого элемента ИЛИ, 30 счетчик и дешифратор,

второй вход которого соединен с одноименным входом начальной установки устройства и с первым входом второго элемента ИЛИ своего канала, выход которого соединен с входами сброса второго, третьего и четвертого триггеров своего канала, выходы которых соединены соответственно с первым и вторым входами третьего элемента ИЛИ своего канала, выход которого через второй элемент задержки соединен с первым входом второго элемента И своего канала, выход которого соединен с вторым входом второго элемента ИЛИ своего канала, второй вход второго элемента И соединен с выходом пятого триггера своего канала, единичный вход которого соединен с выходом пер0

5

0

5

вого элемента ИЛИ г вот о каь.т;,, нулевой вход пятого трш гера каждш о канала соединен с одноименным от ватным входом устройства, единичные в о- ды третьего и четвертого триггеров каждого канала соединены соответственно с одноименными входом опроса и входом разрешения записи устройства, второй вход первого элемента И каждого канала соединен с одноименным входом запуска устройства, единичный выход первого триггера каждого канала соединен с единичным входом второго триггера своего канала, выходы вторых триггеров каналов являются выходами устройства, первый и второй тактовые входы устройства соединены соответственно с первым и вторым тактовыми входами блока приоритета, лучевой вход первого триггера соединен с выходом первого элемента ИЛИ cRoeio канала.

2. Устройство по п.1, о т п и ч а- ю щ е е с я тем, что блок приоритет л содержит группу передатчиков, приемник, триггер, элемент И, эне.мент

выходы

5

0

5 которого являются выходами бпокл, входы которого соединены с входами передатчиков группы, выходы которых объединены и соединены с входами приемника, выход которого соединен с единичным входом триггера, выхоц торого соединен с первым ьходом элемента И-НЕ, выход которого соединен со счетным входом счетчика и г управляющим входом дешифратора, информационные входы которого соединены с выходами счетчика, первый и второй тактовые входы блока соединены г первым и вторым входами элемента И, выход которого соединен с входом сброса триггера, первый тактоинп вход Спока соединен с вторым входом элемента И-НЕ.

фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство переменного приоритета | 1986 |

|

SU1411747A1 |

| Устройство приоритета | 1982 |

|

SU1128254A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1988 |

|

SU1594551A1 |

| Многоканальное устройство для обслуживания запросов со сменными кодами приоритетов | 1986 |

|

SU1336005A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072047A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Матричный коммутатор | 1991 |

|

SU1800605A1 |

| Многоканальное устройство для подключения абонентов к общей магистрали | 1982 |

|

SU1072046A1 |

| Устройство для выбора по приоритету | 1989 |

|

SU1619274A1 |

| Устройство переменного приоритета | 1986 |

|

SU1319033A1 |

Изобретение относится к вычислительной технике, в частности к устройствам управления обменом информации, и может быть использовано для доступа нескольких источников к общему ресурсу. Цель изобретения - расширение области применения устройства путем обеспечения возможности его работы в системах обмена с общим ресурсом, цикл обмена с которыми состоит из двух операций. Устройство содержит блок 14 приоритета, а в каждом канале 1 - элементы ИЛИ 2, 5, 13, триггеры 3, 4, 6, 10, 12, элементы задержки 7, 8, элементы И 9, 11. Изобретение позволяет создавать мультимикропроцессорные системы с общим ресурсом памяти за счет введения в устройство схемы приоритета. При этом запросы обслуживаются не по жесткому приоритету, а по мере их поступления. При этом в устройстве формируются на выходе сигналы опроса, распределенные во времени, что позволяет устранить срабатывание двух или более каналов одновременно. 1 з.п. ф-лы, 2 ил.

| Устройство приоритета | 1982 |

|

SU1049909A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР f | |||

| Устройство приоритета | 1985 |

|

SU1315976A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-05-23—Публикация

1988-07-18—Подача