(Л

С

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения каналов ЭВМ с периферийными устройствами | 1990 |

|

SU1732348A1 |

| Устройство для обмена данными между ЭВМ и периферийным устройством | 1987 |

|

SU1605240A1 |

| Устройство контроля электропитания процессора | 1984 |

|

SU1188741A1 |

| Устройство для сопряжения группы каналов ЭВМ с группой периферийных устройств | 1987 |

|

SU1520529A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1990 |

|

SU1837305A1 |

| Устройство для сбора данных о работе ЭВМ | 1982 |

|

SU1121679A1 |

| Устройство для сопряжения процессора с устройством ввода-вывода | 1984 |

|

SU1180911A1 |

| Устройство для сопряжения магистрали ЭВМ с периферийными устройствами | 1990 |

|

SU1751775A1 |

| Устройство для обмена данными между оперативной памятью и периферийными устройствами | 1987 |

|

SU1587521A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1986 |

|

SU1403069A1 |

Изобретение относится к вычислительной технике и может быть использовано для подключения удаленных периферийных устройств к каналам вычислительных систем. Целью изобретения является повышение быстродействия. Устройство содержит блок управления опросом блок управления передачей информации, блок сдвиговых регистров, блок запросов, мультиплексор, блок приемопередатчиков, группу блоков хранения информации, группу блоков выделения маркера, группу блоков восстановления сигналов, группу блоков приемников и группу блоков передатчиков. 4 з.п. ф-лы. 9 ил.

Изобретение относится к вычислительной технике и может быть использовано дпя подключения удаленных периферийных устройств (ПФУ) к каналам вычислительных систем.

Цель изобретения - повьшение быстродействия установления связи между каналами ЭВМ и ПФУ.

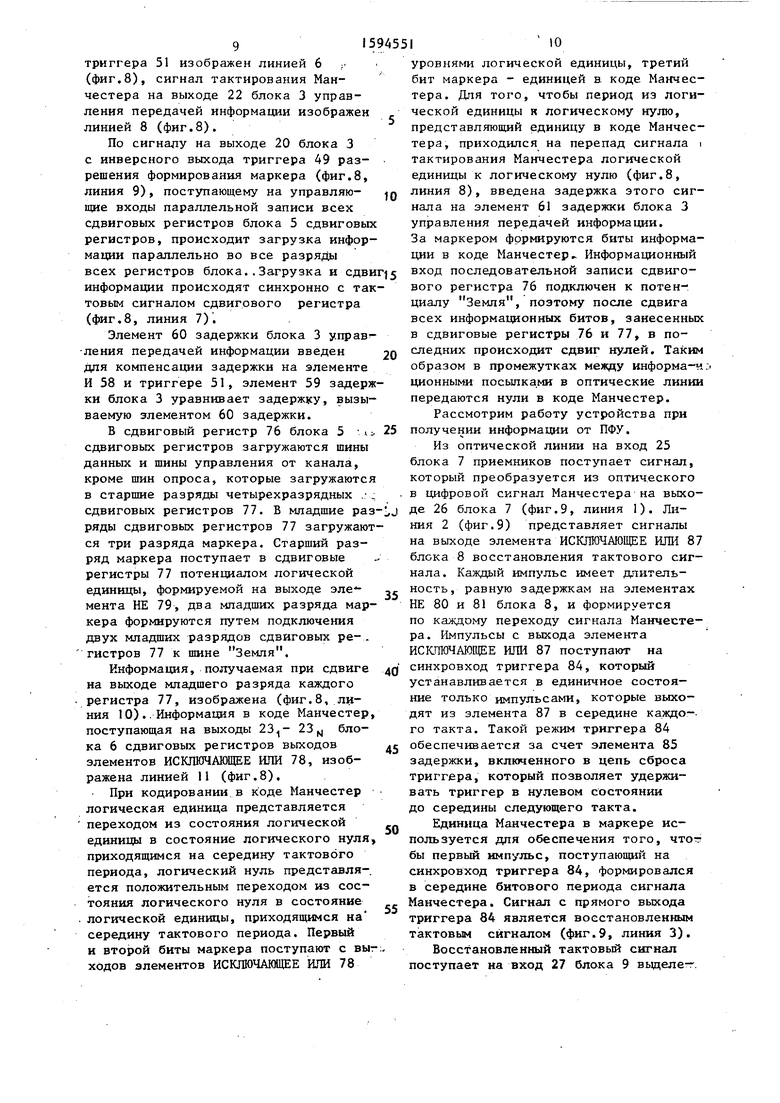

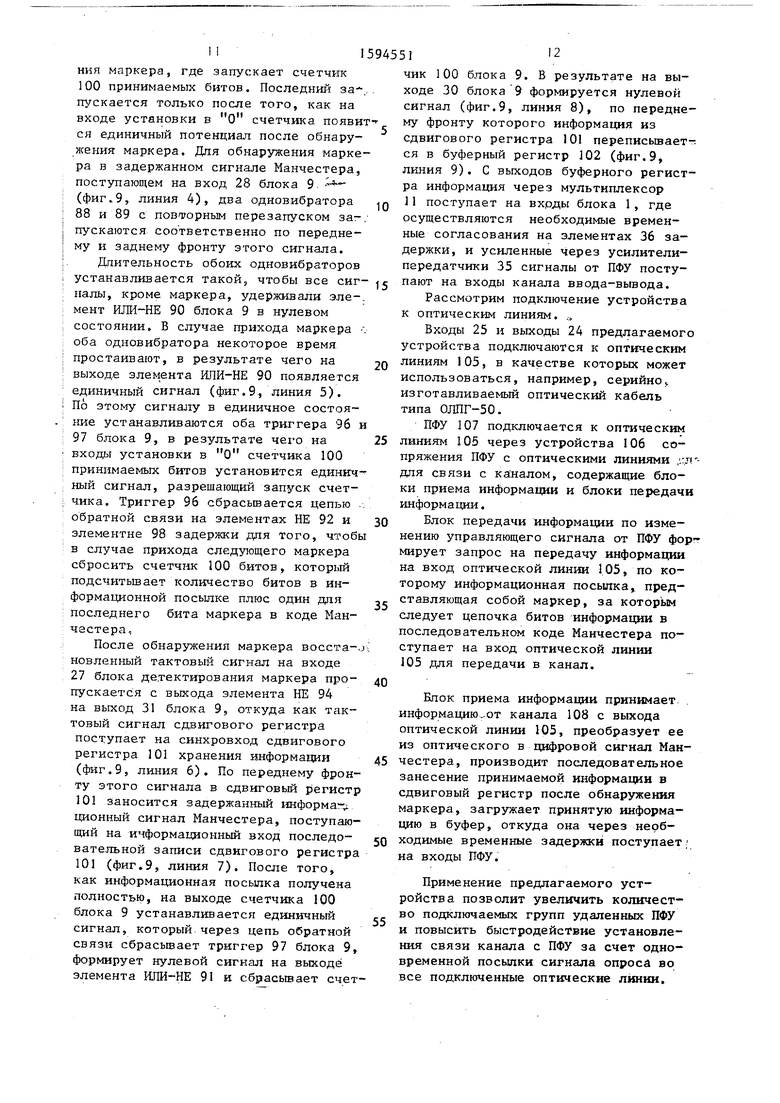

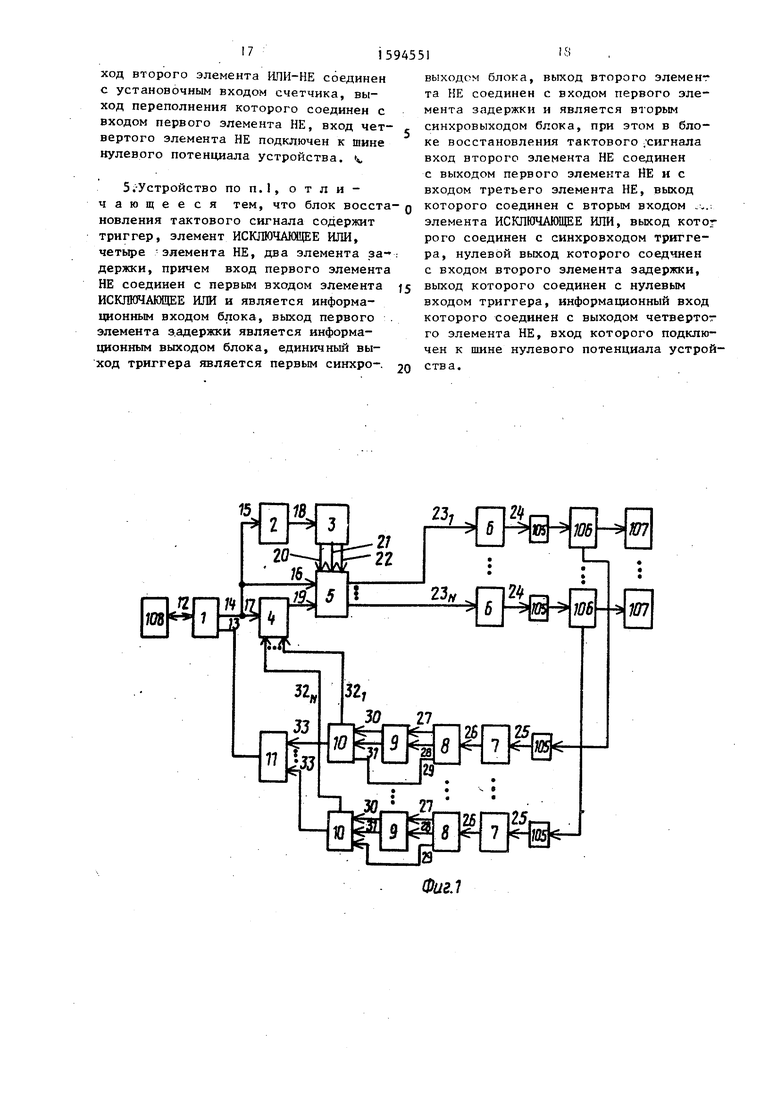

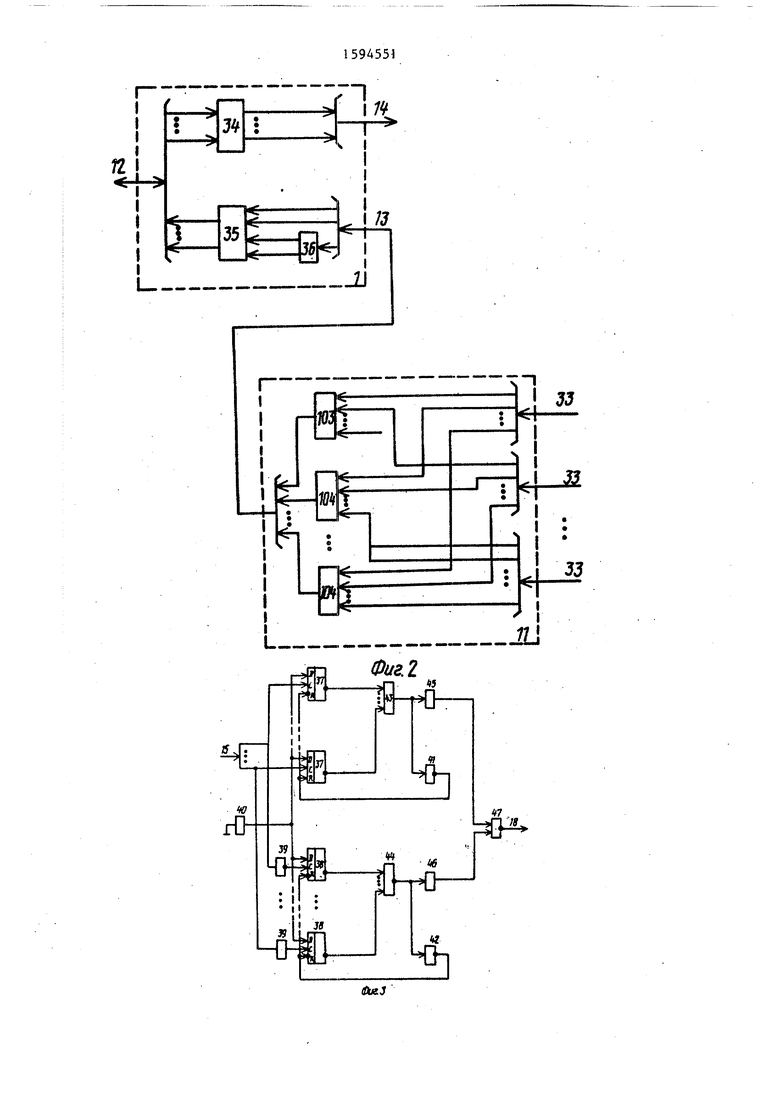

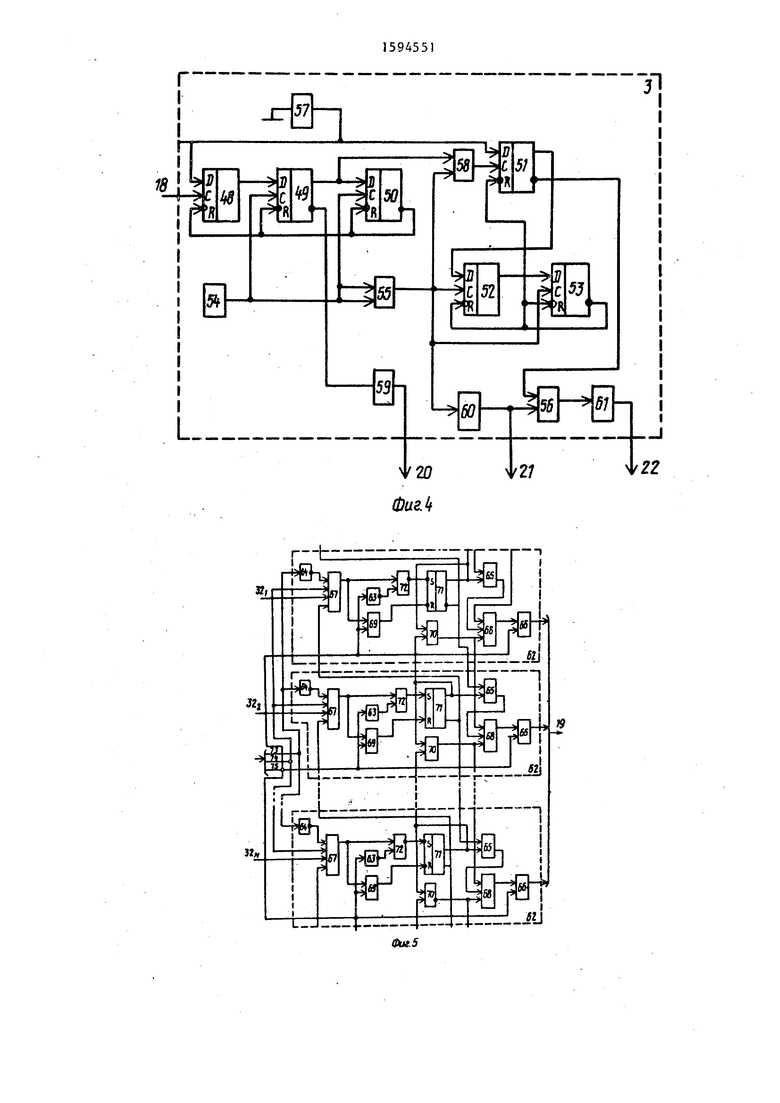

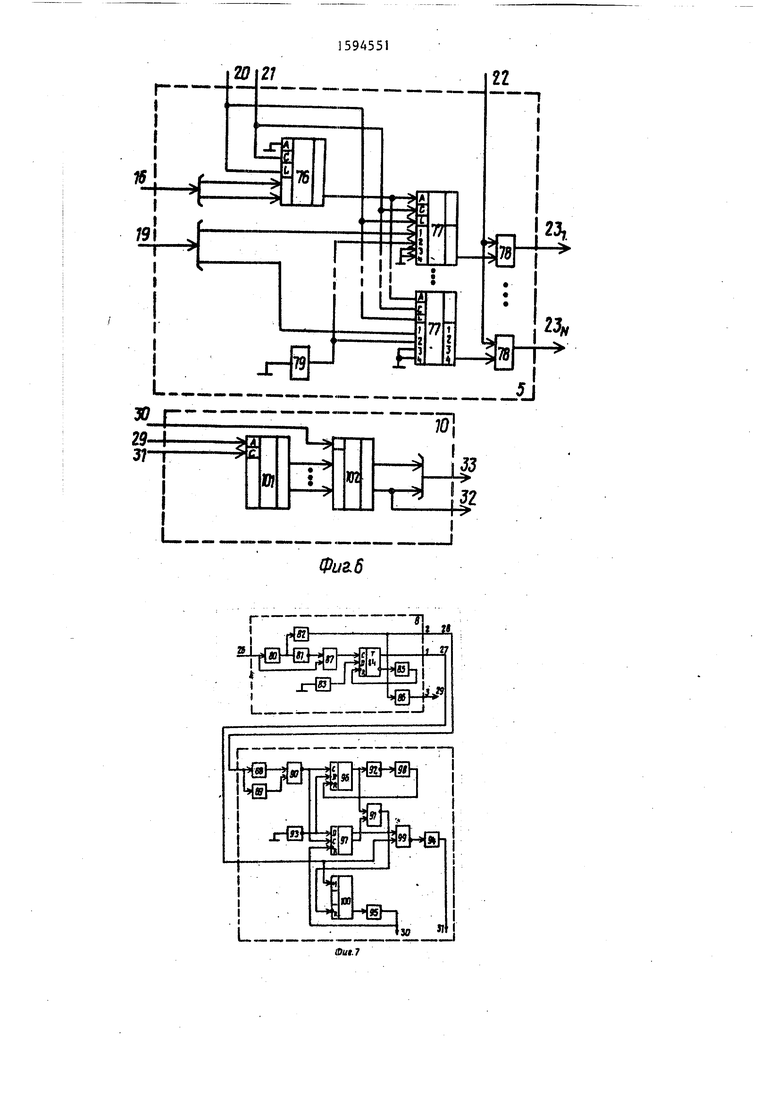

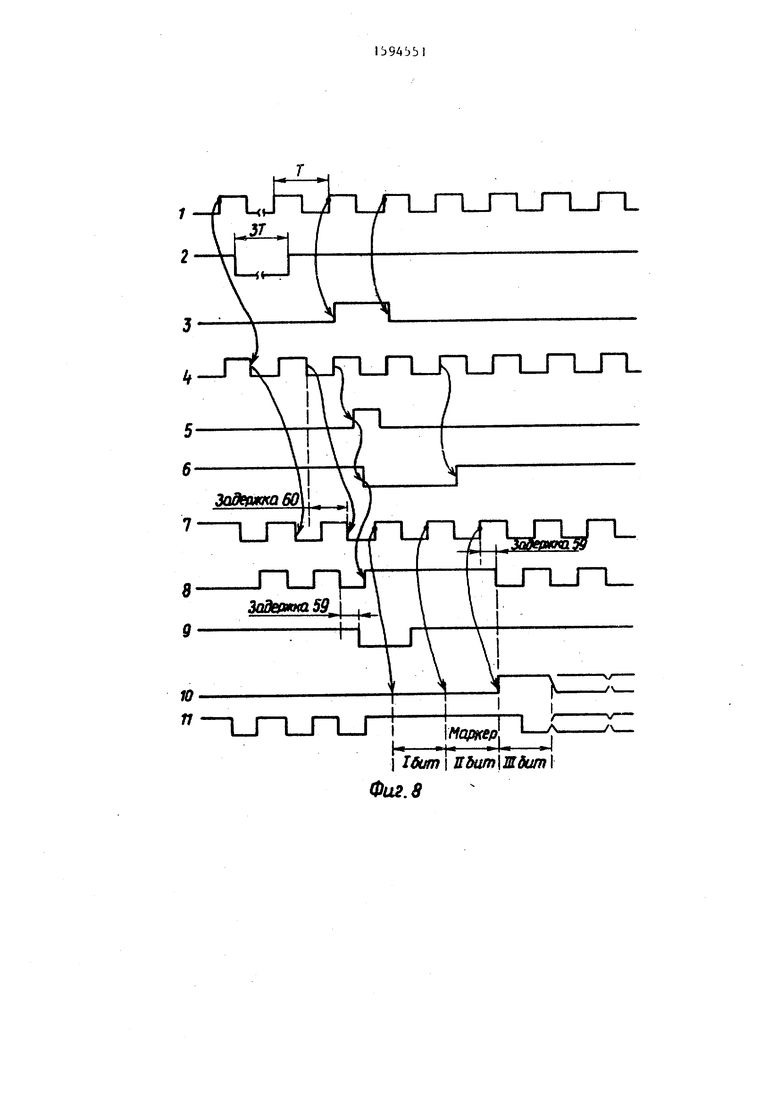

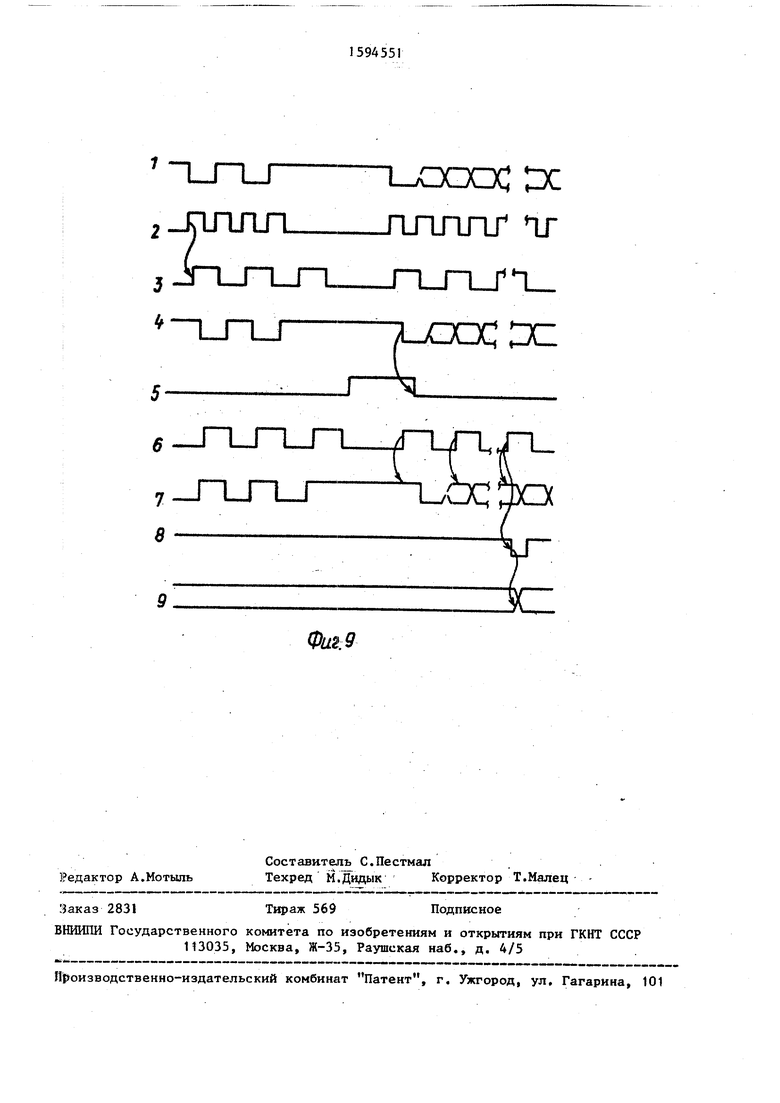

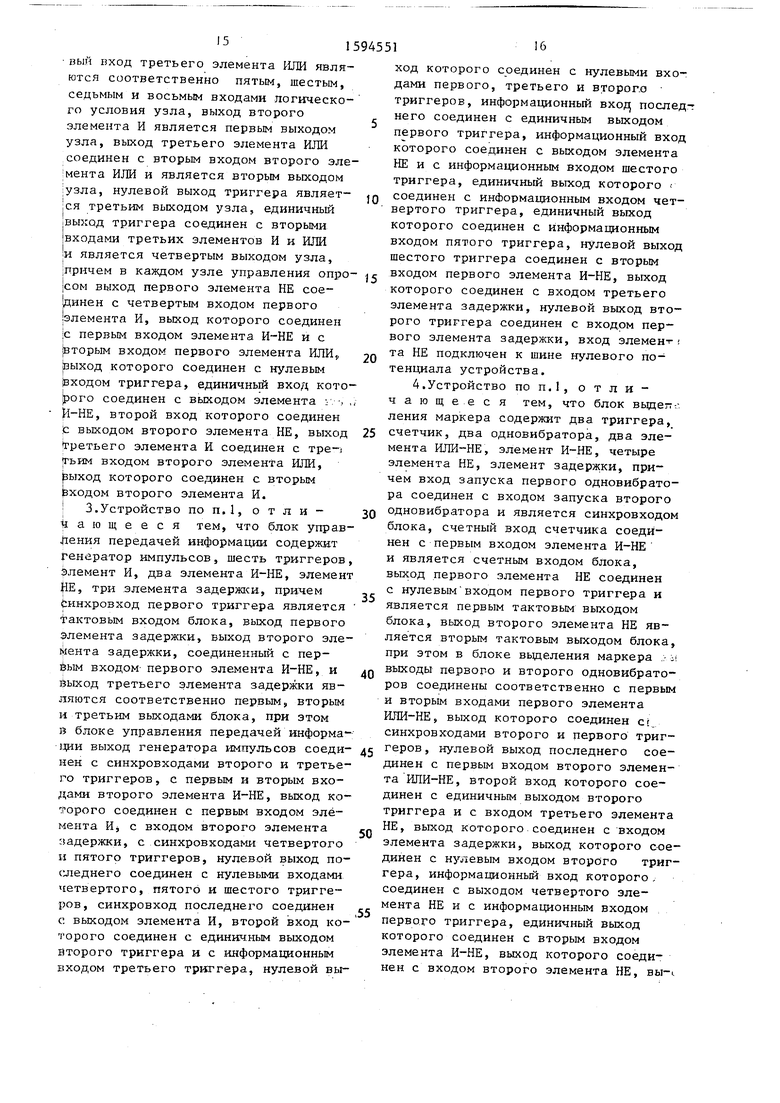

На: фиг.1 представлена функциональная схема устройства; на фиг.2 - схема блоков приемопередатчиков и мультиплексора; на фиг.З - схема блока запросов; на фиг.4 - схема блока управления передачей информации; на фиг.5 - схема блока управления опро - сом; на фиг.6 - схема блока сдвиговых регистров и блока хранения информации; иа фиг.7 - схема блоков восстановления тактового сигнала и вьщелег лния маркера; на фиг.8 - временная диаграмма работы устройства при передаче информации от канала к ПФУ; на фиг.9 - то же, при приеме информации от ПФУ.

Устройство (фиг.1) содержит блок 1 приемопередатчиков, блок 2 запросов, блок 3 управления передачей информации, блок 4 управления опросом, блок 5 сдвиговых регистров, группу блоков 6 передатчиков, группу блоков 7 приемников, группу блоков 8 восстановления тактового сигнала, группу блоков 9 вьщеления маркера, группу блоков 10 хранения информации и мультиплексор 11 .

На фиг. также обозначены группа входов-выходов 12 блока 1, группа входов 13 блока 1, группа выходов 14

СП

;о

4

ел ел

блока ), группа входов 15 блока 2 зал просов, первая группа входов 16 блока 5 сдвиговых регистров, группа входов 17 блока 4 управления опросом, выход 18 сигнала наличия запроса блока 2 запросов, вторая группа входов 19 сигналов опроса блока 5 сдвиговых регистров, вход 20 управляющего сигнала параллельной записи блока 5 сдвиговых регистров, вход 21 синхро- : сигнала блока 5 сдвиговых регистров, I вход 22 тактирования Манчестера бло- ; ка 5 сдвиговых регистров, выходы

Бпок 4 управления опросом (фиг.5) предназначен доя выработки сигналов опроса, входящих в группу выхо2 дов 19, по сигналам из группы входов J7 и в зависимости от наличия и приоритета сигналов на входах 32,-,32 запросов ПФУ и содержит группу узлов 62 управления опросом, каждьй из ко10 торых содержит элементы НЕ 63 и 64, элементы И 65-67, элементы ИЛИ 68 и 69, элемент ИЛИ-НЕ 70, триггер 71, элемент И-НЕ 72 и входы 73-75.

Блок 5 сдвиговых регистров (фиг.6)

i,r N/r сдвиговых регистров, ,5 предназначен для преобразо;ани; ;;и: выхода 24 блоков 6 передатчиков, вхо-, формации, поступающей на о- ды 25 и выходы 26 блоков 7 приемник.-. вхо

ков, выходы 27 и 28 блоков 8 восстановления тактового сигнала, выходы;

20

:29 блоков 8 восстановления тактового iсигнала, выходы 30 и 31 блоков 9 вы- Iделения маркера, выходы 32 блоков 10 :хранения информации, группы выходов ; 38 блоков 10 хранения информации.

дов 16 и 19 блока 5 , из параллельного кода в последовательный код Мин- честер на выходах 23 блока 5 и содержит сдвиговый регистр 76, количество разрядов которого соответствует числу входов в группе входов 16 блока 5, группу четырехразрядных сдвиговых регистров 77, группу элементов.

„ , - j cinnyujo //, группу элементе

опок 1 приемопередатчиков (фиг.2) 25 ИСЮПОЧАЮЩЕЕ ИЛИ 78 и элемент HF 7Р

ЛМЯЧ иатюьт гтггст -rt-Tf.-r .L / 7

Iпредназначен для усиления сигналов, I поступающих из групп входовпвыходов ;12, и согласования по времени управ- сигналов с информационными и I содержит группу усилителей-приемни- ;ков 34 сигналов от канала, группу усилителей-передатчиков 35 сигналов от ПФУ, группу элементов 36 задержки управляющих сигналов от ПФУ.

Блок 6 передатчиков предназначен для преобразования электрического сигнала, поступающего на вход 23 блока, в оптический сигнал на выходе 30 24 блока 6 и, например, может содержать оптический передатчик типа МПД-1.

Блок 7 приемников предназиачеи для преобразования оптического сиг„ „ / оч нала, поступающего на вход 25 блока

, Блок. 2 запросов (фиг.З) предназ- 7 из оптической линии, в электричесS на ; 1 Г °Г™ кий информационный си;нал на вьосоде ;Са на передачу информации по оптичес- - - -«

|кой линии на выходе 1 8 блока 2 при из- Менении состояния одного из управл ш- цих входов из группы входов 15 управ- 40 пяющих сигналов от канала блока 2 и содержит группу триггеров 37, группу триггеров 38, группу элементов НЕ 39, количество элементов в каждой из кото,рых соответствует количеству входов: 45 вьосодах 28 и 29 блока 8 по ииформа;; группы входов 15 блока 2, кроме того, ционному сигналу, поступающему на Д с;

элементы и нП °« 6 блока 8 и содержит элементы элементы И-НЕ 43 и 44, два одновибра- НЕ 80-83, триггер 84, элементы 85 и... гора 45 и 46 и элемент ИПИ-НЕ 47. 86 задержки и элемен; ИСЮПОЧАЮЩЕЕ

Ьлок 3 управления передачей инфор- о ИЛИ 87.

мащш (фиг.4) предназначен для форми- Едок- 9 выделения маркера (фиг.7) рования на выходах 20-22 блока 3 сиг- vw.

налов управления передачей информа- :№и по оптической линии при появлении

I iiv,iojlc:iltlM v v.. jriiaiuiu,cjM net U lUpUM ВХОД ЛО ОЛОКс

яа входе 18 блока 3 сигнала 18 запроса- подсчета принимаемых из оптической н содержит триггеры 48-53, генератор линии битов информации, следующих .54 импульсов, элементы И-НЕ 55 и 56, НЕ 57, элемент И 58 и злемен- ты 59-61 задержки.

26 блока 7 и, например, может содержать серийный оптический приемник типа МПР-1.

Блок 8 восстановления тактового с,.г; сигнала (фиг.7) предназначен дпя восстановления тактового сигнала иа выходе 27 блока 8 и формирования задержанных, информационных сигналов иа

предназначен для обнаружения маркера в задержанном информационном сигнале, поступающем на второй вход 28 блока.

за маркером, синхронно с восстановленным тактовым сигналом на входе 27 -.i. блока 9, а также для выработки сигнаБпок 4 управления опросом (фиг.5) предназначен доя выработки сигналов опроса, входящих в группу выходов 19, по сигналам из группы входов J7 и в зависимости от наличия и приоритета сигналов на входах 32,-,32 запросов ПФУ и содержит группу узлов 62 управления опросом, каждьй из которых содержит элементы НЕ 63 и 64, элементы И 65-67, элементы ИЛИ 68 и 69, элемент ИЛИ-НЕ 70, триггер 71, элемент И-НЕ 72 и входы 73-75.

Блок 5 сдвиговых регистров (фиг.6)

предназначен для преобразо;ани; ;;и: формации, поступающей на о- вхо

предназначен для преобразо;ани; ;;и: формации, поступающей на о- вхо

дов 16 и 19 блока 5 , из параллельного кода в последовательный код Мин- честер на выходах 23 блока 5 и содержит сдвиговый регистр 76, количество разрядов которого соответствует числу входов в группе входов 16 блока 5, группу четырехразрядных сдвиговых регистров 77, группу элементов.

- j cinnyujo //, группу элементе

ИСЮПОЧАЮЩЕЕ ИЛИ 78 и элемент HF 7Р

кий информационный си;нал на вьосоде - - -«

вьосодах 28 и 29 блока 8 по ииформа;; ционному сигналу, поступающему на Д с;

26 блока 7 и, например, может содержать серийный оптический приемник типа МПР-1.

Блок 8 восстановления тактового с,.г; сигнала (фиг.7) предназначен дпя восстановления тактового сигнала иа выходе 27 блока 8 и формирования задержанных, информационных сигналов иа

Едок- 9 выделения маркера (фиг.7) vw.

.. jriiaiuiu,cjM net U lUpUM ВХОД ЛО ОЛОКс

подсчета принимаемых из оптической линии битов информации, следующих

предназначен для обнаружения маркера в задержанном информационном сигнале, поступающем на второй вход 28 блока.

подсчета принимаемых из оптической линии битов информации, следующих

за маркером, синхронно с восстановленным тактовым сигналом на входе 27 -.i. блока 9, а также для выработки сигна51594551

лов на выходах 30 и 31 блока 9, управляющих работой блока 10 хранения информации, и содержит одновибра- торы 88 и 89, элементы ИЛИ-НЕ 90 и 91, элементы НЕ 92-95, триггеры 96 и 97, элемент 98 задержки, элемент И-НЕ 99 и счетчик 100.

Блок 10 хранения информации . . (фиг.6) предназначен для приема информации, поступающей на вход 29 блог ка 10 синхронно с сигналом на входе 31 блока 10, и запоминания ее по сигналу на входе 30 блока 10 и содержит сдвиговый регистр 10.1 и буферный регистр 102.

Мультиплексор 11 (фиг.2) предназначен для формирования из групп , . входов 33 блока 11 одной группы вы- ходов 13 и содержит элемент И 103 и группу элементов ИЛИ 104, количество которых на единицу меньше количества входов в каждой группе входов 33 блока 11.

На фиг.1 также обозначены не вошедшие в устройство оптические линии 105 устройства 106 сопряжения ПФУ с оптическими линиями для связи с каналом, группы входов-выходов которых подключены к входам-выходам ПФУ 107, и канал 108 ЭВМ.

Устройство работает следующим образом.

К группе входов-выходов 12 устройства подключается канал ввода-вьшода, к выходам 24 устройства подключаются входы оптических линий передачи от .... канала к ПФУ, к входам 25-устройства подключаются входы оптических линий передачи информации от ПФУ к каналу. При включении устройства все блоки и узлы устанавливаются в исходное нулевое состояние. Линии сброса не показаны с целью облегчения описания принципов работы устройства.

При изменении состояния одной из управляющих шин канала блок 2 запро -с сов вырабатывает на выходе 18 сигнал наличия запроса на передачу йнформа- . ции по оптическим линиям, по которому одна и та же информационная посьшка, представляющая собой маркер, за которым следует цепочка битов информации в последовательном коде Манчестер, поступает на входы всех оптических иний, подключенных к вьпсодам 24 устройства, причем количество битов инормации в цепочке соответствует количеству интерфейсных шин от канала.

Q

и

20

25

30 л

,с к

40 в

45 Н

50 о

55

При получении информационной посыпки от ПФУ на оптическом входе 25 соответствующего блока 7 приемников последний осуществляет преобразование оптического сигнала в цифровой информационный сигнал Манчестера, из которого в блоке 8 восстановления тактового сигнала на выходе 29 формируется

Q задержанный информационный сигнал, по которому происходит последовательное (бит за битом) занесение принимаемой информации в сдвиговый регистр 101 . блока 10 хранения информации, а

и также запуск счетчика 100 принимаемых битов в блоке 9 вьщеления маркера, причем информация загружается в сдвиговый регистр 10J только после обнаружения маркера блоком 9 выделе20 ния маркера. После того, как требуемое количество битов загружено в сдвиговый регистр 101, по сигналу, вырабатываемому блоком 9, на выходе 30 информация из сдвигового регистра 101

25 стробируется в буферный регистр 102, .. откуда через мультиплексор 11 поступает в блок 1, где осуществляются необходимые согласования сигналов и усиление для взаимодействия с кана30 лом ввода-вывода согласно интерфейса ЕС ЭВМ.

Рассмотрим формирование сигнала опроса для передачи в оптические линии. Исходное состояние триггера 71

,с каждого узла 62 управления опросом блока 4 управления опросом (фиг.5) нулевое. Если сигнал опроса появляетгг ся на входе 75 блока в последовательности начальной выборки, при этом на

0 входах 73 и 84 блока присутствуют сигналы идентификации адреса и работы канала, то он пропускается через элементы И 66 на выходы каждого узла 62 и передается во все оптические ли5 НИИ одновременно.

Если на одном из входов 32 запросов от ПФУ узла 62 управления опросом блока появляется единичный сигнал и канал р ответ на него посылает сигнал

0 опроса, приходящий на вход 75 блока 4 управления опросом, то на всех входах элемента И 67 соответствующего узла устанавливаются единичные потенциалы, в результате чего на входе установки в 1 триггера 71 появляемся нулевой потенциал, который устанавли5

вает его в единичное состояние, на входе установки в О при этом появляется единичный потенциал. Единичный

1594551

потенциал с прямого выхода триггера 71 поступает на вход элемента И 65, . . поскольку триггер 71 предыдущего узла, как и всех остальных, за исклгочег.

нием рассматриваемого, находится в нулевом состоянии, то на выходе эле- : мента И 65 формируется единичный по- ; тенцнал, который через элемент ИЛИ 68 I дает разрешение на прохождение I нала опроса 75 на выход элемента И 66 ; соответствующего узла. Таким образом ; сигнал опроса появляется на выходе ; того узла 62 управления опросом, на ; вход 32 которого поступил запрос от : ПФУ, и передается единичным сигналом ; в оптическую линию, подключенную к i тому ПФУ, от которого пришел запрос. : Во все ocTajibHHe оптические линии сиг;

; нал опроса передается нулевым. : Если поступают запросы от несколь- : кик ПФУ, то сигнал опроса посылается

в ту оптическую линию, которая под- ключена к ПФУ, запрос от которого : является более приоритетным. Приори- тет обеспечивается связью инверсного выхода триггера 71 последующего .- л i узла 62 управления опросом с входом ; элемента И 67 предыдущего узла. Пока : триггер 71 последующего узла не сброг сится в нулевое состояние, не установится аналогичной триггер предьщуще- ; го узла. Таким образом, наименьшим приоритетом обладает запрос 32 от ПФУ, поступивший на вход первого узла 62 управления опросом...После обработки блока приоритетных запросов происходит обработка менее приоритетных.

Если при посылке сигнала опроса в последовательности начальной выборки ни одно из подключенных ПФУ 107 не опознало свой адрес, то на выходе элемента И мультиплексора 11 появляется единичный сигнал обратного са, поступаюш;ий в канал через блок 1.

Если одно из ПФУ,опознало адрес, то на один из входов элемента И 103. мультиплексора 11 сигнал обратной выборки lie поступает, в результате чего на выходе элемента И 103 не формируется сигнал обратного опроса в канал.

Рассмотрим работу устройства, когда канал 108 ввода-вьшода инициирует передачу информации к ПФУ. При этом сигналы, поступающие от канала, усиливаются группой усилителей-приемников 34 блока 1. При изменении состоя8

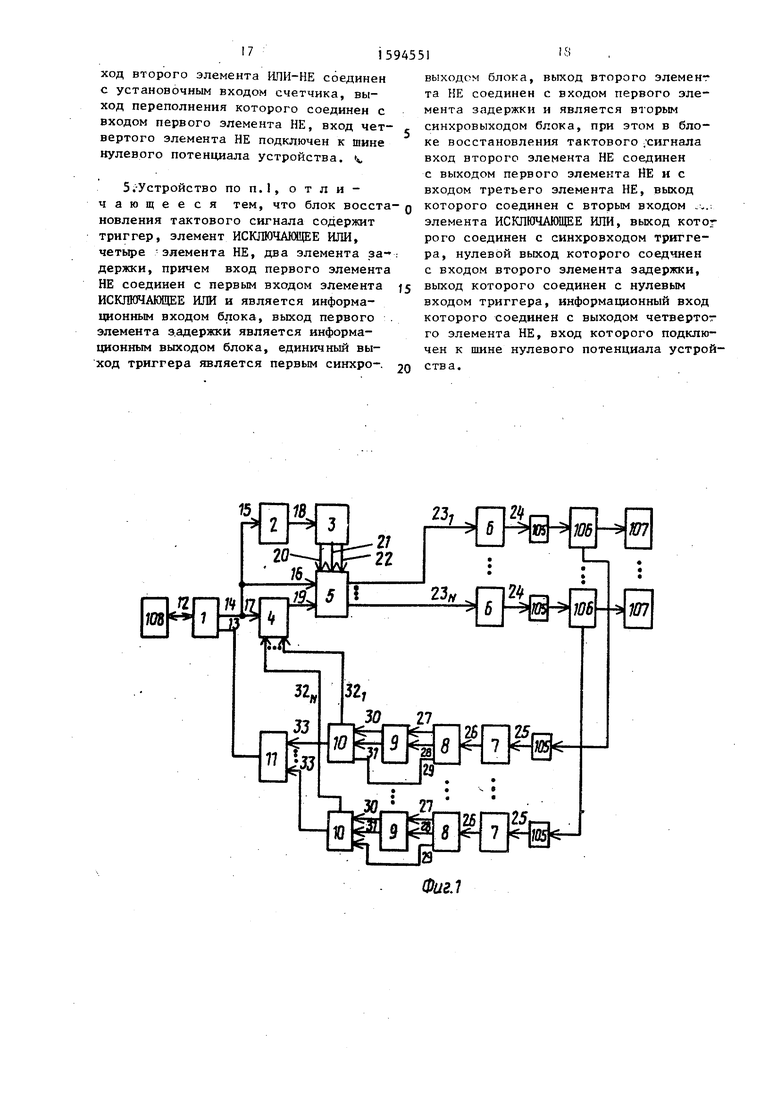

ния одного из управляющих сигналов от канала из группы входов 15 блока 2 запроЪов (фиг.З) устанавливается в единичное состояние соответствующий ему триггер 37 или 38, реагирующий соответственно на передний или на задний фронт сигнала, при этом на выходах элементов И-НЕ 43 или 44 появляется единичный сигнал, задний фронт которого формируется с помощью цепи обратной связи на элементах НЕ 41 и 42. По этому сигналу происхо дит запуск одного из одновибраторов 45 или 46, на выходе которого формируется положительный импульс, в результате чего на выходе 18 блока 2 запросов появляется нулевой сигнал наличия запроса на передачу информации по оптическим линиям (фиг.8, линия 2)„ Дпительность импульса на выходах одновибраторов устанавливается равной трем тактовым периодам, в то же время она не .-должна быть меньще времени стабилизации информации на шинах данных и шинах управления, которое для интерфейса ЕС ЭВМ составляет не менее 100 не.

По сигналу наличия запроса на вьк: ходе 18, поступающему на синхровход триггера 48 блока 3 управления передачей (фиг.4), триггер 48 устанавлкг вается в единичное состояние. По переднему фронту тактового импульса, следующего за установкой в единичное состояние триггера 48, устанавливается в единичное состояние триггер 49, разрешающий формирование маркера. Тактовые импульсы (фиг.9, линия 1) вьфабатываются генератором 54 сигналов. Триггер 49 находится в единич- гом состоянии один период тактового сигнала 1(фиг.8, линия 3), поскольку по следующему тактовому сигналу он сбрасьюается в нулевое состояние по входу установки в О. По сигналу с выхода элемента И 56 (фиг.8, лк-, ния 5), на вход которого поступает сипнап с прямого выхода триггера 44 и проинвертированный и задержанный на элементе И-НЕ 55 тактовый сигнал (фиг.8, линия 4), триггер 51 устанавливается в единичное состояние. Потенциал логического нуля, появившийся на инверсном выходе триггера 51, запрещает вьфаботку тактового сигнала Манчестера на выходе 22 блока 3 управления передачей информации. Сигнал с инверсного выхода :/

триггера 51 изображен линией 6 (фиг.8), сигнал тактирования Манчестера на выходе 22 блока 3 управления передачей информации изображен линией 8 (фиг.8).

По сигналу на выходе 20 блока 3 с инверсного выхода триггера 49 разрешения формирования маркера (фиг.8, линия 9), поступающему на управляющие входы параллельной записи всех сдвиговых регистров блока 5 сдвиговых регистров, происходит загрузка информации параллельно во все разряды всех регистров блока..Загрузка и сдви информации происходят синхронно с тактовым сигналом сдвигового регистра (фиг.8, линия 7).

Элемент 60 задержки блока 3 у.прав -ления передачей информации введен для компенсации задержки на элементе И 58 и триггере 51, элемент 59 задержки блока 3 уравнивает задержку, вызываемую элементом 60 задержки.

В сдвиговый регистр 76 блока 5 сдвиговых регистров загружаются шины данных и шины управления от канала, кроме шин опроса, которые загружаются в старшие разряды четырехразрядных . . сдвиговых регистров 77. В младшие pa3 ряды сдвиговых регистров 77 загружаются три разряда маркера. Старший разряд маркера поступает в сдвиговые регистры 77 потенциалом логической единицы, формируемой на выходе мента НЕ 79, два младших разряда маркера формируются путем подключения двух младших разрядов сдвиговых ре- . гистров 77 к шине Земля.

Информация, получаемая при сдвиге иа выходе младшего разряда каждого регистра 77, изображена (фиг.8, линия 10). .Информация в коде Манчестер, поступающая на выходы 23,- 23 блока 6 сдвиговых регистров выходов элементов ИСКЛЮЧАЮЩЕЕ ШШ 78, изображена линией 11 (фиг.8).

При кодировании в коде Манчестер логическая единица представляется переходом из состояния логической единицы в состояние логического нуля, приходящимся на середину тактового периода, логический нуль представля-. ется положительным переходом из состояния логического нуля в состояние . логической единицы, приходящимся на середину тактового периода. Первый и второй биты маркера поступают с выг ходов элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 78

0

5

з

0

,j

5

0

5

0

5

уровнями логической единицы, третий бит маркера - единицей н коде Манчестера. Для того, чтобы период из логической единицы я логическому нулю, представляющий единицу в коде Манчестера, приходился на перепад сигнала i тактирования Манчестера логической единицы к логическому нулю (фиг.8, линия 8), введена задержка этого сигнала на элемент 61 задержки блока 3 управления передачей информации. За маркером формируются биты информации в коде Манчестер.. Информационный вход последовательной записи сдвигового регистра 76 подключен к потенциалу Земля, поэтому после сдвига всех информационных битов, занесенных в сдвиговые регистры 76 и 77, в последних происходит сдвиг нулей. Таким образом в промежутках между информа-н: ЦИОННЫ14И посылками в оптические линии передаются нули в коде Манчестер.

Рассмотрим работу устройства при получении информации от ПФУ.

Из оптической линии на вход 25 блока 7 приемников поступает сигнал, который преобразуется из оптического в цифровой сигнал Манчестера на выходе 26 блока 7 (фиг.9, линия 1). Линия 2 (фиг.9) представляет сигналы на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 87 блока 8 восстановления тактового сигнала. Каждый импульс имеет длительность, равную задержкам на элементах НЕ 80 и 81 блока 8, и формируется по каждому переходу сигнала Манчестера. Импульсы с выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 87 поступают иа синхровход триггера 84, который устанавливается в единичное состояние только импульсами, которые выходят из элемента 87 в середине каждо-- го такта. Такой режим триггера 84 обеспечивается за счет элемента 85 задержки, включенного в цепь сброса триггера, который позволяет удерживать триггер в нулевом состоянии до середины следующего такта.

Единица Манчестера в маркере используется для обеспечения того, чтот бы первый импульс, поступающий на синхровход триггера 84, формировался в середине битового периода сигнала Манчестера. Сигнал с прямого выхода триггера 84 является восстановленным тактовым сигналом (фиг.9, линия 3).

Восстановленный тактовый сигнал поступает на вход 27 блока 9 выделе-г.

нкя маркера, где запускает счетчик

100принимаемых битов. Последний за пускается только после того, как на входе установки в О счетчика появи ся единичный потенциал после обнару- жения маркера. Для обнаружения маркера в задержанном сигнале Манчестера, поступающем на вход 28 блока 9 (, линия 4), два одновибратора 88 и 89 с пов рорным перезапуском запускаются соответственно по переднему и заднему фронту этого сигнала.

Длительность обоих одновибраторов устанавливается такоЙ5 чтобы все сиг налы, кроме маркера, удерживали элемент ИЛИ-НЕ 90 блока 9 в нулевом состоянии. В случае прихода маркера оба одновибратора некоторое время простаивают, в результате чего на выходе элемента ИЛИ-НЕ 90 появляется единичный сигнал (фиг.9, линия 5). По этому сигналу в единичное состояние устанавливаются оба триггера 96 и 97 блока 9, в результате чего на входы установки в О счетчика 100 принимаемых битов установится единичный сигнал, разрешающий запуск счетчика. Триггер 96 сбрасьшается цепью . обратной связи на элементах НЕ 92 и злементне 98 задержки дпя того, чтобы в случае прихода следующего маркера сбросить счетчик 100 битов, который подсчитьшает количество битов в информационной посьшке плюс один для последнего бита маркера в коде Манчестера,

После обнаружения маркера восста-о новленный тактовый сигнал на входе 27 блока детектирования маркера про- пускается с выхода элемента НЕ 94 на выход 31 блока 9, откуда как тактовый сигнал сдвигового регистра поступает на синхровход сдвигового регистра 101 хранения информации (фиг.9, линия 6). По переднему фронту этого сигнала в сдвиговый регистр

101заносится задержанный информа- ционный сигнал Манчестера, поступающий на информационный вход последо- вательной записи сдвигового регистра

101 (фиг„9, линия 7). После того, как информационная посылка получена полностью, на выходе счетчика 100 блока 9 устанавливается единичный сигнал, который через цепь обратной связи сбрасьшает триггер 97 блока 9, формирует нулевой сигнал на выходе элемента ИЛИ-НЕ 91 и сбрасьшает счетчик 100 блока 9. В результате на выходе 30 блока 9 формируется нулевой сигнал (фиг.9, линия 8), по переднему фронту которого информация из сдвигового регистра 101 переписьшает ся в буферный регистр 102 (фиг.9, линия 9). С выходов буферного регистра информация через мультиплексор 11 поступает на вхрды блока 1, где осуществляются необходимые временные согласования на элементах 36 задержки, и усиленные через усилители- передатчики 35 сигналы от ПФУ поступают на входы канала ввода-вывода.

Рассмотрим подключение устройства к оптическим линиям. ,,

Входы 25 и выходы 24 предлагаемог устройства подключаются к оптическим линиям 105, в качестве которых может использоваться, например, серийно,; изготавливаемый оптический кабель типа ОЛПГ-50.

ПФУ 107 подключается к оптическим линиям 105 через устройства 106 сопряжения ПФУ с оптическими линиями -.л для связи с ка:налом, содержащие блоки приема информации и блоки передачи информации.

Блок передачи информации по изменению управляющего сигнала от ПФУ формирует запрос на передачу информации на вход оптической линии 105, по которому информационная посылка, представляющая собой маркер, за которьм следует цепочка битов информации в последовательном коде Манчестера поступает на вход оптической линии 105 для передачи в канал.

Блок приема информации принимает. информацию..от канала 108 с выхода оптической линии 105, преобразует ее из оптического в цифровой сигнал Манчестера, производит последовательное занесение принимаемой информации в сдвиговый регистр после обнаружения маркера, загружает принятую информацию в буфер, откуда она через необходимые временные задержки поступает; на входы ПФУ.

Применение предлагаемого устройства позволит увеличить количество подключаемых групп удаленных ПФУ и повысить быстродействие установления связи канала с ПФУ за счет одновременной посыпки сигнала опроси во все подключенные оптические линии.

3 Формула изобретения

10

15

20

25

30

35

нена с информационными входами блоков 45 элемента И, три элемента ИЛИ, два передатчиков группы, выход наличия, запроса блока формирования запроса, на передачу соединен с тактовым вхо- дом блока управления передачей информации, первый, второй и третий выхо- о ды которого соединены соответственно с входом записи, с синхровходом и тактовым входом блока сдвиг.овьк per rricTpoB, вторая группа информационных, входов которого соединена с группой вЫходов блока управления опросом, вторая группа входов логического условия которого соединена с инфор- . мационными выходами блоков хранения

элемента НЕ, элемент И-НЕ, при это вход первого элемента НЕ, первый в первого элемента И-являются соотве ственно первым и вторым входами ло гического условия узла, вход второ элемента НЕ соединен с первыми вхо ми первого элемента ИЛИ, второго элемента И и является -третьим вход логического условия узла, второй вход первого элемента И является четвертым входом логического услов узла, первый вход второго элемента ИЛИ, первый вход третьего элемента третий вход первого элемента И и п

10

15

; , о-/Qаи594551 .

информации группы, группы информационных выходов которых соединены с группами информационных входов мультиплексора, группа информационных выходов которого соединена с группой информационных входов блока приемопередатчиков, входы записи и синхровходы блоков хранения информации группы соединены соответственно ;с первыми и вторыми тактовыми выходами блоков вьщеления маркера группы, счетные входы и синхровходы которых соединены соответственно с первыми и вторыми синхровыхрдами .блоков восстановления тактового сигнала группы. 2.Устройство по П.1, о т л и -- . I чающееся тем, что блок управг ления опросом содержит группу узлов управления опросом, прич ем первые, вторые и третьи входы логического условия узлов управления опросом группы образуют первую группу входов логического условия блока, четвертые входы логического условия управления опросом группы образуют вторую группу входов логического условия блока, первые выходы узлов управления опросом группы образуют группу выходов блока, при этом второй выход i-ro узла управления опросом соединен с пятым входом логического условия (i+l)-ro узла управления опросом, третий выход i-ro узла управления опросом соединен с шестым входом логического условия (i+l)-ro узла управления опросом и с седьмым входом логического условия (i-l)-ro узла управления опросом, четвертый выход i-ro узла управления опросом соединен с восьмым входом логического условия (i-l)-ro узла управления опросом, причем каждый узел управления опросом содержит триггер, три

20

25

30

35

/

элемента И, три элемента ИЛИ, два

элемента НЕ, элемент И-НЕ, при этом вход первого элемента НЕ, первый вход первого элемента И-являются соответственно первым и вторым входами логического условия узла, вход второго элемента НЕ соединен с первыми входами первого элемента ИЛИ, второго элемента И и является -третьим входом логического условия узла, второй вход первого элемента И является четвертым входом логического условия узла, первый вход второго элемента ИЛИ, первый вход третьего элемента И ,1 третий вход первого элемента И и пер 1

вый вход третьего элемента ИЛИ являются соответственно пятым, шестым, седьмым и восьмьпч входами логического условия узла, выход второго элемента И является первым выходом узла, выход третьего элемента ИЛИ соединен с вторым входом второго эле ;мента ИЛИ и является вторым выходом :узла, нулевой выход триггера являет- ;ся третьим выходом узла, единичный |Выход триггера соединен с вторыми |входами третьих элементов И и ИЛИ |И является четвертым выходом узла.

ход которого соединен с нулевыми вх дами первого, третьего и второго триггеров, информационный вхо посл него соединен с единичным выходом первого триггера, информационный вх которого соединен с выходом элемент НЕ и с информационным входом шестог триггера, единичный выход которого соединен с информационным входом че вертого триггера, единичный выход которого соединен с информационным входом пятого триггера, нулевой вых шестого триггера соединен с вторым

рричем в каждом узле управления опро- входом первого элемента И-НЕ, выход

20

25

30

|сом выход первого элемента НЕ сое- |динен с четвертым входом первого элемента И, выход которого соединен |с первым входом элемента И-НЕ и с вторым входом первого элемента ИЛИ,, выход которого соединен с нулевым входом триггера, единичньй вход кото- |рого соединен с выходом элемента г, , ,, И-НЕ, второй вход которого соединен С выходом второго элемента НЕ, выход третьего элемента И соединен с тре-j |гьим входом второго элемента ИЛИ, ыход которого соединен с вторым (входом второго элемента И. I 3.Устройство по П.1, отличающееся тем, что блок управ- ения передачей информации содержит генератор импульсов, шесть триггеров, Элемент И, два элемента И-НЕ, элемент Щ, три элемента задержан, причем Синхровход первого триггера является тактовым входом блока, выход первого элемента задержки, выход второго элемента задержки, соединенный с пер- йым входом- первого элемента И-НЕ, и йыход третьего элемента задержки являются соответственно первым, вторым и третьим выходами блока, при этом в блоке управления передачей информа- 1даи выход генератора импульсов соедн- xs нен с синхровходами второго и третьего триггеров, с первым и вторым входами второго элемента И-НЕ, выход которого соединен с первым входом элемента Hj с входом второго элемента

35

40

50

которого соединен с входом третьего элемента задержки, нулевой выход вто рого триггера соединен с входом первого элемента задержки, вход элемент та НЕ подключен к шине нулевого потенциала устройства.

задержки, с синхровходами четвертого

и пятого триггеров, нулевой выход по- сшеднего соединен с нулевыми входами четвертого, пятого и шестого триггеров, Синхровход последнего соединен

с выходом элемента И, второй вход ко- первого триггера, единичный выход горого соединен с единичным выходом второго триггера и с информационным входом третьего трисггёра, нулевой вы4.Устройство по П.1, отли чающееся тем, что блок в ления маркера содержит два тригг счетчик, два одновибратора, два мента ИЛИ-НЕ, элемент И-НЕ, четы элемента НЕ, элемент задержки, п чем вход запуска первого одновибр ра соединен с входом запуска втор одновибратора и является синхровх блока, счетный вход счетчика соед нен с первым входом элемента И-НЕ и является счетным входом блока, выход первого элемента НЕ соедин с нулевьм входом первого триггера является первым тактовым выходом блока, выход второго элемента НЕ ляется вторым тактовым выходом бл при этом в блоке вьщеления маркер выходы первого и второго одновибр ров соединены соответственно с пе и вторым входами первого элемента ИЛИ-НЕ, выход которого соединен с синхровходами второго и первого т геров, нулевой выход последнего динен с первым входом второго эле та ИЛИ-НЕ, второй вход которого с динен с единичным выходом второго триггера и с входом третьего элем НЕ, выход которого,соединен с вхо элемента задержки, выход которого динен с нулевым входом второго гера, информационный вход которог соединен с выходом четвертого эле мента НЕ и с информационным входо

которого соединен с вторым входом элемента И-НЕ, выход которого соед нен с входом второго элемента НЕ,

16

ход которого соединен с нулевыми входами первого, третьего и второго триггеров, информационный вхо последнего соединен с единичным выходом первого триггера, информационный вход которого соединен с выходом элемента НЕ и с информационным входом шестого триггера, единичный выход которого соединен с информационным входом четвертого триггера, единичный выход которого соединен с информационным входом пятого триггера, нулевой выход шестого триггера соединен с вторым

входом первого элемента И-НЕ, выход

0

5

0

s

5

0

0

первого триггера, единичный выход

которого соединен с входом третьего элемента задержки, нулевой выход второго триггера соединен с входом первого элемента задержки, вход элемент; та НЕ подключен к шине нулевого потенциала устройства.

первого триггера, единичный выход

которого соединен с вторым входом элемента И-НЕ, выход которого соединен с входом второго элемента НЕ, вы-i

17

ход второго элемента Ш1И-НЕ соединен с установочным входом счетчика, выход переполнения которого соединен с входом первого элемента НЕ, вход четвертого элемента НЕ подключен к шине нулевого потенциала устройства, ч,

З -Устройство по п. 1, отличающееся тем, что блок восста новления тактового сигнала содержит триггер, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, четьфе -элемента НЕ, два элемента за держки, причем вход первого элемента НЕ соединен с первым входом элемента ИСКЛЮЧАЩЕЕ ИЛИ и является информационным входом блока, выход первого элемента з.адержки является информационным выходом блока, единичный выход триггера является первым синхро-.

15

32;

г fet LU Н

I129

п , 20

94551

выходом блока

15

, выход второго элеменг та НЕ соединен с входом первого элемента задержки и является вторым синхровыходом блока, при этом в блоке восстановления тактового сигнала вход второго элемента НЕ соединен с выходом первого элемента НЕ и с входом третьего элемента НЕ, выход которого соединен с вторым входом .-,.; элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход котог рого соединен с синхровходом триггера, нулевой выход которого соединен с входом второго элемента задержки, выход которого соединен с нулевым входом триггера, информационный вход которого соединен с выходом четвертое го элемента НЕ, вход которого подключен к шине нулевого потенциала устройства.

3

J

35

«е55

I

.2J

w

rO39

Я

1/

I/J

JJ

15

4

«7 .

W

«

42

18

&l

D -1 C5f

I«

л

ГП Ч1Л

55

&l

ya

Фиг 4

Ф2;

fZ2

19

L..

Фиг.6

77

jR

1 я

1бит Фиг. 8

П-П-Г

2 ШТГ1Г1

з-г-1 г-1 п

Фи&:9

едактор А.Мотьшь

Составитегаь С.Пестмал

Техред М.Дидык Корректор Т.Малец

Заказ 2831

Тираж 569

ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

П1Еюизводственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

l- CDCXDC

I-Ллллггг и

/ьоос

е-Л-

Подписное

| Патент США № 4276656, кл | |||

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Development of Optical Channel Subsystem for Computers.- Hitachi Reviev, 1987, v.36, 4, p.221-226. | |||

Авторы

Даты

1990-09-23—Публикация

1988-07-11—Подача