Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной поддержки вычислений в системах синтеза и анализа цифровых автоматов, диагностики цифровых устройств, сжатия данных, обработки изображений, управления роботами-манипуляторами, синтеза топологии БИС.

Целью изобретения является расширение функциональных возможностей за счет обработки систем логических функций.

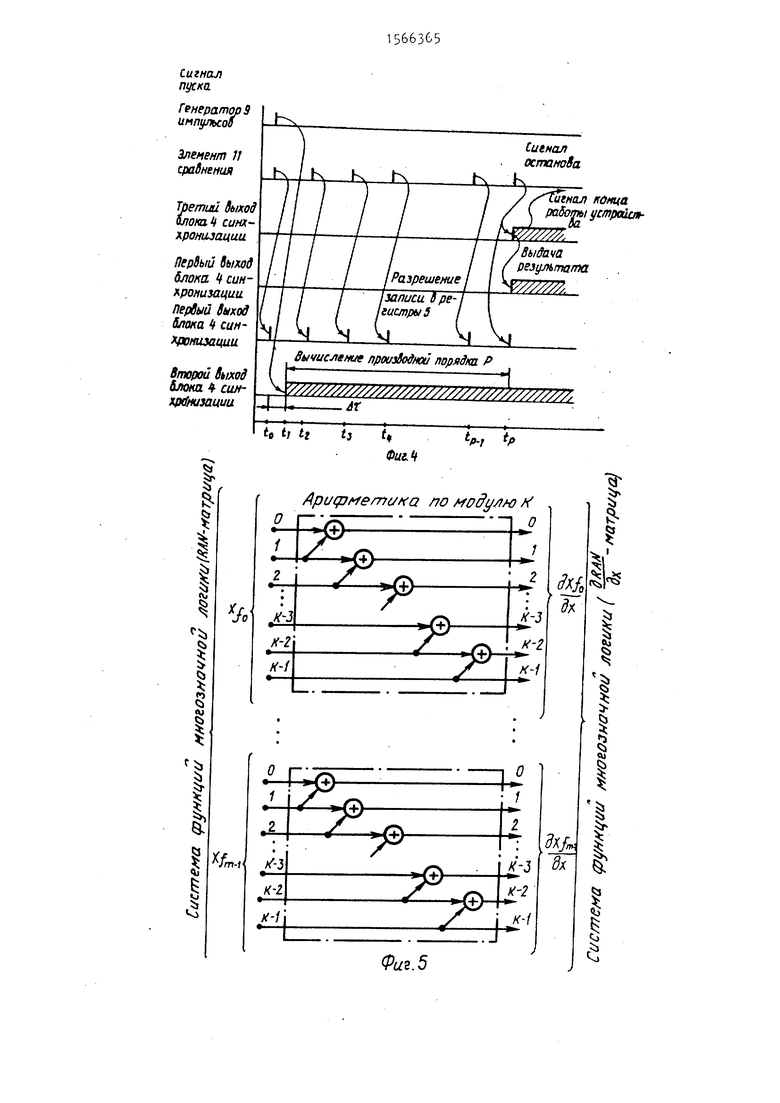

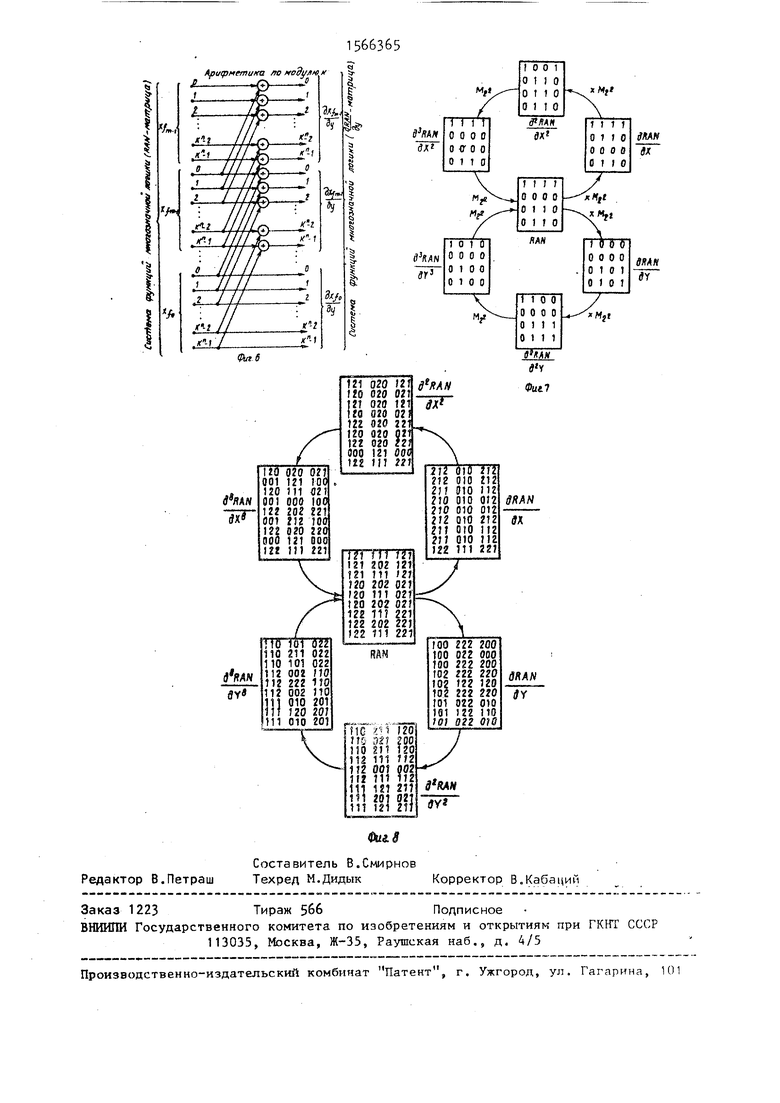

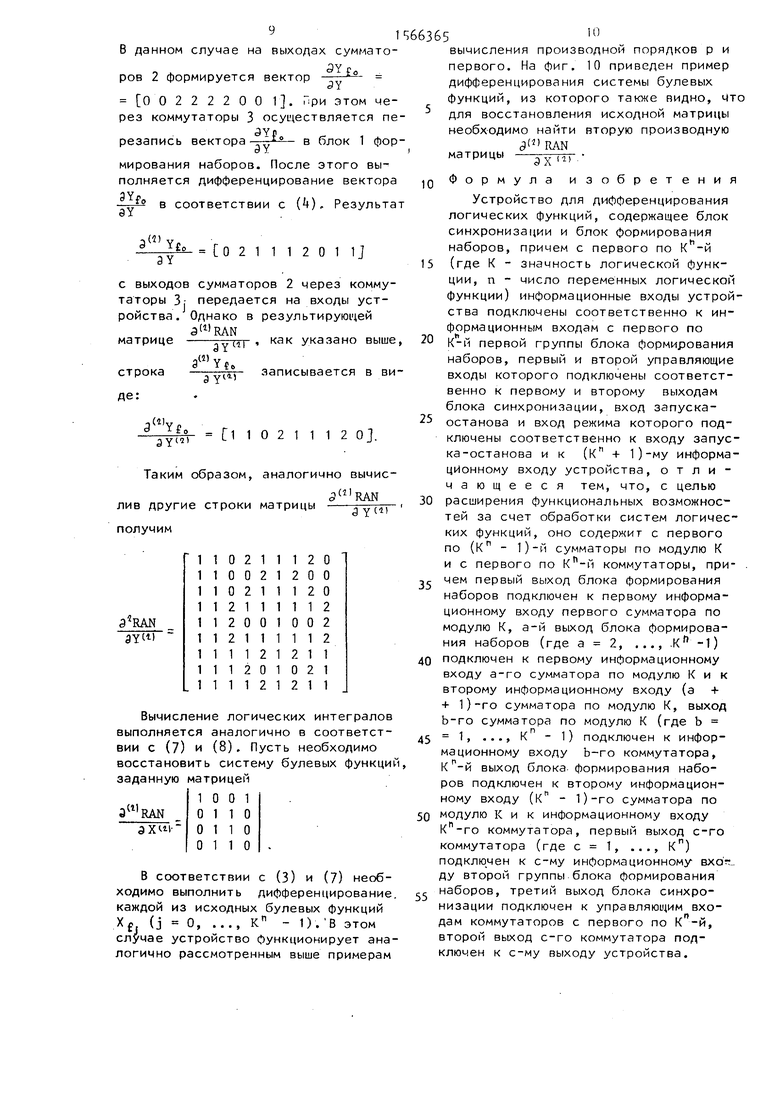

На фиг. 1 представлена схема устройства; на фиг. 2 - схема блока формирования наборов , на фиг. 3 схема блока синхронизации;на фиг. - временная диаграмма функционирования блока синхронизации; на фиг. 5 операционный граф функционирования устройства в режиме дифференцирования логической функции по координате X; на фиг. 6 - операционный граф функционирования устройства в режиме дифференцирования логической функции по координате Y, на фиг. 7 пример дифференцирования системы булевых функций по координатам X и Y , на фиг. 8 - пример дифференцирования системы логических функций по координатам X и Y при |( 3 и п 2

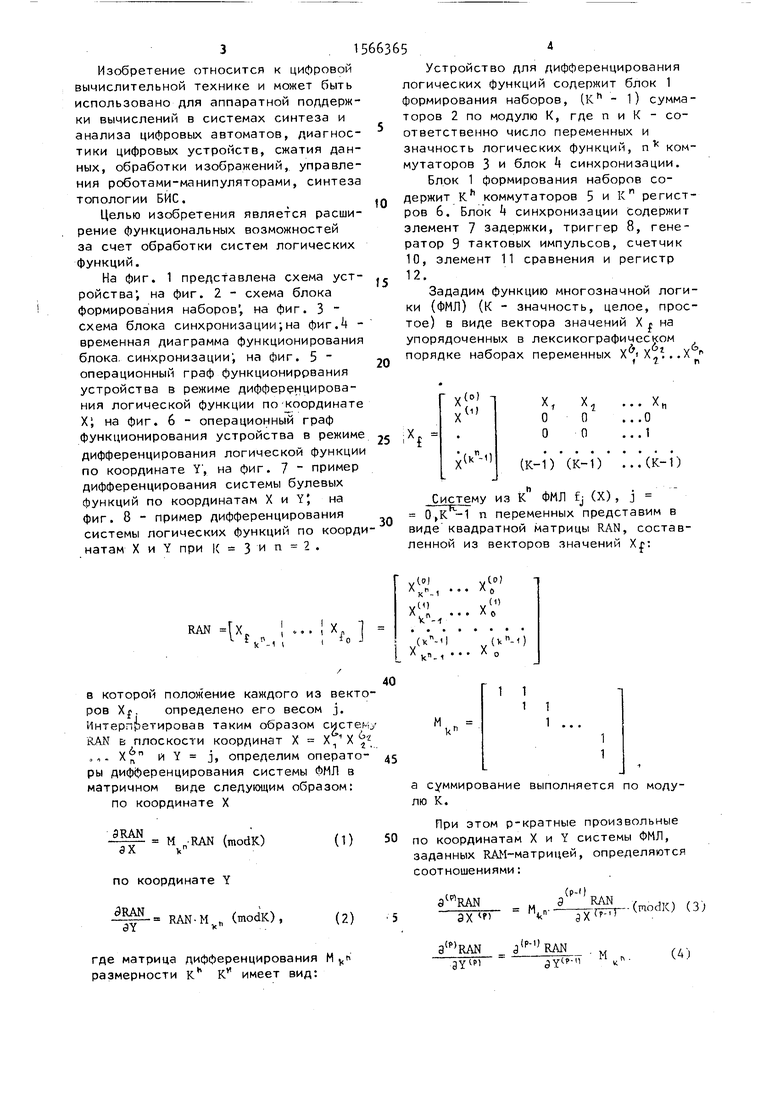

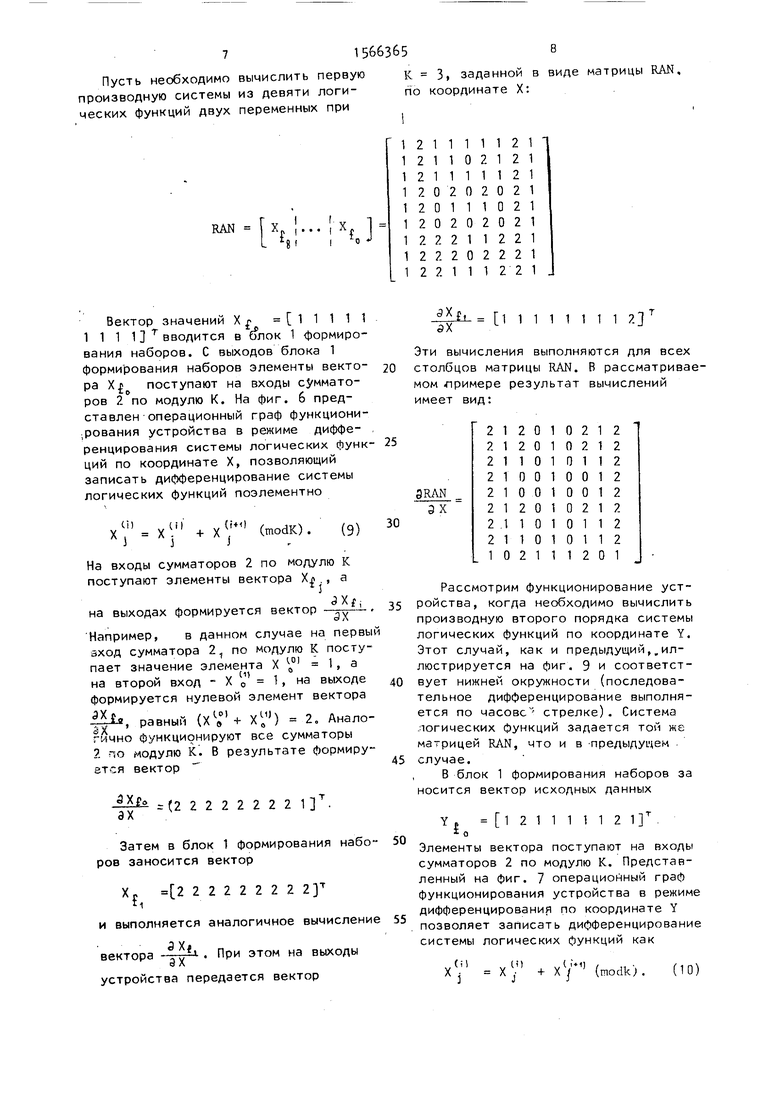

Устройство для дифференцирования логических функций содержит блок 1 формирования наборов, (Kh - 1) сумматоров 2 по модулю К, где п и К - соответственно число переменных и значность логических функций, n v коммутаторов 3 и блок 4 синхронизации.

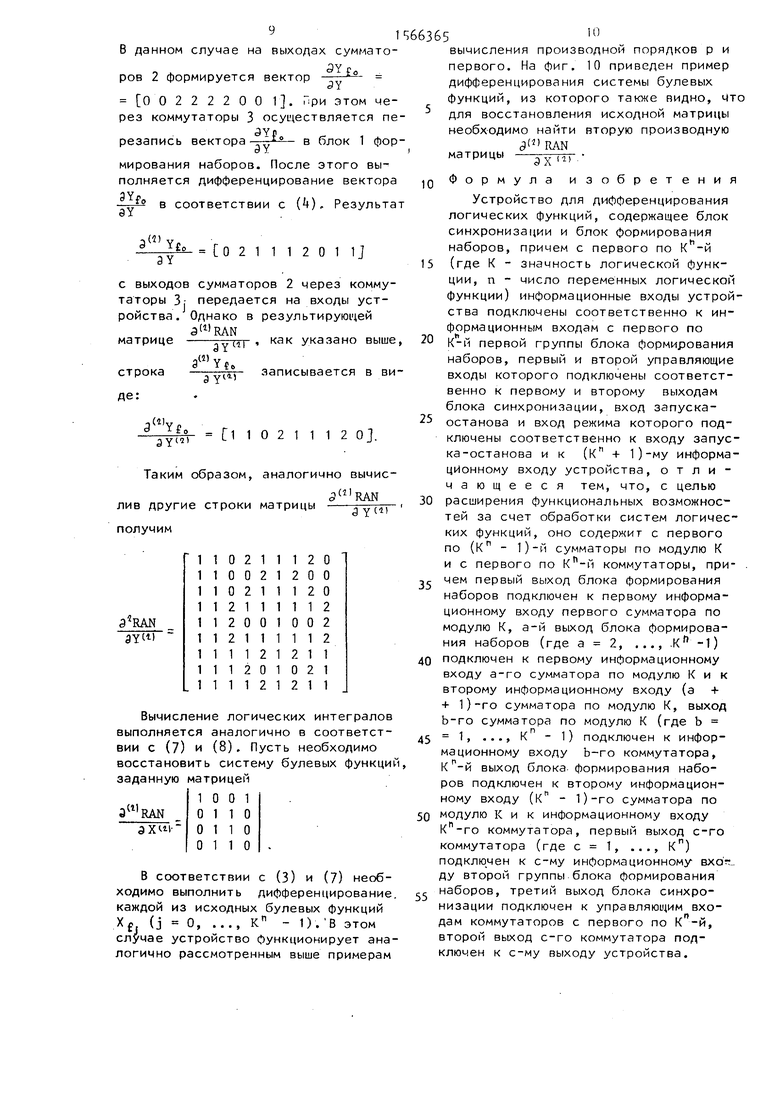

Блок 1 формирования наборов содержит Kh коммутаторов 5 и К регистров 6. Блок 4 синхронизации содержит элемент 7 задержки, триггер 8, генератор 9 тактовых импульсов, счетчик 10, элемент 11 сравнения и регистр 12.

Зададим функцию многозначной логики (ФМЛ) (К - значность, целое, простое) в виде вектора значений X г на упорядоченных в лексикографическом порядке наборах переменных Х X. ..X

г (О)

Id)

Х|Хк -И

Систему из К ФМЛ fj (X) , j О,К -1 п переменных представим в виде квадратной матрицы RAN, составленной из векторов значений Хг:

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для логического дифференцирования и интегрирования булевых функций | 1988 |

|

SU1541592A1 |

| Устройство для вычисления логических производных многозначных данных | 1989 |

|

SU1656549A1 |

| Устройство для логического дифференцирования булевых функций | 1988 |

|

SU1541591A1 |

| Устройство для вычисления логических производных многозначных данных | 1989 |

|

SU1670690A1 |

| Устройство для распознавания на линейность булевых функций | 1990 |

|

SU1756879A1 |

| Устройство для вычисления логических производных многозначных данных | 1990 |

|

SU1837277A1 |

| Устройство для вычисления булевых производных | 1987 |

|

SU1481793A1 |

| Модуль для вычисления логических производных | 1989 |

|

SU1730617A1 |

| Магнитооптическое устройство для вычисления параметрических булевых производных | 1989 |

|

SU1712950A1 |

| Устройство для вычисления булевых дифференциалов | 1989 |

|

SU1777132A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной поддержки вычислений в системах синтеза и анализа цифровых автоматов, диагностики цифровых устройств, сжатия данных, обработки изображений, управления роботами - манипуляторами, синтеза топологии БИС. Цель изобретения - расширение функциональных возможностей устройства за счет обработки систем логических функций. Поставленная цель достигается тем, что устройство содержит блок 1 формирования наборов, (KN-1) сумматоров 2 по модулю K, где N - число переменных логических функции, K - значность логической функции, KN коммутаторов 3 и блок 4 синхронизации. 8 ил.

RAN

I,

vn-i i

в которой положение каждого из векторов Xf. определено его весом j. Интерпретировав таким образом систему RAN Б плоскости координат X ... Хп и Y j, определим операторы дифференцирования системы МЛ в матричном виде следующим образом: по координате X

М „RAN (modK) (1) 50

по координате Y

RAN-M „ (modK), (2)

где матрица дифференцирования М v размерности кь К имеет вид:

40

1 1

1 1

V

45

1

а суммирование выполняется по модулю К.

При этом р-кратные произвольные по координатам X и Y системы ФМЛ, заданных RAM-матрицей, определяются соотношениями:

3tnRAN

ЭХ f)

(nodK) (з,

ах

3(RAN Л RAN

(tlк

(4)

51

Устройство реализует математические модели (3) и ( О ; при этом учитывается свойство периодичности:

у t«-p

Y

где 0 р k - 1 ; t О, 1, 2, ...

Выражения (5) и (6) позволяют вычислять производные от первого до Кп-го порядка. Другими словами, если необходимо вычислить производную (КПС + р)-го порядка по координате У или Y, то на основании (5) и (6) можно ограничиться вычислением произ водной порядка р.

Особенностью устройства является возможность восстановления системы ФМЛ, если в качестве исходных данных заданы производные этих ЛМЛ. При этом не изменяется характер связей компонентов устройства и характеристики информационных обменов. Возможность восстановления системы логиR N X

f,

tn-l

в первом режиме вводится по столбцам

-Гх1

L J

.0, ,„

,Un-

J

Г,

и на выходе формируется столбец мат,9 RAM . рицы

ЭХ

хГ

+ ху )( х(; )...

(хи - + x(kn-1)) x(kn-°1T

г.

Во втором режиме матрица RAN вводится по строкам в следующем порядке

г. xlj tj L k

XIJ

, л с J

при этом на выходе устройства форми 3RAN

руется строка матрицы

3V

г -, продифференцированная по координате Y, и записывается в виде:

5663656

ческих функций по логическим производным этой системы реализуется путем изменения дисциплины загрузки исходных данных.

Выражения (5) и (6) определяют процедуру восстановления (интегрирования) логических функций по их производным, которая заключается в (Кп - р)-кратном дифференцировании производной порядка р:

т(

10

J

RANdX

RAN

РХ

(7)

RANdY

,(-

RAN

3Y (v-P

(8)

20

25

Устройство работает в двух режимах . i,

Первый режим позволяет осуществить дифференциоование (интегрирование) логической функции по координате X, второй режим - по координате Y. Режим работы устройства задается путем организации способа загрузки блока 1 формирования наборов и заключается в следующем. Матрица исходных логических данных

- Г(Х ( + v i ,

9Y U - -2

40

+ х ; х

J,

т.е. начиная с элемента со старшим порядковым номером. Однако в резуль RAN тирующей матрице --- данная строс 1

ка будет записана следующим образом:

... (X

V- 1

i

1; Y 1 J

т.е. начиная с элемента с младшим порядковым номером.

Рассмотрим работу -устройства при вычислении производной первого порядка (р 1) системы логических функций.

Пусть необходимо вычислить первую производную системы из девяти логических функций двух переменных при

Вектор значений X Ј 11111 1 1 1 1 т вводится в oVioK 1 формирования наборов. С выходов блока 1 формирования наборов элементы векто- ра Xt поступают на входы суммато- ров 2 по модулю К. На фиг. 6 представлен операционный граф функционирования устройства в режиме дифференцирования системы логических функ ций по координате X, позволяющий записать дифференцирование системы логических функций поэлементно

Ш ХЫ + Х(. CmodK). (9) J з

На входы сумматоров 2 по модулю К поступают элементы вектора Хл , а

dXf,

на выходах формируется вектор

ЗХ

Например, в данном случае на первы зход сумматора 2, по модулю К поступает значение элемента X

Ю)

(и

1, а

на второй вход - X о 1, на выходе формируется нулевой элемент вектора

Ь, равный (Xle° + Х1в) 2. Аналогично функционируют все сумматоры 2 по модулю К. В результате формируется вектор

3Xfo

ЭХ

г(2 2 2 2 2 2 2 2 .

Затем в блок 1 формирования набо- 50 ров заносится вектор

,

2 2 2 2 2 2 2 2

и выполняется аналогичное вычисление

3Xt вектора - v v. При этом на выходы

о А

устройства передается вектор

К 3 заданной в виде матрицы RAN. по координате X:

ЗХ ЗХ

li- 1 1 1 1 1 1 1 1 2 Т

Эти вычисления выполняются для всех столбцов матрицы RAN. В рассматриваемом примере результат вычислений имеет вид:

212010212 212010212 211010112 210010012 3RAN 210010012 ЗХ212010212

211010112 211010112 102111201

Рассмотрим функционирование устройства, когда необходимо вычислить производную второго порядка системы логических функций по координате Y. Этот случай, как и предыдущий,.иллюстрируется на фиг. 9 и соответствует нижней окружности (последовательное дифференцирование выполняется по часовс ; стрелке). Система югических функций задается той же матрицей RAN, что и в предыдущем случае.

В блок 1 формирования наборов за носится вектор исходных данных

{,

1 21 1 1 1 1 2

Элементы вектора поступают на входы сумматоров 2 по модулю К. Представленный на фиг. 7 операционный граф функционирования устройства в режиме дифференцирования по координате Y позволяет записать дифференцирование системы логических функций как

,(П

j

Х(/ + (nodk).

(Ю)

В данном случае на

ров 2 формируется вектор

выходах суммато3V г

° to 34

00222200 1. Гри этом через коммутаторы 3 осуществляется пеJYJрезапись вектора

в блок 1 форi

мирования наборов. После этого выполняется дифференцирование вектора

Р в соответствии с СО- Результат

О i

av

021112011

сумматоров передается

2 через коммуна входы устОднако в результирующей

s(l

RAN

3U у . d it

ау

как указано выше, 20

записывается в ви3( YЈo 3Y

1 1 0 2 1 1 1 2 Oj.

Таким образом, аналогично вычис U)RAN лив другие строки матрицы ТуТГГ

получим

Вычисление логических интегралов выполняется аналогично в соответствии с (7) и (8), Пусть необходимо восстановить систему булевых функций, заданную матрицей

3U) RAN

В соответствии ходимо выполнить

с (3) и (7) необ- дифференцирование.

каждой из исходных булевых функций

(J О,

К

п

- 1) . В этом

случае устройство функционирует аналогично рассмотренным выше примерам

И)

вычисления производной порядков р и первого. На фиг. 10 приведен пример дифференцирования системы булевых функций, из которого также видно, что для восстановления исходной матрицы необходимо найти вторую производную

10

15

20

25

30

35

0

5

0

5

матрицы

«9(Я RAN

9Х111 Формула изобретения

Устройство для дифференцирования логических функций, содержащее блок синхронизации и блок формирования наборов, причем с первого по К -и (где К - значность логической функции, п - число переменных логической функции) информационные входы устройства подключены соответственно к информационным входам с первого по К-й первой группы блока формирования наборов, первый и второй управляющие входы которого подключены соответственно к первому и второму выходам блока синхронизации, вход запуска- останова и вход режима которого подключены соответственно к входу запуска-останова и к (К + 1)-му информационному входу устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет обработки систем логических функций, оно содержит с первого по (Кп - 1)-й сумматоры по модулю К и с первого по Кп-й коммутаторы, причем первый выход блока формирования наборов подключен к первому информационному входу первого сумматора по модулю К, а-й выход блока формирования наборов (где а 2, ..., Кп -1) подключен к первому информационному входу а-го сумматора по модулю Кик второму информационному входу (а + + 1)го сумматора по модулю К, выход сумматора по модулю К (где b 1, ..., К - 1) подключен к информационному входу b-го коммутатора, Кп-й выход блока формирования наборов подключен к второму информационному входу (К - 1)-го сумматора по модулю Кик информационному входу К11-го коммутатора, первый выход с-го коммутатора (где с 1, ..., Кп) подключен к с-му информационному входу второй группы блока формирования наборов, третий выход блока синхронизации подключен к управляющим входам коммутаторов с первого по К -и, второй выход с-го коммутатора подключен к с-му выходу устройства.

-

Фие.З

LT

О (

vD

LT

k

at- Is

lig Isgll

«2

foh/K/j. ) пмлгоу fioHhDHCoaow ллЬхнбсЬ вмзшэлз

we ,-u

1i

| 0 |

|

SU168925A1 | |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Устройство для вычисления булевых производных | 1985 |

|

SU1277089A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1990-05-23—Публикация

1988-08-10—Подача