Ё

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для дифференцирования логических функций | 1988 |

|

SU1566365A1 |

| Устройство для вычисления логических производных многозначных данных | 1990 |

|

SU1837277A1 |

| Устройство для вычисления логических производных многозначных данных | 1989 |

|

SU1670690A1 |

| СИСТЕМА ДЛЯ КОДИРОВАНИЯ И ДЕКОДИРОВАНИЯ С ИСПРАВЛЕНИЕМ ОШИБОК | 1991 |

|

RU2007042C1 |

| Многофункциональное вычислительное устройство | 1985 |

|

SU1293727A1 |

| Устройство для умножения матриц | 1987 |

|

SU1471201A1 |

| Модуль однородной вычислительной структуры | 1987 |

|

SU1495809A1 |

| Кодек на основе кода Рида - Маллера первого порядка | 1990 |

|

SU1777243A1 |

| Модуль для вычисления логических производных | 1989 |

|

SU1730617A1 |

| Устройство для матричных операций | 1987 |

|

SU1429127A1 |

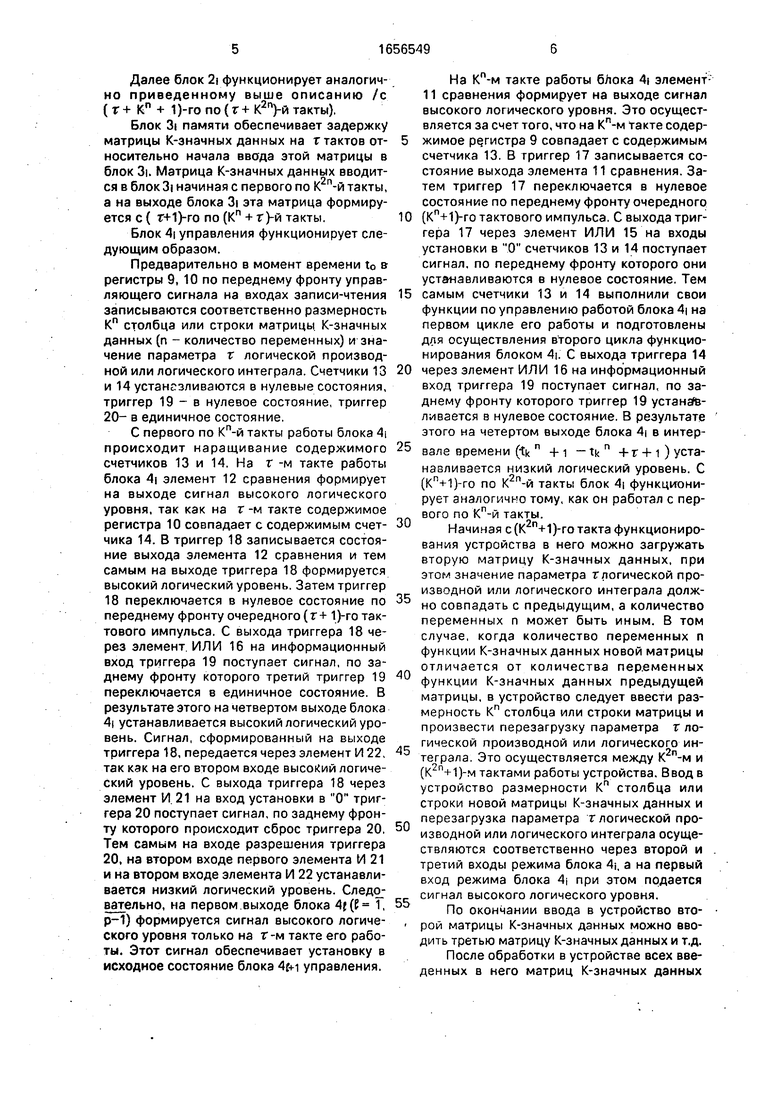

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной поддержки вычислений в системах синтеза, анализа и контроля цифровых автоматов, диагностики цифровых устройств, обработки изображений, сжатия данных, синтеза топологии БИС и СБИС. Цель изобретения - расширение функциональных возможностей устройства за счет обработки многозначных данных. Устройство содержит генератор 1 тактовых импульсов, р операционных блоков 2, р блоков 3 памяти и р блоков 4 управления, где р- порядок логической производной или логического интеграла.4 ил.

С

сл а сл

4 О

фиг.1

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной поддержки вычислений в системах синтеза, анализа, контроля и диагностики цифровых автоматов, об- работки изображений, сжатия данных, синтеза топологии больших и сверхбольших интегральных схем.

Целью изобретения является расширение функциональных возможностей устрой- ства за счет обработки многозначных данных.

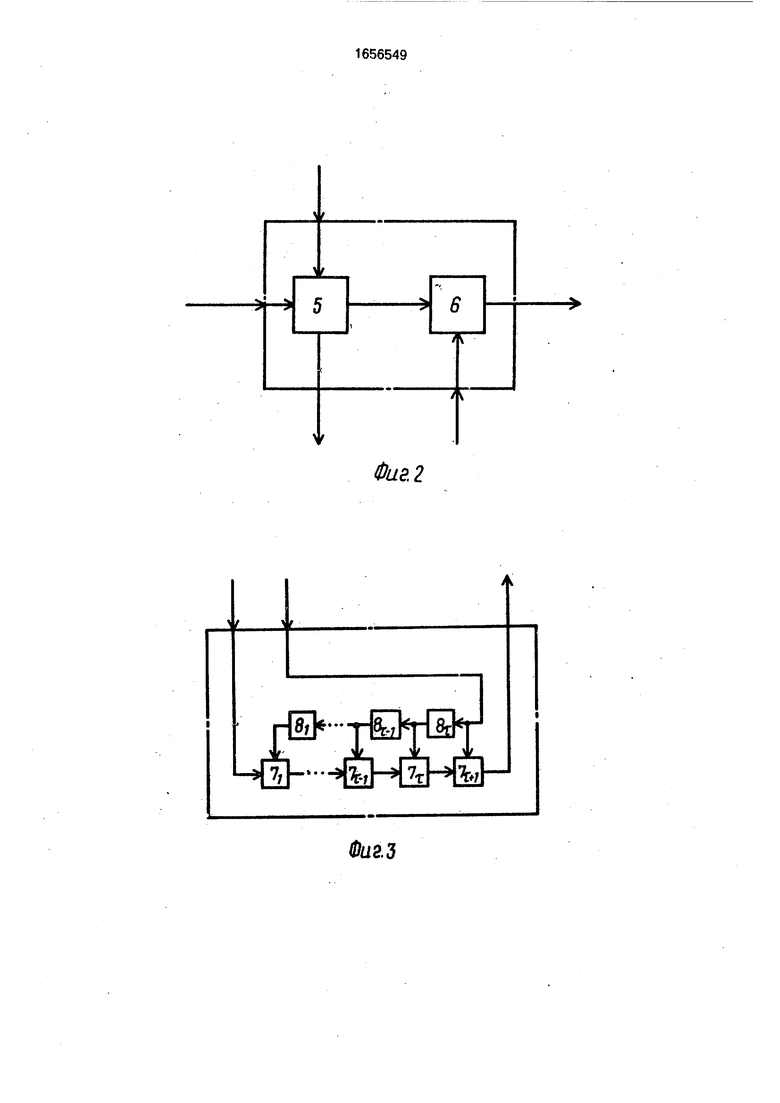

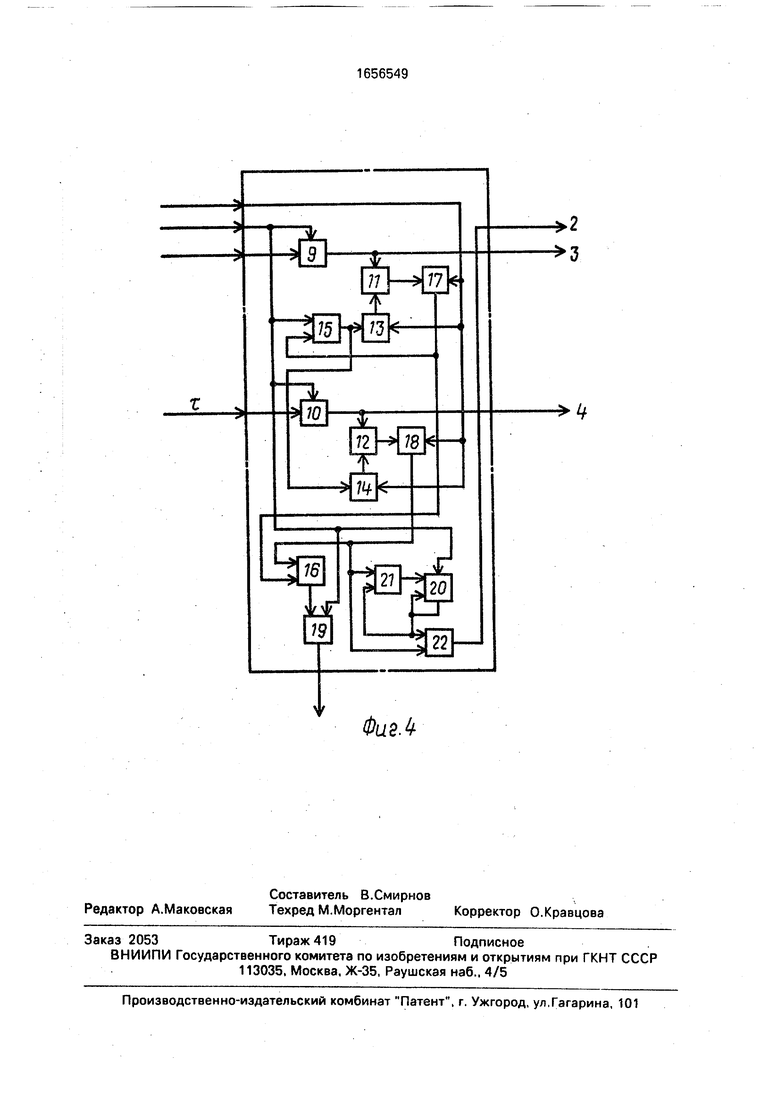

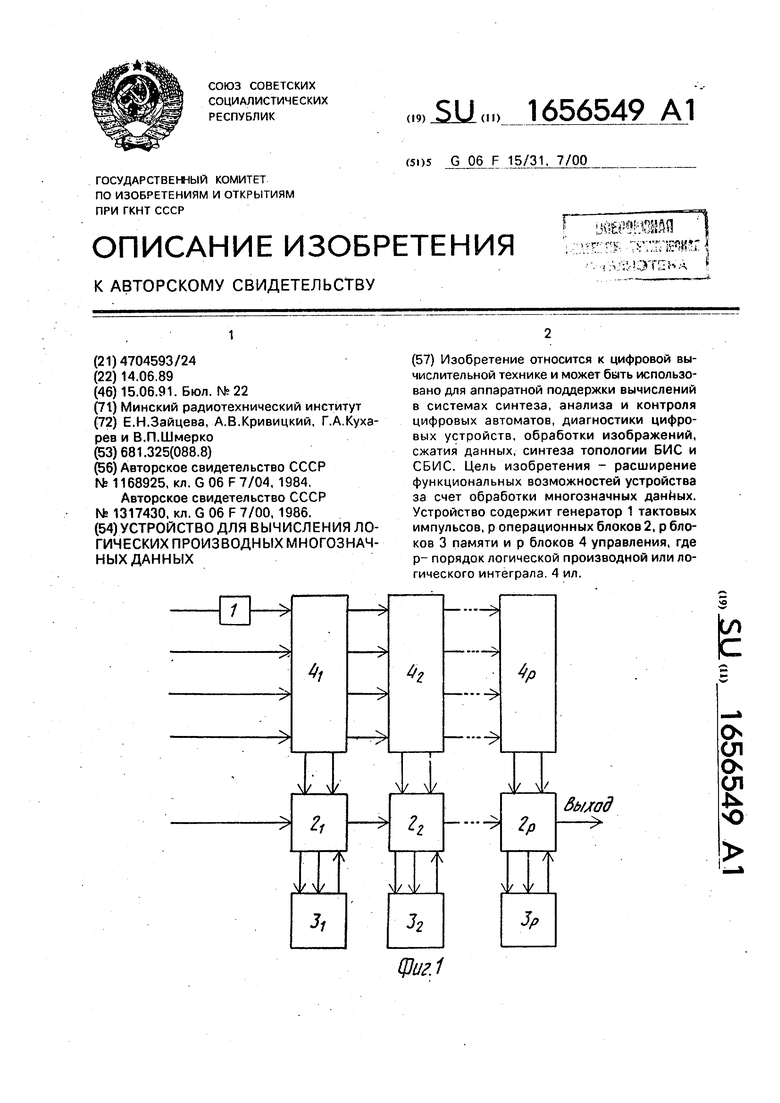

На фиг. 1 представлена схема устройства; на фиг. 2 - схема операционного блока; на фиг. 3 - схема блока памяти; на фиг. 4схема блока управления.

Устройство содержит генератор 1 тактовых импульсов, операционные блоки , где р - порядок логической производной/интеграла, блоки 3i-3p памяти, блоки управления. Каждый операционный блок содержит коммутатор 5 и сумматор 6 по модулю К, где К - значность данных. Каждый блок памяти содержит регистры 7i- 7т , где г-значение параметра логической производной/интеграла, и элементы 8i-8r задержки. Каждый блок управления содержит первый и второй регистры 9 и 10, первый и второй элементы 11 и 12 сравнения, первый и второй счетчики 13 и 14, первый и второй элементы ИЛИ 15 и 16, с первого по четвертый триггеры 17 - 20, первый и второй элементы И 21 и 22.

Операционный блок 2i (1 - 17р) обеспечивает однократное вычисление логической производной с параметром г системы Позначных данных по координате X и Y в соответствии с выражениями для р-кратных логических производных с параметром г, определяемых матричными операторами вида:

кп , (t) X „п , ,., f -§« ««--iiSiTfrr Ч m

8(fxv 3fMXK ..«)

(С| /J ьЛ

-Ypto AV(modk), (2

3(ЈY)IP) 3(4 VI

где MI n - матрица логической производной с параметром т. Исходными данными для 1-го операционного блока является сие- тема К-значных данных, заданная матрицей

g(i-0X

3(0х

,(, -0

(3)

(при логической обработке по координате X) или матрицей вида 0 г,- v

О к

3((

(4)

0

5

0 5 0

5 0

(при логической обработке по координате Y). Причем справедливо следующее соотношение:

з(о1хкп

5

0

э(о1х„«

-х

к

Э(Јх)(01 Э(ОГ)ГО) то есть для блока 2i исходными данными является система К-значных данных, заданная матрицей xk .

Блок 4i управления предназначен для синхронизации функционирования блоков 2i и 3i. С первого по Кп-й такты работы блока 2) на его первый информационный вход поэлементно подается первый столбец или строка матрицы многозначных данных.

С первого по т-и такты первые т элементов первого столбца или первой строки матрицы многозначных данных (3) или (4) пересылаются через коммутатор 5 с его информационного входа на его второй выход. Первые г тактов работы блока 2 на первый и второй входы сумматора 6 по модулю К информация не поступает, что равносильно подаче на первый и второй входы сумматора 6 по модулю К блока 2i нулевых элементов.

С ( т+ 1 )-го по Кп-й такты коммутатор 5 осуществляет пересылку данных со своего информационного входа на первый и второй выходы одновременно, а на второй информационный вход сумматора б по модулю К поэлементно поступают (Кп - г) К-значных данных, принадлежащих первому столбцу или строке матрицы (3) или (4) соответственно.

С (Кп + 1)-го по ( т + Кп)-й такты коммутатор 5 пересылает данные со своего информационного входа на второй выход. С(КП + 1)по 2Кп-й такты на первый информационный вход блока 2| подается второй столбец или вторая строка матрицы многозначных данных (3) или (4) соответственно.

С (Г+ 1)-го по(г + Кп)-й такт на первый информационный вход сумматора 6 по модулю К поступает поэлементно первый столбец или первая строка матрицы многозначных данных (3) или (4).

С (г + 1)-ro no (f- Кп)-й такт на выходе сумматора 6 по модулю К формируется первый столбец матрицы К-значных данных, имеющий вид

,

3(ЈХ);1

или первая строка матрицы К-значных данных вида0(И

кп

Э(У)

(Я

(6)

Матрицы (5) и (6) являются логическими производными первого порядка матриц (3) и (4) соответственно.

Далее блок 2i функционирует аналогично приведенному выше описанию /с ( г + К + 1 )-го по (г + К2п)-й такты).

Блок 3i памяти обеспечивает задержку матрицы К-значных данных на г тактов от- носительно начала ввода этой матрицы в блок 3|. Матрица К-значных данных вводится в блок 3i начиная с первого по К2п-й такты, а на выходе блока 3i эта матрица формируется с ( т+1)-го по (Кп + г)-й такты.

Блок 4| управления функционирует следующим образом.

Предварительно в момент времени to в регистры 9, 10 по переднему фронту управляющего сигнала на входах записи-чтения записываются соответственно размерность Кп столбца или строки матрицы К-значных данных (п - количество переменных) и значение параметра г логической производной или логического интеграла. Счетчики 13 и 14 устансзливаются в нулевые состояния, триггер 19 - в нулевое состояние, триггер 20- в единичное состояние.

С первого по Кп-й такты работы блока 4; происходит наращивание содержимого счетчиков 13 и 14. На г -м такте работы блока 4| элемент 12 сравнения формирует на выходе сигнал высокого логического уровня, так как на г -м такте содержимое регистра 10 совпадает с содержимым счет- чика 14. В триггер 18 записывается состояние выхода элемента 12 сравнения и тем самым на выходе триггера 18 формируется высокий логический уровень. Затем триггер 18 переключается в нулевое состояние по переднему фронту очередного (г + 1)-го тактового импульса. С выхода триггера 18 через элемент ИЛИ 16 на информационный вход триггера 19 поступает сигнал, по заднему фронту которого третий триггер 19 переключается в единичное состояние. В результате этого на четвертом выходе блока 4| устанавливается высокий логический уровень. Сигнал, сформированный на выходе триггера 18, передается через элемент И 22, так как на его втором входе высокий логический уровень. С выхода триггера 18 через элемент И 21 на вход установки в О триггера 20 поступает сигнал, по заднему фронту которого происходит сброс триггера 20. Тем самым на входе разрешения триггера 20, на втором входе первого элемента И 21 и на втором входе элемента И 22 устанавливается низкий логический уровень. Следо; вательно, на первом выходе блока 4f(f 1, р-1) формируется сигнал высокого логического уровня только на т-м такте его работы. Этот сигнал обеспечивает установку в исходное состояние блока 4м управления.

На Кп-м такте работы блока 4i элемент 11 сравнения формирует на выходе сигнал высокого логического уровня. Это осуществляется за счет того, что на Кп-м такте содержимое регистра 9 совпадает с содержимым счетчика 13. В триггер 17 записывается состояние выхода элемента 11 сравнения. Затем триггер 17 переключается в нулевое состояние по переднему фронту очередного (Кп+1)-го тактового импульса. С выхода триггера 17 через элемент ИЛИ 15 на входы установки в О счетчиков 13 и 14 поступает сигнал, по переднему фронту которого они устанавливаются в нулевое состояние. Тем самым счетчики 13 и 14 выполнили свои функции по управлению работой блока 4| на первом цикле его работы и подготовлены для осуществления второго цикла функционирования блоком 4i. С выхода триггера 14 через элемент ИЛИ 16 на информационный вход триггера 19 поступает сигнал, по заднему фронту которого триггер 19 устанавливается в нулевое состояние. В результате этого на четертом выходе блока 4| в интервале времени (ik n + i - tk n + г + 1 ) устанавливается низкий логический уровень. С (Кп+1)-го по К п-й такты блок 4| функционирует аналогично тому, как он работал с первого по Кп-й такты.

Начиная с (К п+1)-го такта функционирования устройства в него можно загружать вторую матрицу К-значных данных, при этом значение параметра г логической производной или логического интеграла должно совпадать с предыдущим, а количество переменных n может быть иным. В том случае, когда количество переменных n функции К-значных данных новой матрицы отличается от количества переменных функции К-значных данных предыдущей матрицы, в устройство следует ввести размерность Кп столбца или строки матрицы и произвести перезагрузку параметра т логической производной или логического интеграла. Это осуществляется между К -м и (К2п+1)-м тактами работы устройства. Ввод в устройство размерности Кп столбца или строки новой матрицы К-значных данных и перезагрузка параметра г логической производной или логического интеграла осуществляются соответственно через второй и третий входы режима блока 4j. а на первый вход режима блока 4 при этом подается сигнал высокого логического уровня.

По окончании ввода в устройство второй матрицы К-значных данных можно вводить третью матрицу К-значных данных и т.д.

После обработки в устройстве всех введенных в него матриц К-значных данных

устройство останавливается путем подачи на его вход запуска/останова сигнала высокого логического уровня,

Формула изобретения Устройство для вычисления логических производных многозначных данных, содержащее первый блок управления, первый операционный блок и генератор тактовых импульсов, причем информационный вход и вход запуска-останова устройства подключены соответственно к первому информационному входу первого операционного блока и к входу запуска-останова генератора тактовых импульсов, выход которого подключен к входу синхронизации первого блока управления, отличающееся тем, что, с целью расширения функциональных возможностей за счет обработки многозначных данных, оно содержит с второго по р-й блоки управления (где р - порядок логической производной интеграла), с второго по р-й операционные блоки и р блоков памяти, причем выход генератора тактовых импульсов подключен к входам синхронизации блоков управления с второго по р-й и к входам синхронизации блоков памяти с первого по р-й, управляющий вход, вход размерности и вход параметра логической производной интеграла устройства подключены соответственно к первому, второму и третьему входам режима первого блока управления, первый, второй, третий и четвертый выходы с-го блока управления (где с

1р-1) подключены соответственно к

первому, второму, третьему входам режима (с+1)-го блока управления и управляющему входу с-го операционного блока, четвертый выход р-го блока управления подключен к управляющему входу р-го операционного блока, первый и второй выходы с-го операционного блока подключены соответственно к первому инфррмационному входу (с+1)-го операционного блока и к информационному входу с-го блока памяти, первый и второй выходы р-го операционного блока подключены соответственно к выходу результата устройства и к информационному входу р-го блока памяти, выход b-го блока

памяти (где ) подключен к второму

информационному входу b-го операционного блока, причем каждый операционный блок содержит коммутатор и сумматор по модулю К (где К-значность данных), причем в каждом операционном блоке первый и второй информационные входы операционного блока подключены соответственно к

информационному входу коммутатора и к первому информационному входу сумматора по модулю-К, выход которого подключен е первому выходу операционного блока, управляющий вход которого подключен к управляющему входу коммутатора, первый и второй выходы которого подключены соответственно к второму информационному входу сумматора по модулю Кик второму

выходу операционного блока, причем каждый блок управления содержит два регистра, два элемента сравнения, два счетчика, два элемента ИЛИ, четыре триггера и два элемента И, причем в каждом блоке управления вход синхронизации блока управления подключен к входам установки в О первого и второго триггеров, к счетным входам первого и второго счетчиков, первый вход режима блока управления подключен к

входам записи-чтения первого и второго регистров, к входу установки в О третьего триггера, к входу установки в 1 четвертого триггера и к первому входу первого элемента ИЛИ, выход которого подключен к входам

установки в О первого и второго счетчиков, информационные выходы которых подключены соответственно к первым входам первого и второго элементов сравнения, выходы которых подключены соответственно к входам установки в 1 первого и второго триггеров, выход первого триггера подключен к второму входу первого элемента ИЛИ и к первому входу второго элемента ИЛИ, выход которого подключен к информационному входу третьего триггера, выход второго триггера подключен к второму входу второго элемента ИЛИ, к первым входам первого и второго элементов И, выходы которых подключены соответственно к

входу установки в О четвертого триггера и к первому выходу блока управления, выход четвертого триггера подключен к входу разрешения четвертого триггера и к вторым входам первого и второго элементов И,

второй вход режима блока управления подключен к информационному входу первого регистра, выход которого подключен к второму входу первого элемента сравнения и к второму выходу блока управления,

третий вход режима которого подключен к информационному входу второго регистра, выход которого подключен к второму входу второго элемента сравнения и к третьему выходу блока управления, четвертый выход которого подключен к выходу третьего триггера.

1 гпф

6fr9999l

Фиг. 4

| Устройство для вычисления булевых производных | 1983 |

|

SU1168925A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-06-15—Публикация

1989-06-14—Подача