СП

с

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления логических производных многозначных данных | 1990 |

|

SU1837277A1 |

| Модуль для вычисления логических производных | 1989 |

|

SU1730617A1 |

| Устройство для вычисления логических производных многозначных данных | 1989 |

|

SU1656549A1 |

| Устройство для дифференцирования логических функций | 1988 |

|

SU1566365A1 |

| Устройство для распознавания на линейность булевых функций | 1990 |

|

SU1756879A1 |

| Устройство для обработки приращений вектора | 1984 |

|

SU1203510A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

| Модульное устройство для программного управления и контроля | 1988 |

|

SU1647519A1 |

| Программируемое многофункциональное аналого-цифровое устройство сопряжения | 1986 |

|

SU1425635A1 |

| Устройство для сопряжения эвм с абонентами | 1984 |

|

SU1215114A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано для аппаратной поддержки вычислений в системах синтеза и анализа цифровых автоматов, диагностики цифровых устройств, сжатия данных, обработки изображений, управления роботами-манипуляторами, синтеза топологии БИС. Цель изобретения - расширение функциональных возможностей за счет логической обработки многозначных данных. Поставленная цель достигается тем, что устроство содержит блоки 11 - 1N управления, операционные блоки 21 - 2N и блоки 31 - 3N памяти, где N - число переменных функций, описывающей многозначные данные. 3 ил.

(

VJ

о о ю о

Изобретение относится к цифровой вычислительной технике и может быть использовано для синтеза и анализа цифровых автоматов, диагностики цифровых устройств, сжатия данных, обработки изображений, управления роботами-манипуляторами, синтеза топологии больших интегральных схем.

Целью изобретения является расширение функциональных возможностей за счет логической обработки многозначных данных.

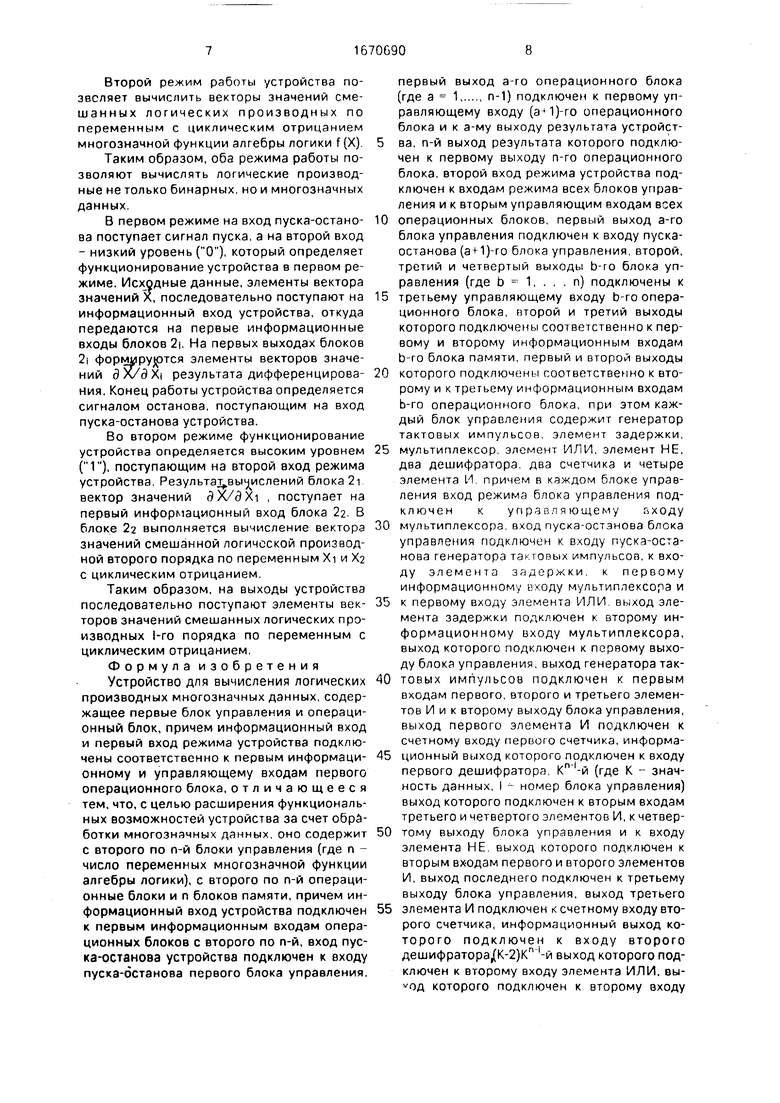

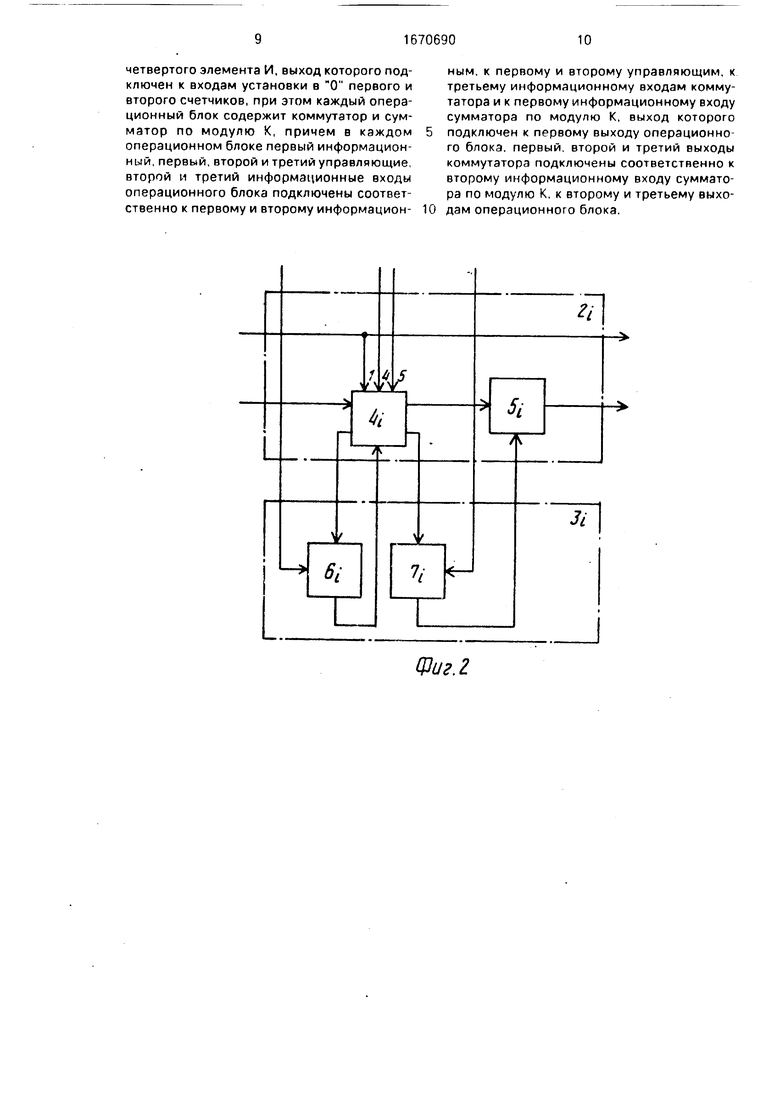

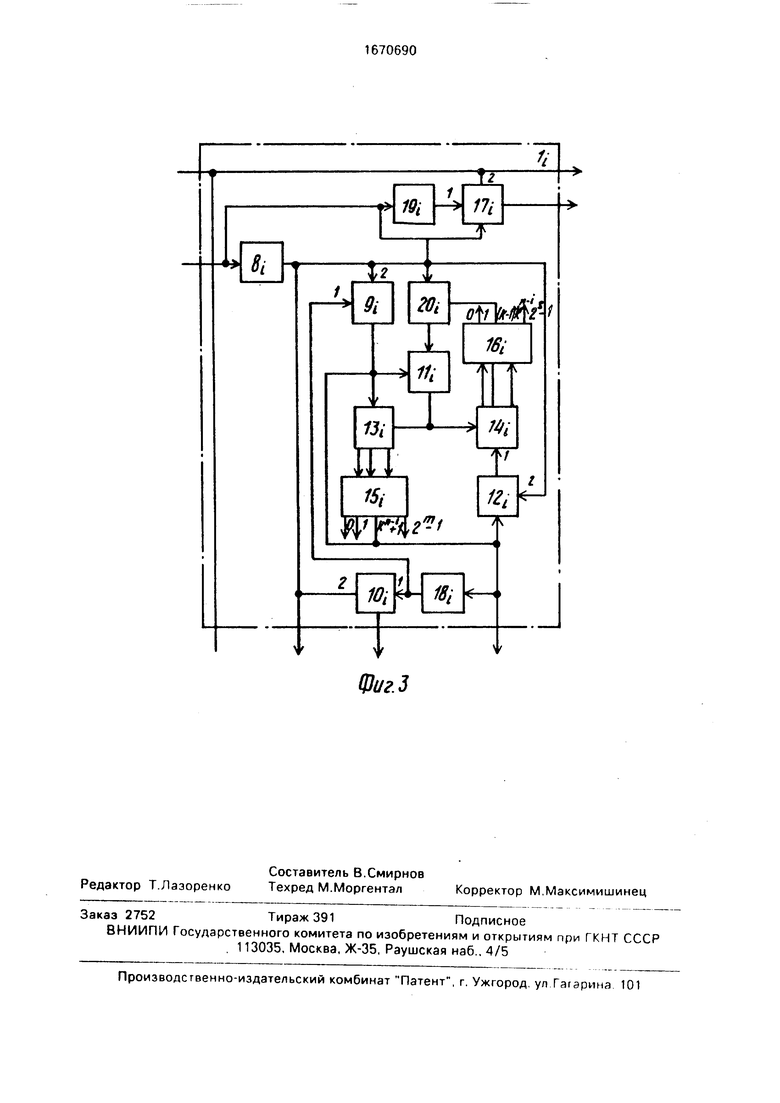

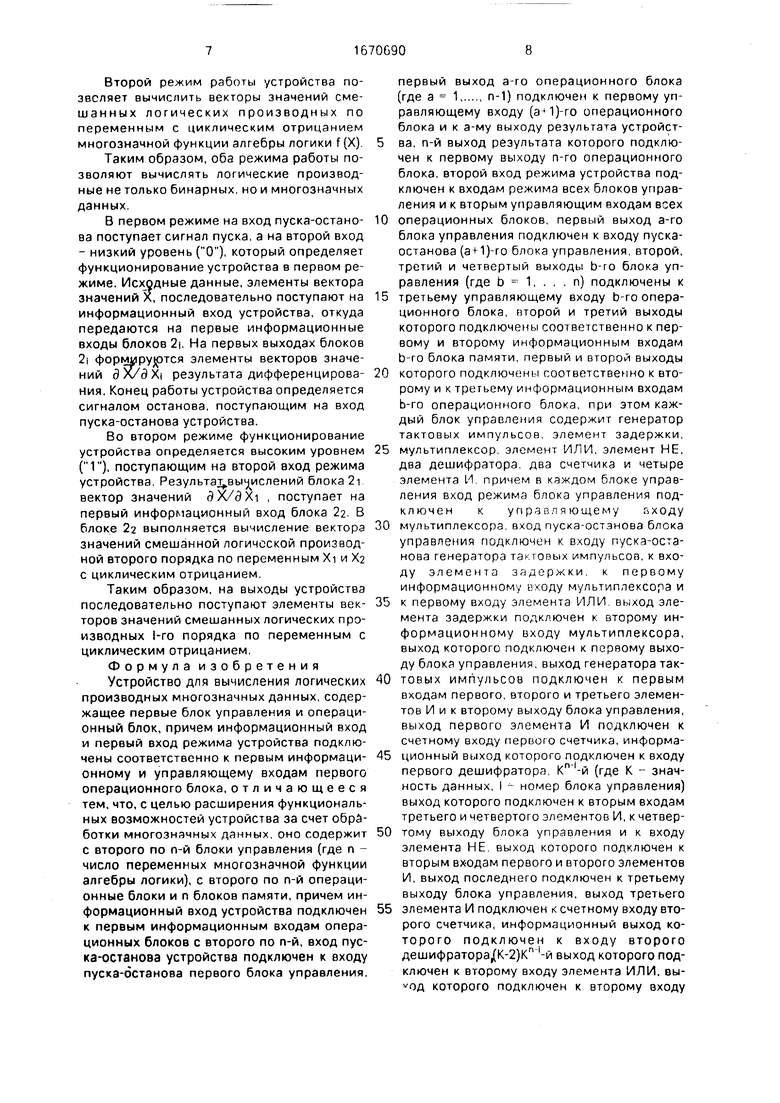

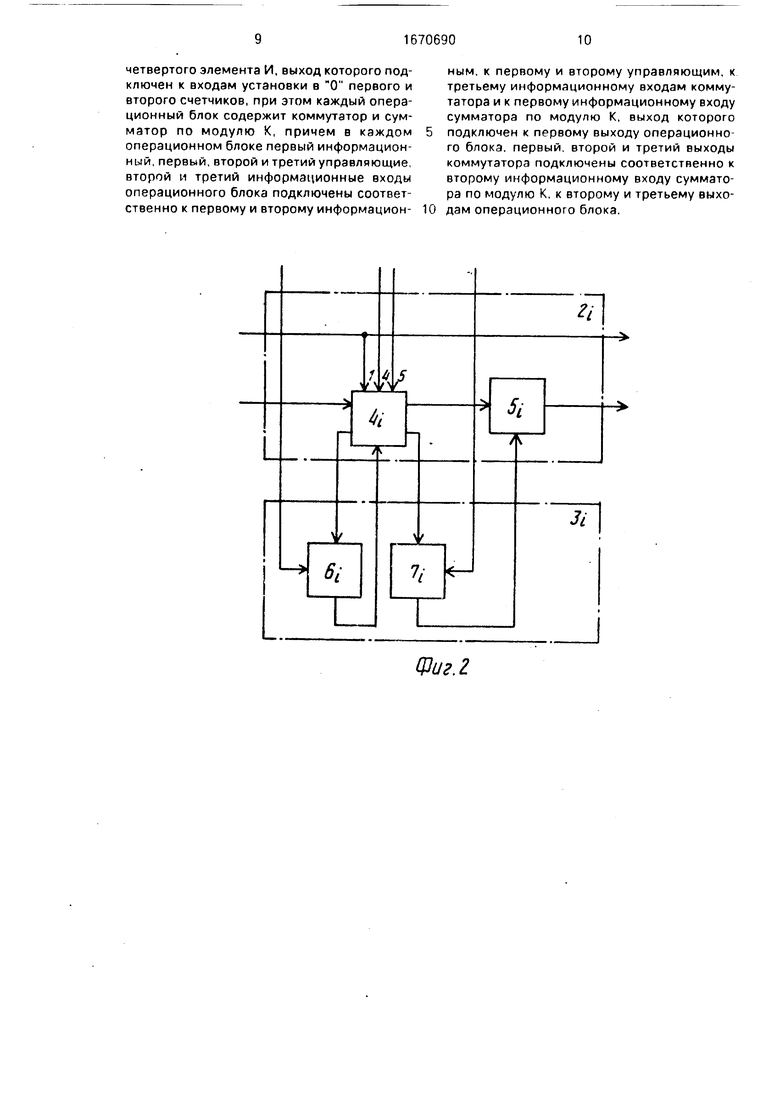

На фиг.1 представлена схема устройства; на фиг.2 - схемы блоков памяти и операционного блока; на фиг.З - схема блока управления.

Устройство содержит блоки 1i-1n управления, операционные блоки 2г-2п и блоки 3-гЗп памяти, где п - число переменных многозначной функции алгебры логики. Каждый операционный блок содержит коммутатор 4 и сумматор 5 по модулю К (где К - значность данных). Каждый блок памяти содержит первый и второй узлы 6 и 7 регистровой памяти. Каждый блок управления содержит генератор 8 тактовых импульсов, с первого по четвертый элементы И 9-12, первый 13 и второй 14 счетчики, первый 15 и второй 16 дешифраторы, мультиплексор 17, элемент НЕ 18, элемент 19 задержки и элемент ИЛИ 20.

Операционный блок 1 (где I 1.. .п) предназначен для вычисления вектора значений д X/д Х| логической производной по 1-й переменной Х| с циклическим огрицани- ем в первом режиме и вектора значений смешанной логической производной 1-го порядка по переменным с циклическим отрицанием во втором режиме. В первом режиме работы исходными данными для блока 2| являются элементы вектора значений X многозначной функции алгебры логики, во втором - результат вычислений блока 2м (вектор значений логической производной (1-1)-го порядка по переменным с цикли- ческим отрицанием).

Первый режим работы блока 1i определяется низким уровнем О, который подается на вход режима блока 1i в момент времени to. Во втором режиме работы на вход режима блока 1| в момент времени to подается высокий уровень 1. Одновременно сигнал с входа режима блока } поступает на управляющий вход мультиплексора 17|. При этом на выход мультиплексора 17( передается информация с РГО перпого информационного входа. Сигнал пуска поступает на вход пуска-останова генератора 8i тактовых импульсов и через мультиплексор

17| на первый выход блока 1| в момент времени t0, откуда поступает на вход пуска-ос- танова следующего (1 + 1)-го блока управления.

Начиная с момента времени t0 до момента времени tp, где р-Ки(Кп -i(K-1)KnV Кп -1, генератора 8i импульсов формирует последовательность импульсов которые поступают на первый вход элемента И 9i, элемента И 101 и элемента И 12i а также на второй выход блока 1ь

На первый вход элемента И 10i поступает высокий логический уровень,а на второй вход- синхроимпульсы с выхода генератора 8i импульсов. На выходе элемента И 10i формируется последовательность импульсов которые поступают на третий выход блока 1: и служат для управления работой 1-го блока 3i.

В момент времени t кп когда на выходах счетчика 13i формируется двоичный эквивалент числа Кп +1. на соответствующем выходе дешифратора 15i формируется высокий уровень ( 1), который поступает на вход элемента НЕ 18i, с выхода которого низкий логический уровень передается на первые входы элементов И 9| и 10i, на выходе котог.ых формируется низкий логический уровень Вследствие этого счетчик 13( фиксирует состояние, в котором он находился в момент времениt . Одновременно высокий уровень с вылода дешифратооа 15, поступает на первые входы гов И 12i, 11i и на четвертый выход блока 1 В результате этого с выхода лемента И 12| на счетный вход сметчика 14| поступают синхроимпульсы.

,п I

В момент времени ti, где I К + (К-1)К когда на выходах счетчика 14: формируется двоичный эквивалент числа (К-1)КП1, на соответствующем выходе дешифратора 16i формируется высокий уровень (1), который поступает на второй вход элемента ИЛИ 20,, с выхода которого высокий уровень (1) поступает на второй вход элемента И 1 11, на выходе которого устанавливается высокий логический уровень, поступающий на вход установки в ноль счетчиков 13i и 14|, После этого на выхода/ дешифраторов 15i и 16i устанавливаются низкие логические уровни.

Цикл работы блока 1| повторяется К 1 раз. начиная с момента Бремени С момента времени т «м | АО V функционирование блока 1| аналогично его работе с момента времени t0 по t п В момент времени т на вход пуска-пстзчипа блока 1; полается сигнал останова случащий признаком конца работы блока 1,

1

Во втором режиме в момент времени ь высокий уровень (1) поступает на управляющий вход мультиплексора 17, Вследствие этего данные на выход мультиплексора 17( поступают с его второю информационного входа Одновременно на вход пуска-останова блока 1i подается сигнал пуска, который поступает на вход пуска-осганова генерато ратактовыхимпульсов8|Ина вход элемента 19i задержки. С ьылидь с лемен(а 9| задержки через время Л г - К 1 /f. где f - частота следования импульсов на выходе генератора 8i, сигнал пуска поступает на второй информационный вход мультиплексора 17|, а с его выхода - на первый выход блока 1| В остальные моменты времени функционирование блока 1i во втором режиме аналогично его функционированию в первом режиме

Блок 2i работает следующим образом в двух режимах

В первом режиме исходные данные вектор значений X функции f(X), поступают с первого информационного входа блока 2, на первый информационный вход коммутатора 4|

Начиная с момента времени t0 на первый и второй управляющие входы коммута торэ 4, поступают низкие уровни В результате информация передается с первого информационного входа коммутатора 1i на его второй и i р , ий вылоды и с третьего информационного коммутаюра на иго первый вь од Исходные данные с второго и третьего выводов коммутатора 4, поступают соответственно на второй и третий выходы блока 2,

С момента времени t кг на первом управляющем входе коммутатора 4, устанавливается высокий логический уровень Вследстсие этого информация передается с первого информационного входа коммутатора 4| на его первый и третий выходы На донном jTcine исходные данные поступают, с первого выхода коммутатора 4, на второй информационный вход сумматора 5i по модулю Кис третьего информационного входа блока 2i на первый информационный вход сумматора 5i по модулю К Результат суммирования с выхода сумматора 5 по модулю К поступает на первый выход блока 2,

Цикл работы блока 2,, начиная с момента времени ц повторяется Ки-1 раз. Начиная с момента времени ) no tp. Функционирование блока 2 аналогично его работе с момента времени to по t «n .

Во втором режиме, начиная с момента времени to. на первый управляющий вход

0

5

0

5

0

0

Г,

0

5

коммутатора 4, поступает высокий уровень а на второй управляющий вход коммутатора 4, низкий уровень В результате этого информация с первого информационного вхо да коммутатора 4| передается на его второй и третий выходы, а с третьего информационного входа коммутатора 4| на его первый выход С второго и третьего выходов коммутатора 4, исходные данные поступают соот вР1Ственно на второй и третий выходы блока 2i

С момента времени на втором управляющем входе коммутатора 4| форми руется высокий логический уровень. Вследствие этого информация с второго информационного входа коммутатора 4, передается на его первый и третий выходы. На данном этапе функционирования исходные данные поступают на первый и второй информационные входы сумматора 5i по моду лю К, а результат суммирования с выхода сумматора по модулю К поступает на первый выход блока 2i. Цикл работы блока 2, повторяется К 1-1 раз, начиная с момента

времени ti С момента времени t« | по tp функционирование блока 2, аналогично его работе с момента времени to по t «n

Начиная с момента времени to до момента 1кп в узел 6, pei истровой памяти и в узел 7| регистровой памяти записывается информация поступающая на информационные илоды лих узлие

С момента времени t i/1 - 1 в течение {К 1)К тактов работы блока 3i запись и считывание информации из узла 6i не осущест- вляегся Однако узел 7, продолжает Функционировать: информация, поступающая на его информационный вход, последовательно проходит через все регистры узла 7, и поступает на его выход. С момента времени ti на управляющий вход узла 6, посту- пает последовательность импульсов Вследствие этого содержимое регистров уз- па С, последовательно поступает на его выход Период работы запоминающей ячейки 3, с момента времени t «n по tm, где m 2КП1 + (К-1) повторяется К -1 раз и заканчивается в момент времени tp

Устройство для вычисления логических производных многозначных данных работает следующим образом в двух режимах.

Первый режим работы прзцоляет вычислить векторы значений ) Х/г У Х| логической производной по переменной X, с циклическим отрицанием многозначной функции алгебры логики f(X) В блоке 2, вычисляется логическая производная по переменной Xi с циклическим отрицанием

Второй режим работы устройства позволяет вычислить векторы значений смешанных логических производных по переменным с циклическим отрицанием многозначной функции алгебры логики f (X)

Таким образом, оба режима работы позволяют вычислять логические производные не только бинарных, но и многозначных данных.

В первом режиме на вход пуска-останова поступает сигнал пуска, а на второй вход - низкий уровень (О), который определяет функционирование устройства в первом режиме. Исходные данные, элементы вектора значений л, последовательно поступают на информационный вход устройства, откуда передаются на первые информационные входы блоков 2|. На первых выходах блоков 2i формируется элементы векторов значений dX/dXi результата дифференцирования. Конец работы устройства определяется сигналом останова, поступающим на вход пуска-останова устройства.

Во втором режиме функционирование устройства определяется высоким уровнем (1), поступающим на второй вход режима устройства. Результат выч ислений блока 2i вектор значений ЭХ/dXi , поступает на первый информационный вход блока 22. В блоке 22 выполняется вычисление вектора значений смешанной логической производной второго порядка по переменным Xi и Ха с циклическим отрицанием.

Таким образом, на выходы устройства последовательно поступают элементы векторов значений смешанных логических производных 1-го порядка по переменным с циклическим отрицанием.

Формула изобретения

Устройство для вычисления логических производных многозначных данных, содержащее первые блок управления и операционный блок, причем информационный вход и первый вход режима устройства подключены соответственно к первым информационному и управляющему входам первого операционного блока, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обработки многозначных данных, оно содержит с второго по n-й блоки управления (где п - число переменных многозначной функции алгебры логики), с второго по n-й операционные блоки и п блоков памяти, причем информационный вход устройства подключен к первым информационным входам операционных блоков с второго по n-й, вход пуска-останова устройства подключен к входу пуска-останова первого блока управления,

первый выход а-го операционного блока (где а 1, п-1) подключен к первому управляющему входу (а41)-го операционного блока и к а-му выходу результата устройства, n-й выход результата которого подключен к первому выходу п-го операционного блока, второй вход режима устройства подключен к входам режима всех блоков управления и к вторым управляющим входам всех

0 операционных блоков, первый выход а-го блока управления подключен к входу пуска- останова (а+1)-го блока управления, второй, третий и четвертый выходы b-го блока управления (где b - 1, . . . п) подключены к

5 третьему управляющему входу b-го операционного блока, второй и третий выходы которого подключены соответственно к первому и второму информационным входам b-го блока памяти, первый и второй выходы

0 которого подключены соответственно к второму и к третьему информационным входам b-го операционного блока, при этом каждый блок управления содержит генератор тактовых импульсов, элемент задержки,

5 мультиплексор, элемент ИЛИ, элемент НЕ, два дешифратора, два счетчика и четыре элемента И причем в каждом блоке управления вход режима блока управления подключен к управляющему входу

0 мультиплексора, вход пуска-остэнова блока управления подключен к входу пуска-останова генератора тактовых импульсов, к входу элемента задержки, к первому информационному еходу мультиплексора и

5 к первому входу элемента ИЛИ выход элемента задержки подключен к второму информационному входу мультиплексора, выход которого подключен к первому выходу блока управления, выход генератора так0 товых импульсов подключен к первым входам первого, второго и третьего элементов И и к второму выходу блока управления, выход первого элемента И подключен к счетному входу первого счетчика, информа5 ционный выход которого подключен к входу первого дешифратора, (где К - знач- ность данных, I - номер блока управления) выход которого подключен к вторым входам третьего и четвертого элементов И, к четвер0 тому выходу блока управления и к входу элемента НЕ выход которого подключен к вторым входам первого и второго элементов И, выход последнего подключен к третьему выходу блока управления, выход третьего

5 элемента И подключен к счетному входу второго счетчика, информационный выход которого подключен к входу второго дешифратора/К-2)Кп -и выход которого подключен к второму входу элемента ИЛИ, вы- од которого подключен к второму входу

четвертого элемента И, выход которого подключен к входам установки в О первого и второго счетчиков, при этом каждый операционный блок содержит коммутатор и сумматор по модулю К, причем в каждом операционном блоке первый информационный, первый, второй и третий управляющие, второй и третий информационные входы операционного блока подключены соответственно к первому и второму информацион0

ным. к первому и второму управляющим, к третьему информационному входам коммутатора и к первому информационному входу сумматора по модулю К, выход которого подключен к первому выходу операционного блока, первый, второй и третий выходы коммутатора подключены соответственно к второму информационному входу сумматора по модулю К, к второму и третьему выходам операционного блока.

Л

Si

А

7/

Фиг. 2

Щиг.З

| Устройство для вычисления булевых производных | 1983 |

|

SU1168925A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для вычисления булевых производных | 1985 |

|

SU1277089A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1991-08-15—Публикация

1989-06-05—Подача