ми первого и второго элементов ИЛИ, инверсный выход второго разряда регистра сдвига соединен с первым входом восьмого элемента И и вторыми входами третьего и шестого элементов И, прямой выход третьего разряда сдвигового регистра соединен с вторыми,входами второго и восьмого элементов И и третьим входом второго элемента ИЛИ, инверсный въкор, третьего разряда соединен с вторыми входами девятого и седьмого элементов И и с информационным входом регистра сдвига, тактирующий вход которого соединен с входом элемента НЕ и выходом третьего элемента ИЛИ, подключенного первым входом к выходу девятого элемента И, второй вход третьего элемента ИШТ соединен с входами разрешения записи первого и второго реверсивных счетчиков и второго и третьего дополнительных регистров и с выходом первого одновибратора, вход которого соединен с выходом десятого элемента И, первый вход которого соединен с инверсным выходом триггера и выходом сигнала готовности преобразователя,второй вход десятого элемента И соединен с входом тактовых импульсов преобразователя и входом первого элемента задержки, выход которого соедичен с входом установки в единицу триггера, вход установки в ноль которого соединен через формирователь импульсов с выходом одиннадцатого элемента И, первый вход которого с выходом пятого элемента И и первым входом четвертого элемента ИЛИ, второй вход одиннадцатого элемента И соединен с первыми вxoдa ш элементов И с двенадцатого по четырнадцатый и через второй элемент задержки с управляющим входом сумматора и выходом пятого элемента ИЛИ, первый вход которого соединен с выходом пятнадцатого элемента И, первый вход которого соединен с прямым выходом второго одновибратора, второй вход пятнадцатого элемента И соединен с инверсным выходом третьего одновибратора, вход которого подключен к входу второго одновибратора tf выходу шестнадцатого элемента И, первьш вход которого соединен с выходом шестого элемента И, второй вход шестнадцатого элемента И соединен с выходом элемента НЕ, входом четвертого одновибратора и первым входом семнадцатого элемен11

6

та И, второй вход которого соединен с выходом первого элемента ИЛИ, выход семнадцатого элемента И соединен с входами одновибраторов с пятого по восьмой, второй вход пятого элемента ИЛИ соединен с выходом восемнадцатого элемента И, первый и второй входы которого соединены с прямым выходом пятого одновибрато- ра и инверсным выходом шестого одновибратора, прямой выход седьмого одновибратора соединен с первым входом девятнадцатого элемента И, второй вход которого соединен с инверсным выходом четвертого одновибратора и первьгм входом двадцатого элемента И, второй вход и выход которого соединены соответственно с выходом восьмого одновибратора и входом вьшитания реверсивных счетчиков, второй вход девятого элемента И подключен к выходу второго элемента ИЛИ, выход второго элемента И соединен с первым входом двадцать первого элемента И и первыми входами шестого и седьмого элементов ИЛИ, вторые входы которьпс соединены с выходом восьмого элемента И, выход шестого элемента ИЛИ соединен с вторым входом двенадцатого элемента И, третий вход седьмого элемента ИЛИ соединен с вькодом третьего элемента И и первым входом восьмого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, первым входом двадцать второго элемента И и вторым входом четвертого элемента ИЛИ, выход которого соединен с вторым входом четырнадцатого элемента И, третий вход восьмого элемента ИЛИ соединен с выходом седьмого элемента И и первьм входом двадцать третьего элемента И, второй вход которого соединен с прямым выходом четвертого одновибратора, вторыми входами двадцать первого и двадцать второго элементов И и первым входом двадцать четвертого элемента И, выход которого соединен с входом установки

в ноль третьего регистра, второй вход двадцать четвертого элемента И соединен с выходом седьмого элемента ИЛИ и вторым входом тринадцатого элемента И, выходы двадцать третьего и двадцать первого элементов И соединены с входами суммирования соответственно первого и второго реверсивных счетчиков, выхст двадцать второго элемента И соединен с управляющим .входом &лока памяти, выходы двадцатого, двенадцатого, тринадцатого и четырнадцатого элементов И соединены с управляющими входами соответственно с первого по третий регистров и первого дополнительного регистра, вы110713 . 6 ходы восьмого элемента ИПИ и первого, восьмого и пятото элементом И соединены с управляюиу1мч нходами второго коммутатора, выходы первого элемента ИЛИ и шестого элементл И соединены с управляющими входами первого коммутатора,

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для воспроизведения функций | 1984 |

|

SU1182539A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Функциональный преобразователь | 1984 |

|

SU1171774A1 |

| МНОГОМЕРНЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР УСРЕДНЕННОЙ МОЩНОСТИ НЕСТАЦИОНАРНОЙ НАГРУЗКИ | 1992 |

|

RU2060542C1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ СУБОПТИМАЛЬНОГО РАЗМЕЩЕНИЯ И ЕГО ОЦЕНКИ | 2001 |

|

RU2193796C2 |

| МНОГОКАНАЛЬНАЯ СИСТЕМА ДЛЯ РЕГИСТРАЦИИ ФИЗИЧЕСКИХ ВЕЛИЧИН | 1991 |

|

RU2037190C1 |

| Синусно-косинусный функциональный преобразователь | 1981 |

|

SU970357A1 |

| Устройство для сжатия информации | 1986 |

|

SU1324047A1 |

| Многомерный статистический анализатор сглаженной эффективной мощности нагрузки | 1991 |

|

SU1836692A3 |

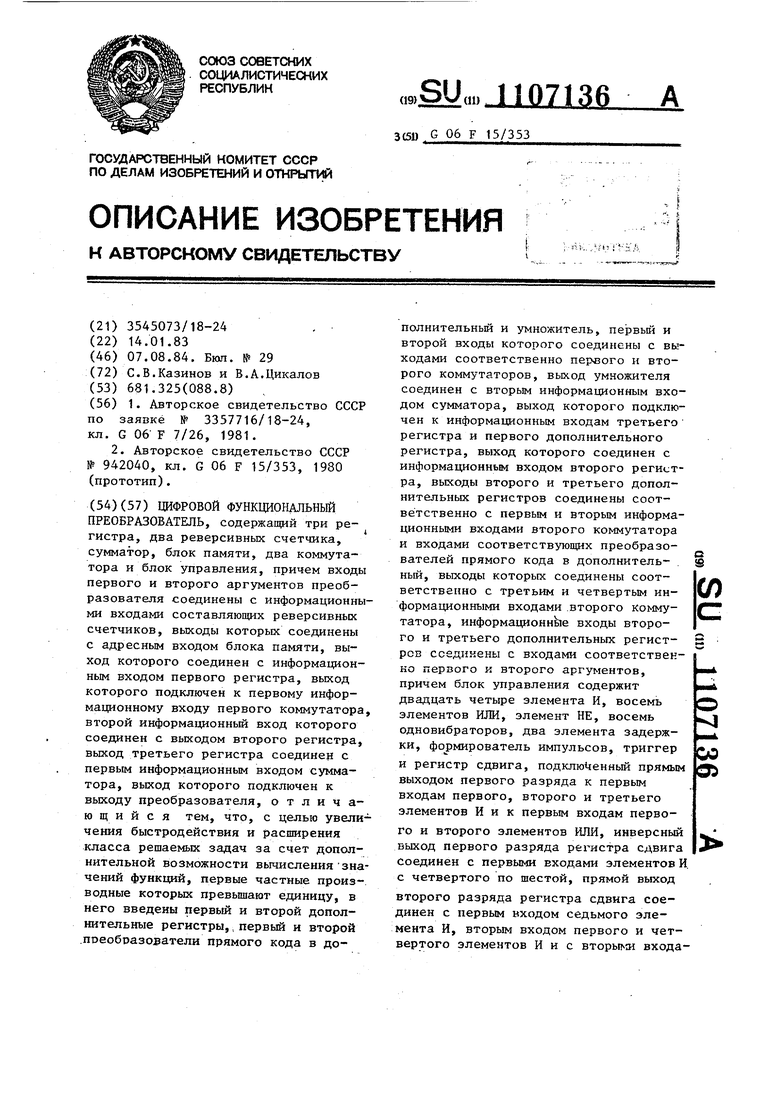

ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий три регистра, два реверсивных счетчика, сумматор, блок памяти, два коммутатора и блок управления, причем входы первого и второго аргументов преобразователя соединены с информационными входами составляющих реверсивных счетчиков, выходы которых соединены с адресным входом блока памяти, выход которого соединен с информационным входом первого регистра, выход которого подключен к первому информационному входу первого коммутатора, второй информационный вход которого соединен с выходом второго регистра, выход третьего регистра соединен с первым информационным входом сумматора, выход которого подключен к выходу преобразователя, отличающийся тем, что, с целью увеличения быстродействия и расширения класса решаемых задач за счет дополнительной возможности вычисления значений функций, первые частные производные которых превышают единицу, в него введены первый и второй дополнительные регистры,, первый и второй .преобразователи прямого кода в дополнительньш и умножитель, первый и второй входы которого соединены с выходами соответственно первого и второго коммутаторов, выход умножителя соединен с вторым информационным входом сумматора, выход которого подключен к информационным входам третьего регистра и первого дополнительного регистра, выход которого соединен с информационным входом второго регистра, выходы второго и третьего дополнительных регистров соединены соответственно с первым и вторым информационными входами второго коммутатора и входами соответствующих преобразоi вателей прямого кода в дополнитель- . ньй, выходы которых соединены соотСП ветственно с третьим и четвертым информационными входами .второго коммутатора, информационнее входы второго и третьего дополнительных регистров соединены с входами соответственно первого и второго аргументов, причем блок управления содержит двадцать четыре элемента И, восемь элементов ИЛИ, элемент НЕ, восемь одновибраторов, два элемента задержки, фо рмирователь импульсов, триггер 00 и регистр сдвига, подключенный прямым О) выходом первого разряда к первым входам первого, второго и третьего элементов Ник первым входам первого и второго элементов ИЛИ, инверсный выход первого разряда регистра сдвига соединен с первыми входами элементов И. с четвертого по шестой, прямой выход второго разряда регистра сдвига соединен с первым входом седьмого элемента И, вторым входом первого и четвертого элементов И и с вторьп м входа

1

Изобретение относится к автоматике и вычислительной технике.

. Известен функциональный преобразователь, содержа1ций группу входных преобразователей, блок памяти, блок управления, формирователь интерполирующих функций, регистры, умножители и сумматор CllНедостатками функционального преобразователя являются сложность технической реализации из-за использования большого количества умножителей и пониженная точность преобразования из-за использования при вычислениях промежуточного представления сигналов в аналоговой форме.

Наиболее близким по технической сущности к предлагаемому является цифровой функциональный преобразователь многих, переменных, содержащий коммутаторы,группу из п реверсивных счетчиков (где п - количество независимых переменных), подключенных установочными входами к шинам ввода соответствующих переменных, входами управления установкой кода - к первому выходу блока управления, суммирующими входами - к соответствующим выходам первой группы выходов блока управления, вычитающими входами к соответствующим вьо:одам второй группы выходов блока управления, а выходами - к адресным входам блока памяти, соединенного управляющим входом с вторым выходом блока управления, а выходом - с информационным входом первого регистра, подключенного выходом к первому информационному входу первого коммутатора, соединенного вторым информационным входом с выходом второго регистра, причем выход третьего регистра подключен к первому входу сумматора, выход которого является выходом цифрового функционального преобразователя многих переменных, а управляющие входы регистров соединены с соответствующими выходами третьей группы рыходов блока управления, подключенного третьим выходом к управляющему входу сумматора, соединенного вторым входом с выходом блока памяти и с информационным входом второго регистра, а выходом - с информационным входом блока памяти, причем выход переполнения каждого i-го () реверсивного счетчика подключен к счетному

5 входу (-ъ-И)-го реверсивного счетчика, а выход л-го реверсивного счетчика соединен с управляющими входами первого коммутатора и второго коммутатора, подключенного информационными

0 входами и выходами первого и второго регистров, а выходы коммутаторов соединены с входа комбинационного суммирования, подключенного выходом к информационному входу третьего

5 регистра С2.

Недостатками известного устройства являются ограниченность класса воспроизводных функций из-за невозможности воспроизведения функций,

0 первые частные производные которых превышают единицу, и пониженное iбыстродействие из-за формирований функции внутри каждой подобласти аппроксимации путем последовательного

5 построчного интегрирования yзJIoвыx значений первых производных.

Цель изобретения - увеличение быстродействия и расширение класса решаемых задач за счет дополнительной

0 возможности вычисления значений функций, первые частные производные которых превышают единицу.

Поставленная цель достигается тем, что в цифровой функциональный 31 преобразователь, содержащий три регистра, два реверсивных счетчика, сумматор, блок памяти, два коммутато ра и блок управления, причем входы первого и второго аргументов преобразователя соединены с информационны ми входами соответствукяцих реверсивных счетчиков, выходы которых соединены с адресным входом блока памяти, выход которого соединен с информационным входом первого регистра, выход которого подключен к первому информационному входу первого коммутатора второй, информационный вход которого соединен с выходом второго регистра, выход третьего регистра соединен с первым информационным входом сумматора, выход которого подключен к выходу преобразователя, дополнительно введены первый и второй дополнительные регистры, первый и второй преобразователи прямого кода в дополнительный и умножитель, первый и второ входы которого соединены с выходами соответственно первого и второго коммутаторов, выход умножителя соеди нен с вторым информационным входом сумматора, выход которого подключен . к информационным входам третьего регистра и первого дополнительного регистра, выход которого соединен с информационным входом второго 1регистра, выходы второго и третьего дополнительньк регистров соединены соответственно с первым и вторым информационными входами второго коммутатора и входами соответствующих преобразователей прямого кода в дополнительный выходы которЬЕС соединены соответствен но с третьим и четвертым информационными входами второго коммутатора, информационные входы второго и третьего дополнительных регистров соединены с входами соответственно первого и второго аргументов, причем блок управле- 45 тый

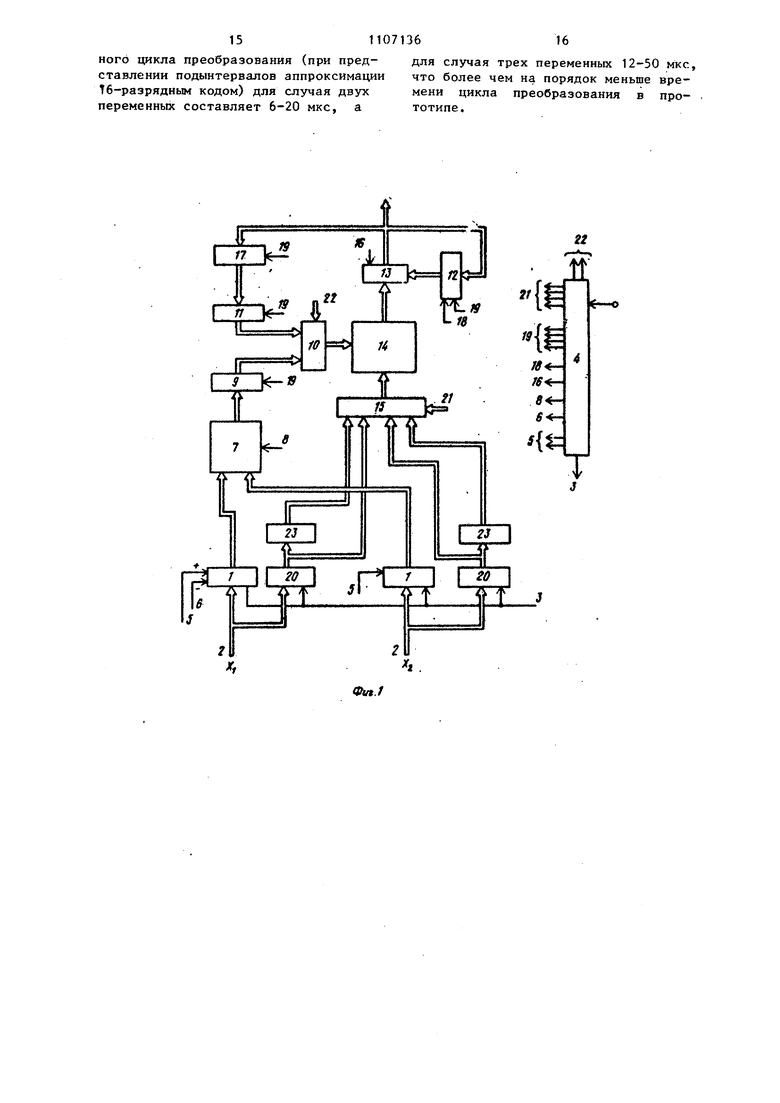

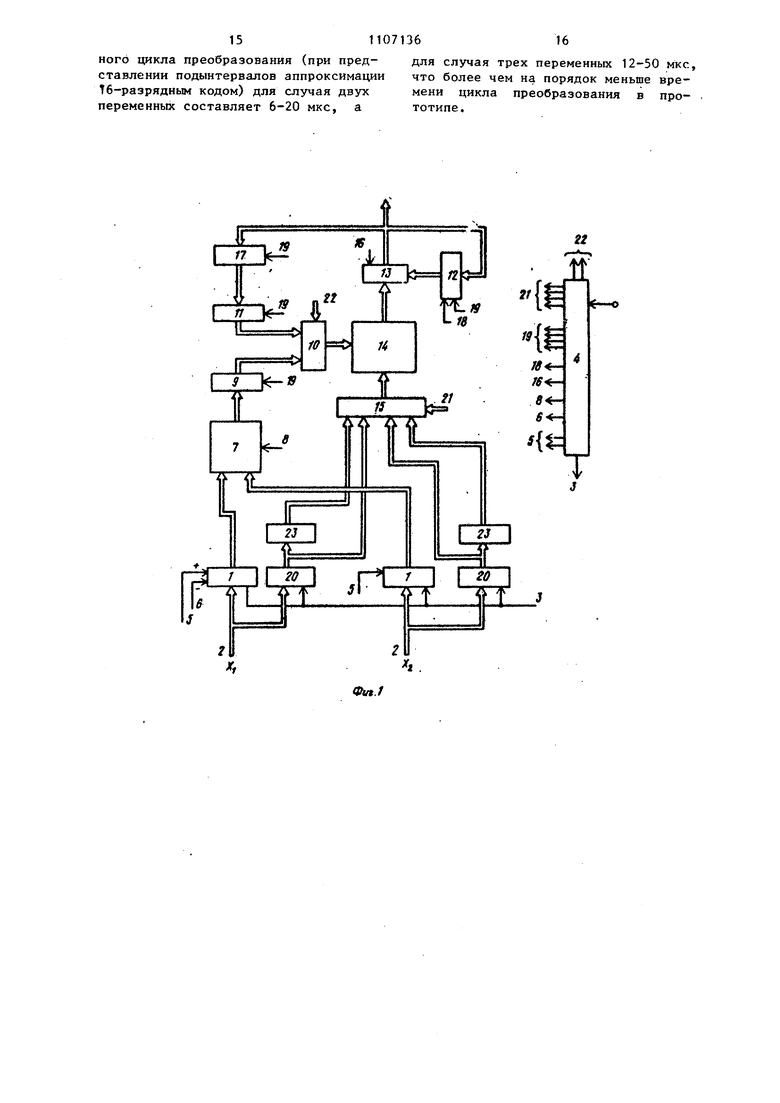

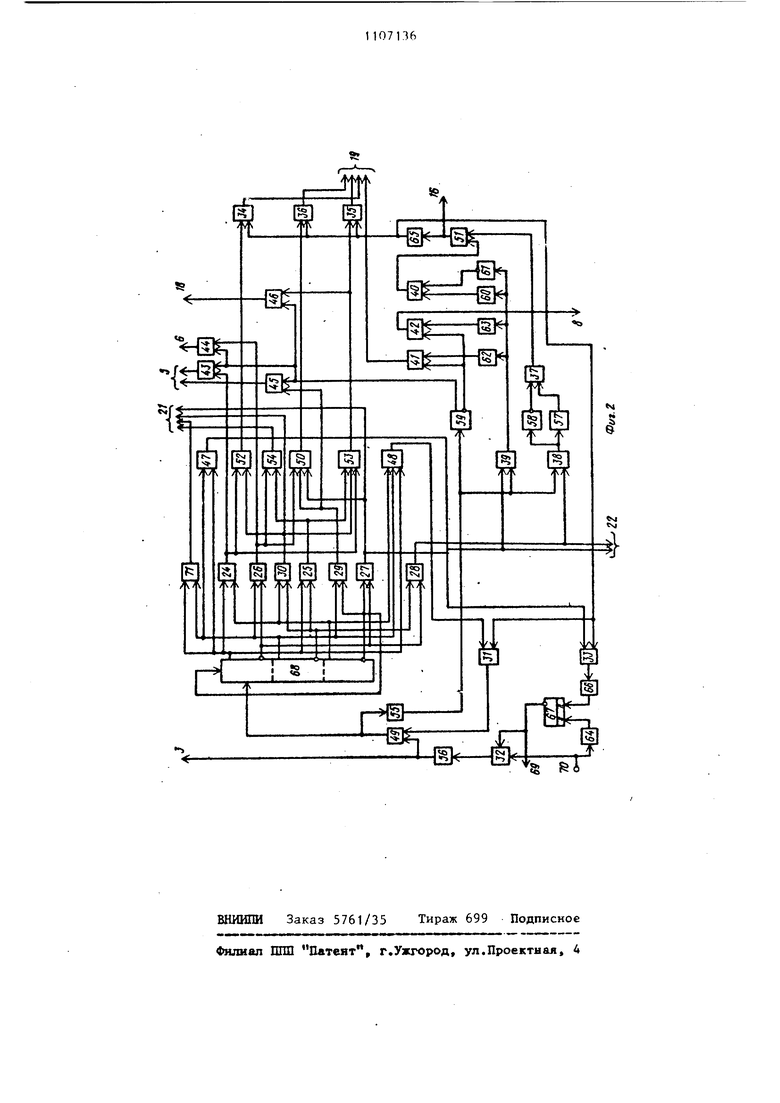

ния содержит двадцать четыре элемента И, восемь элементов ИЛИ, элемент НЕ, восемь одновибраторов, два элемента задержки, формирователь импуль сов, триггер и регистр сдвига, подключенньй прямым выходом первого разряда к первымвходам первого, второго и третьего элементов И и к первым входам первого и второго элементов ИЛИ инверсный вьгход первого разряда регистра сдвига соединен с первыми входами элементов И с четвертого по шестой, прямой выход второго разряда реуправляющим входом сумматора и выходом пятого элемента ИЛИ, первый вход которого соединен с выходом пятнадцатого элемента И, первый вход которого соединен с прямым выходом второго одновибратора, второй вход пятнадцатого элемента И соединен с инверсным выходом третьего одновибратора, вход которого подключен к входу второго одновибратора и выходу шестнадцатого элемента И, первьм вход которого соединен с выходом шестого элемента И, второй вход шестнадцатого эле6гистра сдвига соединен с первым входом седьмого элемента И, вторым входом первого и четвертого элементов И и с вторыми входами первого и второго элементов ИЛИ, инверсный выход второго разряда регистра сдвига соединен с первым входом восьмого элемента И и вторыми входами третьего и шестого элементов И, прямой выход третьего разряда сдвигового регистра соединен с вторыми входами второго и-восьмого элементов И и третьим входом второго элемента ИЛИ, инверсньй выход третьего разряда соед1 нен с вторыми входами девятого и седьмого элементов И и с информационнь1м входом регистра сдвига, тактирующий вход которого соединен с входом элемента НЕ и выходом третьего элемента ИЛИ, подключенного первым входом к выходу девятого элемента И, второй вход третьего элемента ИЛИ соединен с входами разрешения записи первого и второго реверсивных счетчиков и второго и третьего дополнительных регистров и с выходом первого одновибратора, вход которого соединен с выходом десятого элемента И, первый вход которого соединен с инверсным выходом триггера и выходом сигнала готовности преобразователя, второй вход десятого элемента И соединен с входом тактовых импульсов преобразователя и входом первого элемен- - та задержки,- выход которого соединен с входом установки в единицу триггера, вход установки в ноль которого соединен через формирователь импульсов с выходом одиннадцатого элемента И, первый вход которого соединен с выходом пятого элемента И и первым входом четвертого элемента ИЛИ, второй вход одиннадцатого элемента И оединен с первьп 1и входами элеменов И с двенадцатого по четырнадцаи через второй элемент задержки с S11 мента И соединен с выходом элемента НЕ,, входом четвертого одновибратора и первым входом семнадцатого элемента И, второй вход которого соединен с выходом первого элемента ИЛИ, выход, семнадцатого элемента Н соединен с входами одновибраторов с пятого по восьмой, второй вход пятого элемента ШТИ соединен с выходом восемнадцатого элемента И, первьм и второй входы которого соединены с прямым выходом пятого одновибратора и инверсным выходом шестого одновибратора, прямой выход седьмого одновибратора соединен с первым входом девятнадцатого элемента И, второй вход которого соединен с инверсным выходом четвертого одновибратора и первым входом двадцатого элемента И, второй вход и выход которого соединен соответственно с выходом восьмого одновибратора и входом вычитания реверсивных счетчиков, второй вход девятого элемента И подключен к выхо ду второго элемента ИЛИ, выход второго элемента И соединен с первым входом двадцать первого элемента И и первыми входами шестого и седьмого элементов ИЛИ, вторые входы которых соединены с выходом восьмого элемента И, выход шестого элемента ИЛИ соединен с вторым входом двенадцатого элемента И, третий вход седьмого элемента ИЛИ соединен с выходом третьего элемента И и первым входом восьмого элемента РШИ, второй вход которого соединен с выходом четверто го элемента И, первым входом двадцат второго элемента И и вторым входом четвертого элемента ИЛИ, выход кото рого соединен с вторым входом четырнадцатого элемента И, третий вход восьмого элемента ИЛИ соединен с выходом седьмого элемента И и первым входом двадцать третьего элемента И второй вход которого соединен с прямым выходом четвертого одновибратора вторыми входами двадцать первого и двадцать второго элементов И и первы входом двадцать четвертого элемента И выход которого соединен с входом установки в ноль третьего регистра, второй вход двадцать четвертого элемента И соединен с выходом седьмого элемента ИЛИ и вторым входом тринадцатого элемента И, вьпходы двадцать третьего и двадцать первого элементов И соединены с входами суммироваНИН соответственно первого и второго реверсивных счетчиков, выход двадцать второго элемента И соединен с управляющим входом блока памяти, выходы двадцатого, двенадцатого, тринадцатого и четырнадцатого элементов И соединены с управляющими входами соответственно с первого по третий регистров и первого дополнительногорегистра, вьсходы восьмого элемента ИЛИ и первого, восьмого и пятого элементов И соединены с управляюшими входами втог рого коммутатора, выходы первого элемента ИЛИ и шестого элемента И соединены с управляющими входами первого коммутатора. На фиг.1 приведена блок-схема преобраэователя; на фиг.2 - конструкция блока управления. Цифровой функщ1ональный преобразовате,пь содержит реверсивные счетчики 1, входы 2 аргументов, входы 3 разрешения записи счетчиков 1, блок 4 управления, входы 5 и 6 соответственно cyм иpoвaния и вычитания счетчиков 1, блок 7 памяти, вход 8 управления блоком 7 памяти, регистр 9, коммутатор 10, регистры 11 и 12, сумматор 13, умножитель 14, коммутатор 15, управляюи ий вход 16, дополнительный регистр 17, вход 18 обнуления и управляющий вход 19, дополнительные регистры 20, управляющие входы 21 и 22 коммутаторов 15 и 10, преобразователи 23 прямого кода в дополнительБлок управления Содержит элементы И 2А-46, элементы ИЛИ 47-54, элемент НЕ 55, одновибраторы 56-63, элементы 64 и 65 задержки, формирователь 66 импульсов, триггер 67, регистр 68 сдвига, выход 69 сигнала готовности, тактовый вход 70 и элемент И 7 1 . Цифровой функциональный преобразователь может производить вьиисления значений функций двух переменных, но, учитывая сущность построения структуры преобразования для двух и более переменных, рассмотрим работу преобразования для общего случая. Цифровой функциональньп преобразователь работает следующим образом. Исходная функция f(v ...} аппроксимируется п -мерным полиноминальным сплайном первого порядка, нормированные значения ординат которого в узлах подобластей аппроксимации перед 711 началом работы записываются в блок 7 памяти. Каждый цикл работы преобразователя состоит из такто и начинается со считывания по шинам 2 (фиг,1) кодов переменньгх в реверсивные счтечики 1 и регистры 20, При этом старшие разряды кодов переменньгх, определяющие узлы подобластей аппроксимации, считываются в реверсивные счетчики 1, а младшие разряды кодов переменных, определяющие приращения переменных внутри подобластей аппроксимации, считываются в регистры 20. Выполняется первая группа из 2 тактов, в каждом из которых из блока 7 памяти в регистр 9 считывается ордината одного из узлов подобласти аппроксимации, умножается в умножителе 14 на значение приращения первой переменной в прямом 20 или дополнительном коде, выбираемое с помощью коммутатора 15, Результат перемножения суммируется в сумматоре 13 с содержимым регистра 12 и записывается в один из регистров 11,12 или 17. При этом переход от одного к другому узлам аппроксимации для выборки из блока 7 памяти ординат этих узлов осуществляется в каждом такте путем добавления или вычитания единицы младшего разряда в одном из реверсивных счетчиков 1. По окончании первой группы тактов выполняются последуюи т.д. такщие группы из тов, в каждой из которых значения приращений в прямом или дополнительном коде одной из остальных переменньгх умножаются на результаты вычислений по предыдущей группе тактов. По окончании последней группы из двух тактов, в которых два результата вычислений по предпоследней группе тактов умножаются на значение приращения последней переменной в прямом и дополнительном коде и суммируются полученные произведения, результат суммирования, являющийся вычисленным значением функции Су,Х2.,...; Хи) , считывается на выход функционального преобразователя. Далее описанный цикл функционального преобразования повторяется для новых значений переменных Рассмотрим подробнее-работу устройства для случая выполнения функционального преобразования по двум переменным ((и,Х2)В исходном состоянии обнулены, сумматор 13, а также триггер 67 и регистр 68 сдвига блока 4 управления (цепи приведения в исходное состояние не показаны) . С приходом на гшшу 70 (фиг.2) Импульса запуска синхронизирующей частоты и началом первого такта работы этот импульс проходит через открытый элемент И 32 на вход одновибратора 56 и одновременно с зтим поступает на вход элемента 64 задержки. Одновибратор 56 по положительному фронту входного сигнала формирует импульс, поступающий через выход 3 блока 4 управления на входы управления установкой кода реверсивных счетчиков 1 и регистров 20. Старшие и младшие разряды входных переменных х и х считываются в счетчики 1 и регистры 20 соответственно. По истечении времени задержки импульс с выхода элемента 64 задержки устанавливает триггер 67 в единичное состояние, запирающее элемент И 32 и препятствующее повторному запуску устройства до окончания цикла функционального преобразования. Выходной импульс одновибратора 56 через элемент ИЛИ 49 поступает на вход элемента НЕ 55 и на тактирующий вход регистра 68 сдвига. По заднему фронту этого импульса, соответствующему окончанию записи информации в счетчики 1 и регистры 20, в регистре 68 (выполненном по схеме о перекрестной связью на триггерах Ъ, -типа) формируется единичный сигнал на прямом выходе первого разряда, отпирающий элемент И 25 и элементы ИЛИ 47, 48, 53 и 54. Сигнал с выхода элемента ИЛИ 47 поступает на управляющий вход коммутатора 10, подключая выход регистра 9 к входу умножителя 14. Сигнал с выхода элемента ИЛИ 54 поступает на управляющий вход коммутатора 15, подключая выход дополнительного кода первого из регистров 2 к второму входу умножителя 14. Задний фронт импульса одновибратора 56, инвертированный элементом НЕ 55, запускает Одновибратор 59 и через элемент И 39, открытый сигналом с вькода элемента ИЛИ 47, запускает одно- . вибраторы . Импульс с прямого вькода одновибратора 59 через эле„ент И 46, открытый сигналом с выхода элемента ИЛИ 53, и выход 18 блока управления поступает на вход обнуления регистра 12, а импульс с инверсного выхода одновибратора 59 блокирдгет прохождение импульсов с БЫХОДОЕ одновибраторов 62 и 63 на время обнуления регистра 12. По окончании обнуления регистра 12 импульсы с выходов одновибраторов 62 и 63 поступают на управляющие входы регистра 9 и блока 7 памяти соответственно, Сигналом Выборка кристалла с вькода элемента И 42 блок 7 памяти, на шину выбора режима Чтениетзапись коттэ- рого подан потенциал Чтение (не показано), осуществляет выборку данных по адресу, соответствующему значениям выходных кодов счетчиков 1. Сигналом с выхода элемента И 41 осуществляется запись этих данных в регистр 9. Поскольку в блоке 7 памяти записаны нормированные значения С ординат аппроксимирующего сплайна 3(х-(,У2.) для узловых точек (х|,х|) подобластей аппроксимации

р..

UT-I-;

()

где () и (x x|) - шаг разбиения области аппроксимации по первой и второй переменным соответственно, tYi vyi2 число шагов разбиения по соответствующей переменной, а коды старших разрядов переменных х и Xj, считанные в реверсивные счетчики 1, определяют адрес первого (начального) узла текущей подобласти аппроксимации, например, с координатами (х, х), то в регистр 9 будет считано значение ординаты для этого первого узла. Умножитель 14 выполняет умножение ординаты С , поступающей на его вход с выхода регистра 9, на значение дополнительного кода приращения первой переменной внутри данной подобласти аппроксимации, т.е. на код (xij х) с выхода первого из регистров 20. Сформированное произведение суммируется с нулевым кодом регистра 12 и фиксируется на выходе сумматора 13. Для этого на управляюпщй вход сумматора 13 с выхода элемента ИЛИ 51 подается импульс, сформированный С помощью одновибраторов 60 и 61 и элемента И 40. Передний фронт этого импульса появляется на выходе элемента ИЛИ 51 после установления кода произведения на выходе умножителя 14. и его суммирования в сумматоре 13 с кодом регистра 12, а длительность импульса определяется временем фик-.

сации (записи) кода суммы на выходе сумматора 13. После фиксации результата на выходе сумматора 13 импульс с выхода элемента 65 задержки проходит через элемент И 35, открытый сигналом с выхода элемента ИЛИ 53, на управляющий вх(ед регистра 12. В регистр 12 переписывается значение выходного сумматора 13 равное

N.-Ci(xV-XO

Второй такт работы начинается с поступления зад;него фронта импульса

с выхода элемента 63 задержки через элемент И 31, открытый, сигналом с выхода элемента ИЛИ 48, и элемент ИЛИ 49 на тактирующий вход регистра 68 и вход элемента НЕ 55. По заднему

фронту импульса единица записывается во второй разряд регистра 68, а состояние остальных разрядов регистра не изменяется. При этом запираются элементы И 25 и элементы ИЛИ 53 и 54,

отпираются элементы И 71 и 29 и элемент ИЛИ 50, а элементы ИЛИ 47 и 48 остаются в открытом состоянии. Сигнал с выхода элемента И 71 поступает на управляющий вход коммутатора 15, подключая к входу умножителя 14 прямой выход первого из регистров 20. Другой вход умножителя 14 остается подключенным через коммутатор 10 к выходу регистра 9. Задний фронт импульса с

вькода элемента 65 задержки, инвертированный элементом НЕ 55, запускает одновибратор 59 и, Лроходя через элемент И 39, запускает одновибраторы 60-63. Импульс с прямого выхода одновибратора 59 через элемент И 45, открытый сигналом с выхода элемента И 29, поступает на суммирующий вход первого из реверсивных счетчиков 1, добавляя к его содержимому единицу младшего разряда. Поскольку состояние второго реверсивного счетчика 1 не изменяется, то код на адресных входах блока 7 памяти станет соответствовать адресу второго узла текущей подобласти аппроксимации. Аналогично

описанному по окончании установления кода в первом реверсивном счетчике 1 импульсы с выходов одновибраторон 62 и 63 поступят на управляю цие входы блока 7 памяти и регистра 9. В результате код ординаты ,j второго узла аппроксимации будет считан из блока 7 памяти в регистр 9 и через коммутатор 10 поступит на вход

умножителя 14, на другой вход которого через коммутатор 15 подается с первого из регистров 20 прямое значение кода приращения первой переменной внутри подобласти аппроксимации

Произведение этих кодов с выхода умножителя 14 суммируется в сумматор 13 с содержанием регистра 12. После фиксации окончательного результата код на выход-е сумматора 13 равный

M7--Civi,j( .

считывается в регистр 17 импульсом, поступающим на управляющий вход регистра 17 с выхода элемента 65 задержки через элемент ИЛИ 51 и элемент И 36, открытый сигналом с выхода элемента liJM 50.

Третий такт работы начинается с поступления заднего фронта импульса с выхода элемента 65 задержки через элементы И 31 и ИЛИ 49 на тактирующий вход регистра 68 и вход элемента НЕ 55. По этому фронту единица записывается в третий разряд регистра 68, состояние остальных разрядов которого не изменяется. Выходными сигналами регистра 68 запираются элементы И 29 и ИЛИ 50, отпираются элементы И 24 и ИЛИ 52 и 53, а элементы И 71 и ИЛИ 47 и 48 остаются в открытом состоянии. При этом Акод регистра 9 через коммутатор 10 подключен к первому входу умножителя 14, второй вход которого через коммутатор 15 соединен с прямым выходом первого из регистров 20. Положительным перепадом напряжения с выхода элемента НЕ запускаются одновибраторы 59-63. Импульс с прямого выхода одновибратора. 59 через элемент И 46, открытый сигналом с выхода элемента ИЛИ 53, обнуляет регистр 12 и через элемент И 43, открытый сигналом с выхода элемента И 24,добавляет еди ницу младшего разряда во второй из реверсивных счетчиков 1 (в котором было записано значение кода адреса хЗ по второй переменной х). В результате это счетчик 1 переходит в состояние, при котором на его выходе формируется код х| , а на адресных входах блока 7 памяти устанавливаются коды адреса (х ) третьего узла текущей подробности аппроксимации. После установления кода в счетчике 1 и обнуления регистра 12 импульсы с выходов одновибраторов 62 и 63 поступают на управляющие входы блока 7

памяти и регистра 9, осуществляя считывание кода -ординаты C-i.+H , in третьего узла аппроксимации из блока 7 памяти в регистр 9. Умножитель 14 перемножает код регистра 9 на прямой код первого из регистров, 11, а на выходе сумматора 13 формируется и фиксируется код j () По окончании фиксации кода на выходе сумматора 13 импульсов с выхода элемента 65 задержки, поступающего через элемент И 35 на управляющий вход регистра 12, осуществляется считывание кода I4j в-регистр 12. Одновременно импульсом с вьосода элемента 65 задержки через элемент И 34, открытый сигналом с выхода элемента ИЛИ 52, осуществляется перепись кода N2 из регистра 17 в регистр 11.

Б четвертом такте работы по заднему фронту импульса с выхода элемента 65 обнуляется первый разряд регистра 68 сдвига и запускаются одновибраторы 59-63. Запираются элементы И 71, 24 и ИЛИ 52, 53, отпираются элементы И 26 и ИЛИ 50, 54, а элементы ИЛИ 47 и 48 остаются в открытом состоянии. Второй вход умножителя 14 через коммутатор 15 подключается к выходу дополнительного кода первого из регистров 20. Импульсом с прямого выхода одновибратора 59 через элемент И 44, открытый выходным сигналом элемента И 26, из содержимого первого из реверсивных счетчиков 1 вычитается единица мпадшего разряда и на выходе этого счетчика устанавливается код х . По окончании устан овления кода в счетчике импульсами с выходов одновибраторов 62 и 63 производится считывание из блока 7 памяти в регистр 9 кода ординаты С чет-. вертого узла (х, х| ) текущей подобласти аппроксимации. Умножитель 14 умножает значение этого кода на значение приращения первой переменной в дополнительном коде, а на выходе сумматора 13 формируется и фиксируется код

,J44(r.XiVNs

После фиксации в сумматоре 13 кода результата импульсом с выхода элемента 65 задержки, исходящим через элемент И 36 на управляющий вход регистра 17, содержимое сумматора 13 переписывается в регистр 17.

По заднему фронту импульса с выхода элемента 65 задержки заканчивается первая группа из тактов и начинается вторая группа из 2 тактов (пятого и шестого). В пятом такте работызадним фронтом импульса с выхода элемента 65 задержки обнуляется второй разряд, регистра 68 сдвига и зaпyckaeтcя одновибратор 59. Запираются элементы И 26 и ИЛИ 47, 50, 54, отпираются элементы И 28, 30 и ИЛИ 52, 53, а элемент ИЛИ 48 остается в открытом состоянии. Сигналом с выхода элемента И 28 переключается комму татор 10, соединяя выход регистра 11 с первым входом умножителя 14, а сиг налом с выхода элемента И 30 переклю чается коммутатор 15, соединяя выход дополнительного кода второго из регистров 20 с вторьм входом умножител 14. Выходной сигнал элемента НЕ 55 через элемент И 38, открытый сигналом с выхода элемента И 28, запускае одновибраторы 57 и 58. Импульсы с прямого выхода одновибратора 59 чере элемент И 46 обнуляют регистр 12. Умножитель 14 перемножает код Mr с выхода регистра 11 на значение прира щения второй переменной в дополнительном коде с выхода второго из регистров 20. После установления кода произведения на вькоде умножителя 14 и кода суммы па выходе сумматора ТЗ г импульсом с выхода элемента И 37, поступающим через элемент ИЛИ 51 на .управляющий вход сумматора 13, фиксируется выходной код Ng сумматора 13 Kl5-HiCxt-X2 После фиксации выходного кода сумматора 13 импульсом с выхода элемента 65 задержки, проходящим через элемент И 35 на регистр 12, код сумматора 13 считывается в регистр 12. Одновременно выходным импульсом элемента 65 задержки, проходящим через элемент И 34 на регистр 11, содержимое регистра 17 переписывается в регистр 11. В шестом такте работы задним фрон том импульса с выхода элемента 65 за держки обйуляется третий разряд регистра сдвига и запускаются одновибраторы 57-59. Запираются элементы И 30 и ИЛИ 48, 52, 53, отпираются элементы И 27 к ИЛИ 50, а элемент И 28 остается в открытом состоянии. Сигналом с выхода элемента И 27 переклю чается коммутатор 15, соединяя прямо выход второго на регистров 20 с вторым входом умножителя 14. Первый вход умножителя 14 остается подключенным через коммутатор 10 к выходу регистра 11. Умножитель 14 перемножает код MS с выхода регистра 11 на значение прямого кода приращения второй переменной. После установления кода произведения и его суммирования в сумматоре 13 с кодом регистра 12 на-выходе элемента ИЛИ 51 формируется импульс, фиксирующий выходной код сумматора 13, равный Нв М5СХ1-Х2)-1Ц5Ог С | -УлХУ - 2 Ct.,j(x,( «-Ч..ЗН.СУ.-K-jXx -) S(Xx,Xi), т.е. код, равный результатам функционального преобразования по двум переменным. Импульс с выхода элемента 65 задержки через элемент И 33, открытый сигналом с выхода элемента И 27, поступает на вход формирователя 66, дифференцирукяцего этот импульс по переднему фронту. Выходной сигнал формирователя 66 обнуляет триггер 67, сигнал с выхода которого разблокирует элементаИ 32, и поступает на выходную шину 69, свидетельствуя о завершении цикла преобразования и готовности начала нового цикла. Новый цикл преобразования начинается по сигналу импульса внешней синхронизации и выполняется аналогично описанному (для работы в режиме внутренней синхронизации шину 69 нудно подключить к шине 7.0) . Таким образом, предлагаемый цифровой функциональный преобразователь по срав.нению с прототипом позволяет осуществлять преобразование для более широкого класса функций, включающего функции, первые частные производные которых превьш1ают единицу (что определяется соотношением разрядности слов блока 7 памяти и длин подынтервалов аппроксимации), а также обладает более высоким быстродействием,осуществляя полньш цикл преобразования за фиксированное число тактов, не за- висящее от длин подынтервалов аппроксимации. При реализации рассмотренного преобразователя на современной элементной базе (включая перспективные варианты быстродействующих двоичных умножителей на ТТЛ схемах) время полного цикла преобразования (при представлении подынтервалов аппроксимации Тб-разрядным кодом) для случая двух переменных составляет 6-20 мкс, а

nCIOLlgj ,n7j сю ITTLJT 1ГГ иЗ- для случая трех переменных 12-50 мкс, что более чем на порядок меньше времени цикла преобразования в прототипе.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР по заявке № 3357716/18-24, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Интерполятор поверхности | 1980 |

|

SU942040A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-08-07—Публикация

1983-01-14—Подача