Ин(р. выход -

Woe

| название | год | авторы | номер документа |

|---|---|---|---|

| МНОГОЧАСТОТНЫЙ ПРИЕМНИК ДЕЛЬТА-МОДУЛИРОВАННЫХ СИГНАЛОВ | 1993 |

|

RU2090981C1 |

| Цифровой обнаружитель гармонических составляющих дельта-модулированных сигналов | 1989 |

|

SU1626461A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2004 |

|

RU2260195C1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ДЫХАНИЯ ПАЦИЕНТА | 1999 |

|

RU2161475C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ СИГНАЛОВ С ПРОГРАММНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 1997 |

|

RU2110890C1 |

| Устройство синхронизации в одночастотных многоканальных адресных системах с временным разделением каналов | 1989 |

|

SU1811018A1 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

| Многочастотный приемник сигналов адаптивной дельта-модуляции | 1989 |

|

SU1626442A1 |

| Преобразователь сигналов с адаптивной дельта-модуляцией со слоговым компандированием в сигналы с нелинейной импульсно-кодовой модуляцией | 1990 |

|

SU1762411A1 |

| УСТРОЙСТВО ДЛЯ СИНХРОНИЗАЦИИ ПО ЦИКЛАМ | 2002 |

|

RU2239953C2 |

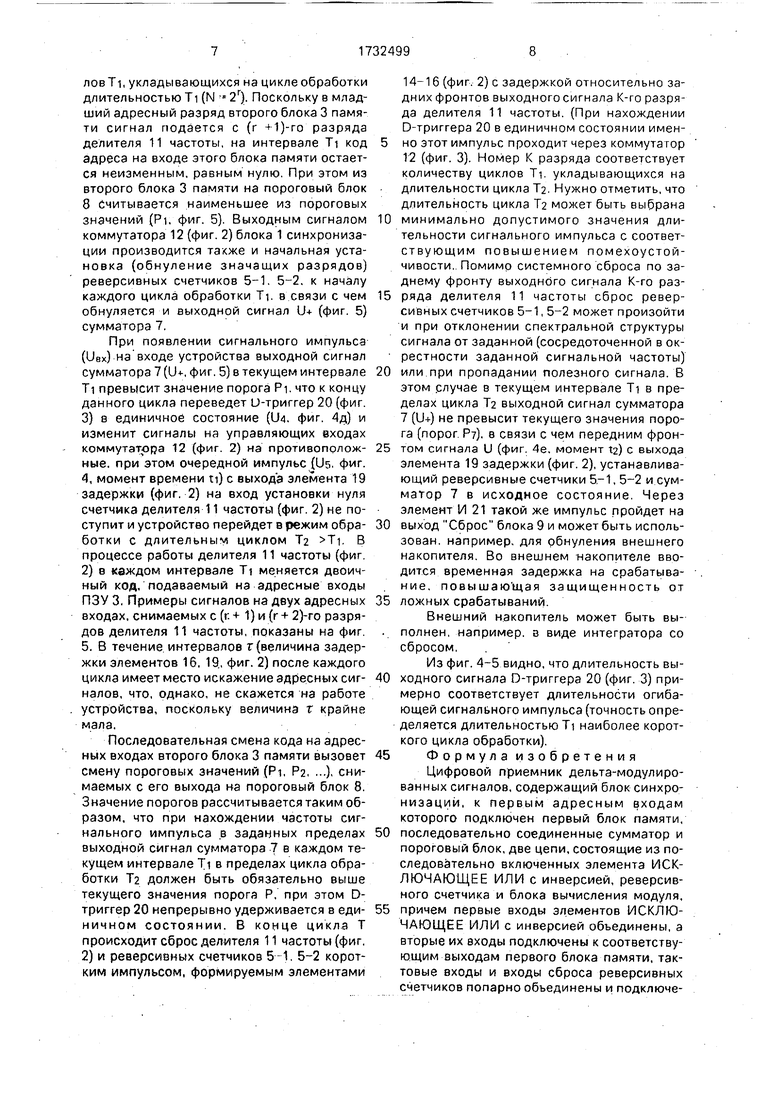

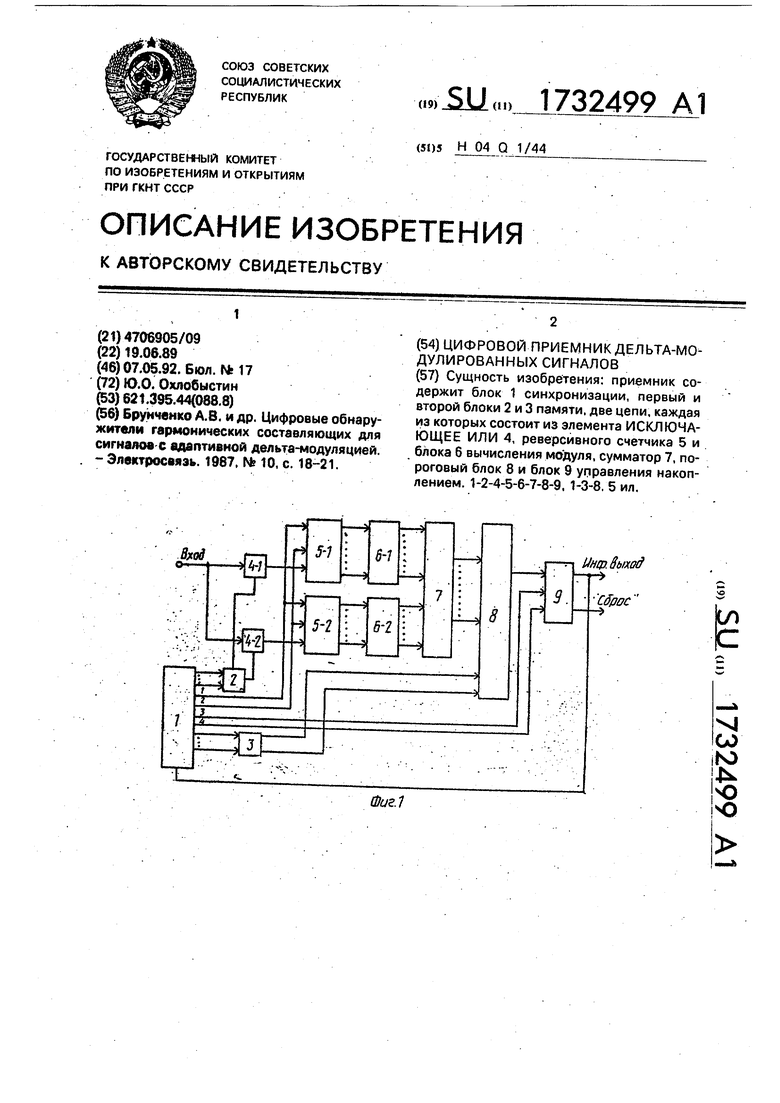

Сущность изобретения: приемник содержит блок 1 синхронизации, первый и второй блоки 2 и 3 памяти, две цепи, каждая из которых состоит из элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 4, реверсивного счетчика 5 и блока 6 вычисления модуля, сумматор 7, пороговый блок 8 и блок 9 управления накоплением. 1-2-4-5-6-7-8-9. 1-3-8. 5 ил.

Фиг.1

VJ GJ |Ю

1 Ч

о

Изобретение относится к технике цифровой обработки сигналов и может быть использовано в электросвязи для приема одиночных сигналов, в частности, для приема линейных сигналов 2600 Гц, используе- мых на телефонных сетях, представленных в форме сигналов дельта-модуляции с инерционным компандированием.

Известен цифровой приемник одноча- стотных сигналов в виде дельта-модулиро- ванных сигналов, который может быть реализован в виде линии задержки, отводы которой через умножители соединены с входом сумматора.

Недостатком известного устройств яв- ляется его сложность, связанная с большим количеством умножителей Кроме того, повышение избирательности по частоте путем увеличения длительности анализа приводит к искажениям длительности сигнала на вы- ходе устройства.

Известен цифровой приемник дельта- модулированных сигналов, содержащий блок синхронизации,блок памяти,первый и второй элементы ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, первый и второй реверсивные счетчики, первый и второй блоки вычисления модуля, сумматор и пороговое устройство.

В указанном устройстве решение о на- личин или отсутствии сигнальной частоты в обрабатываемом сигнале формируется в конце каждого цикла обработки, имеющего некоторую заданную длительность Т.

В одночастотные приемники линейных сигналов с целью повышения защищенности отложных срабатываний от речевых сигналов вводится временная задержка на срабатывание. Если Тмин - минимально допустимая длительность сигнального им- пульса, то очевидно, что для повышения помехозащищенности время задержки на срабатывание целесообразно принять близким к величине Тмин, чтобы при этом не пропустить сигнальный импульс, искаже- ния длительности сигнала на выходе приемника должны быть достаточно малы. Повышение помехозащищенности достигается увеличением избирательности фильтрации в устройстве, что требует увеличения длительности Т одного цикла обработки, но из-за некоррелированности границ начала и конца цикла с моментами прихода сигнального импульса увеличение длительности Т приводит к повышению искажений длительности сигнала на выходе устройства и снижению помехозащищенности,

Однако увеличение Т повышает помехозащищенность за счет повышения избирательности полосовой фильтрации, кроме

того, ведет к увеличению искажений длительности и уменьшению допустимой величины задержки на срабатывание и снижение помехозащищенности.

Целью изобретения является повышение помехозащищенности и уменьшение искажений длительности путем обеспечения возможности функционирования устройства при больших длительностях цикла обработки, но с сохранением малых искажений длительности сигнала.

Цель изобретения достигается введением зависимости длительности одного цикла обработки от того, находится ли устройство в сработавшем (прием) или несработавшем состоянии. При этом в отсутствие сигнального импульса на входе устройства время Ti цикла обработки мало (поиск сигнала) и обнаружение начала сигнального импульса происходит с минимальной задержкой. После срабатывания устройство переходит в режим, при котором длительность цикла увеличивается до величины Т2 TL но решение о наличии или отсутствии сигнальной информации благодаря наличию системы из нескольких порогов принимается в каждом интервале Ti, поэтому отклонение частоты сигнала от заданной величины или момент пропадания сигнала распознается также достаточно быстро (примерно в течение текущего интервала TI). В результате описанных процессов избирательность по частоте определяется величиной Т2, которая может достигать минимально допустимой длительности всего сигнального импульса, а искажения длительности всего сигнального импульса определяются сравнительно небольшой величиной TL

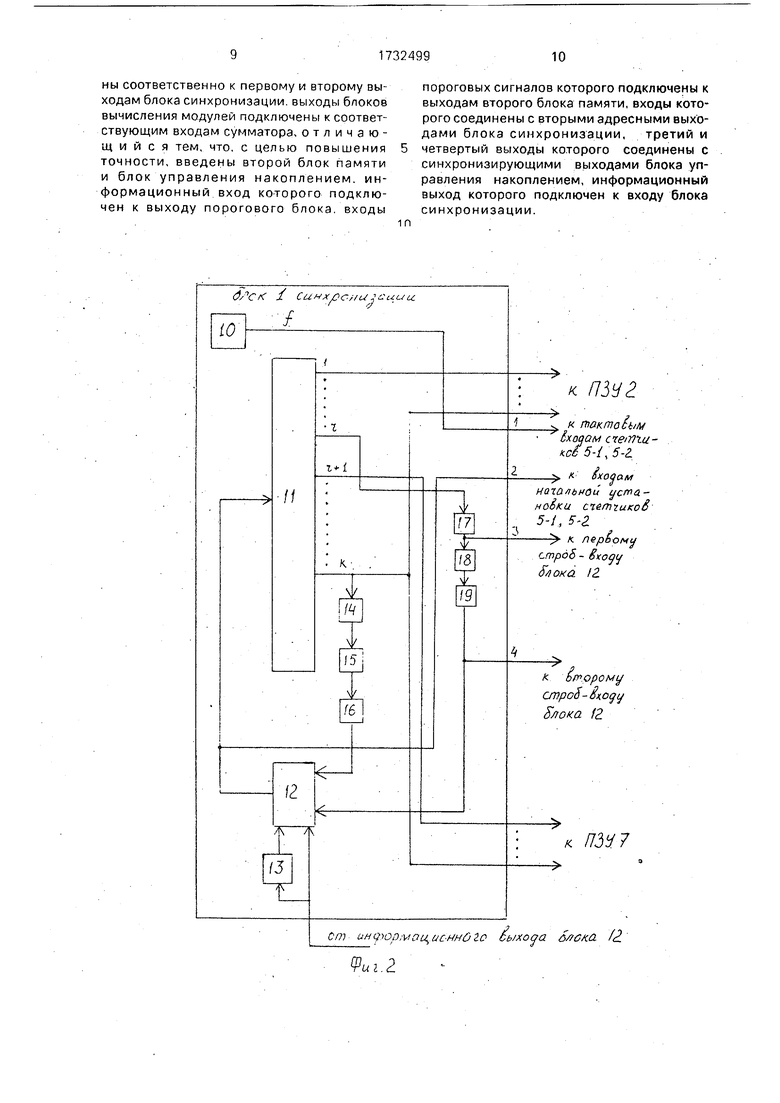

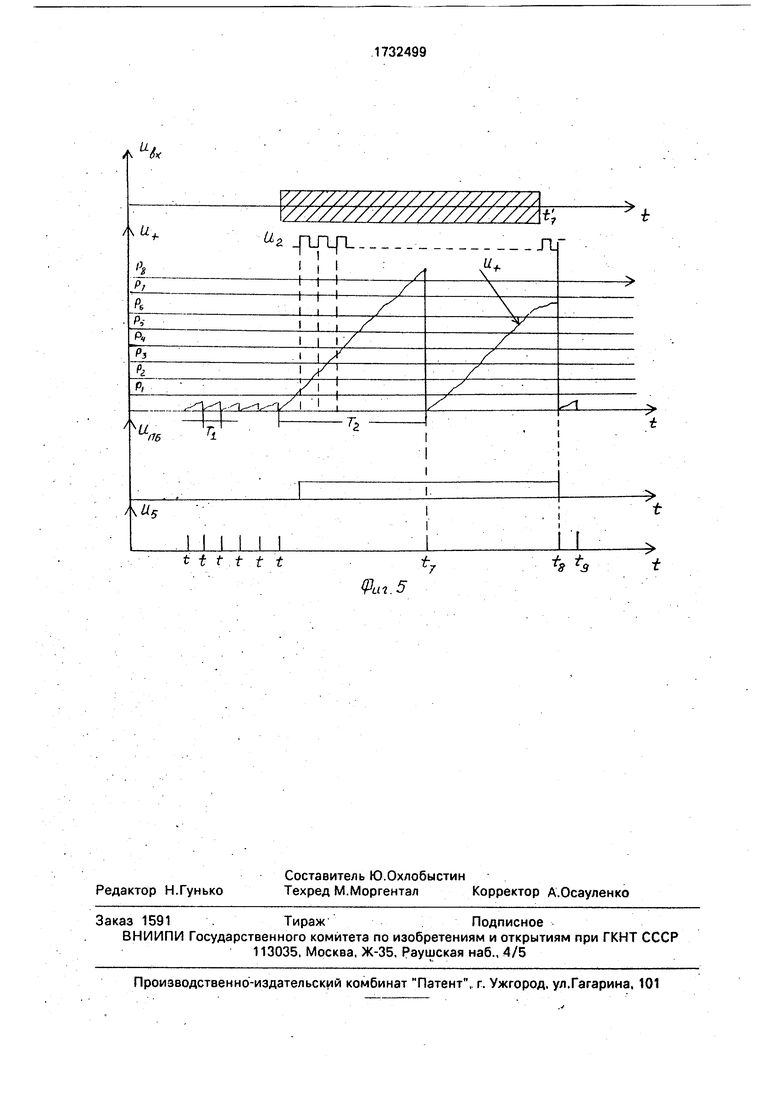

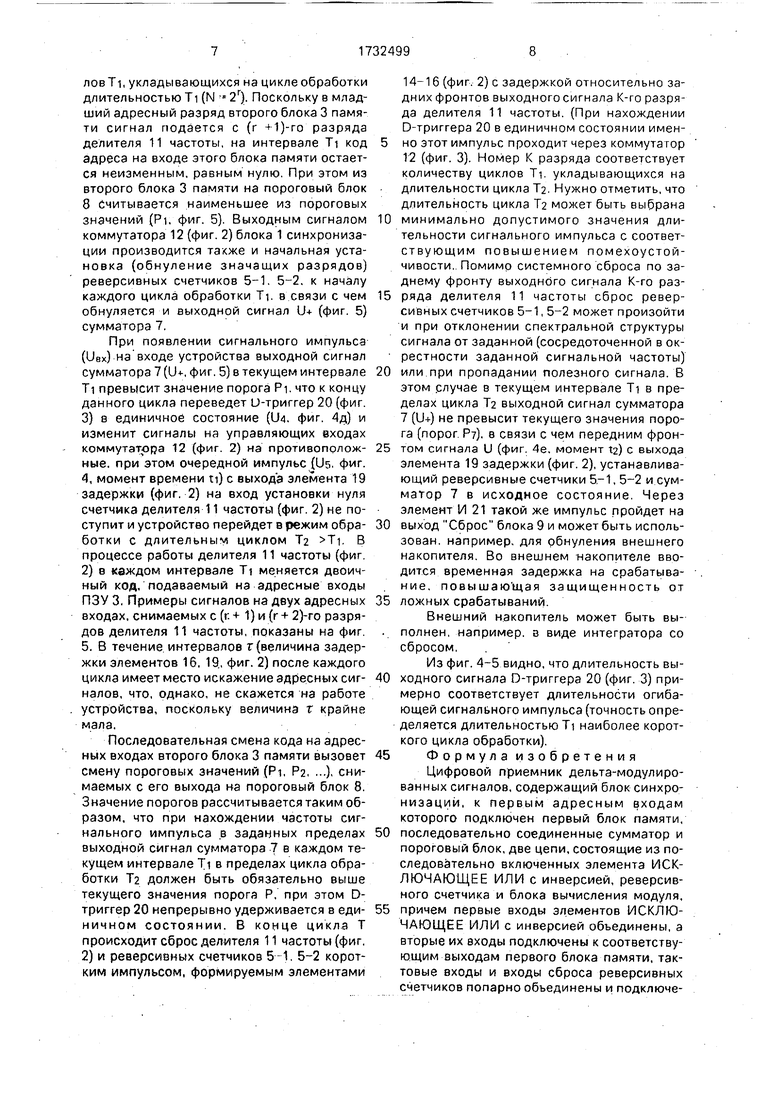

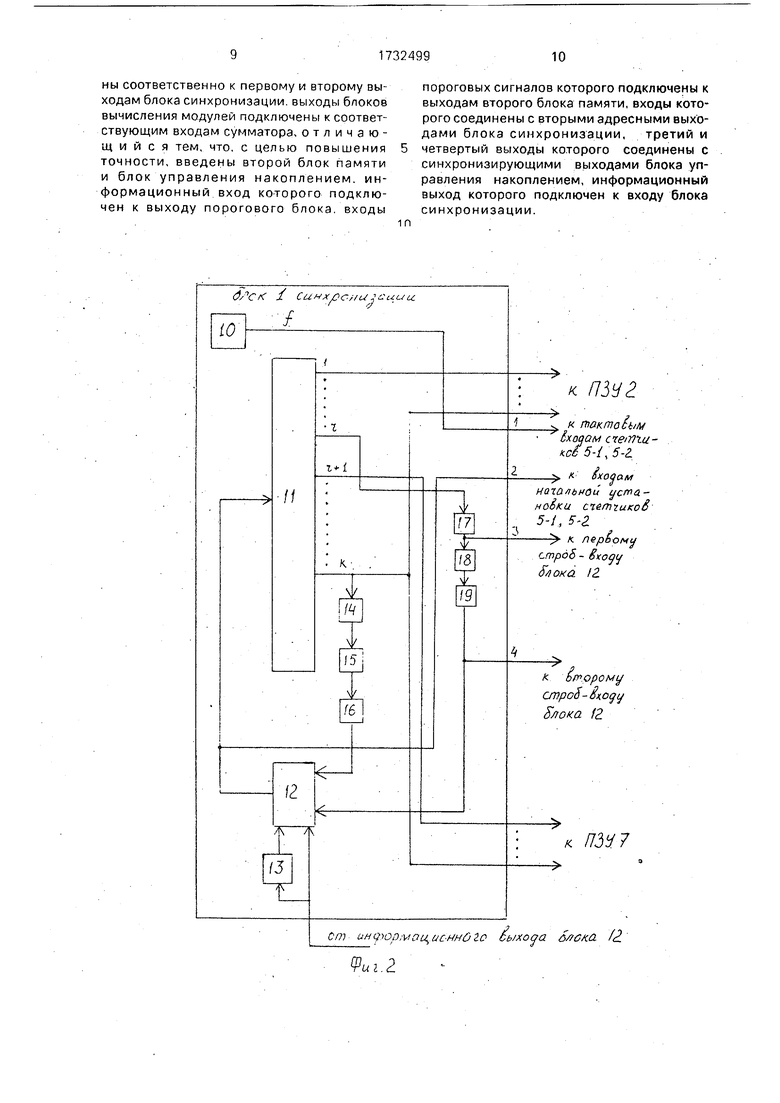

На фиг 1 представлена блок-схема предложенного приемника; на фиг. 2 - блок- схема блока синхронизации; на фиг. 3 - блок-схема блока управления накоплением; на фиг. 4, 5 - временные диаграммы, поясняющие работу устройства.

Цифровой приемник содержит блок 1 синхронизации, первый блок 2 памяти, первый 4-1 и второй 4-2 элементы ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, первый 5-1 и второй 5-2 реверсивные счетчики, второй блок 3 памяти, первый 6-1 и второй 6-2 блоки вычисления модуля, сумматор 7, пороговый блок 8, блок 9 управления накоплением.

Блок 1 синхронизации (фиг 2) содержит тактовый генератор 10, делитель 11 частоты, коммутатор 12, инверторы 13, 14, 17, одно- вибраторы 15, 18 и элементы 16, 19 задержки,

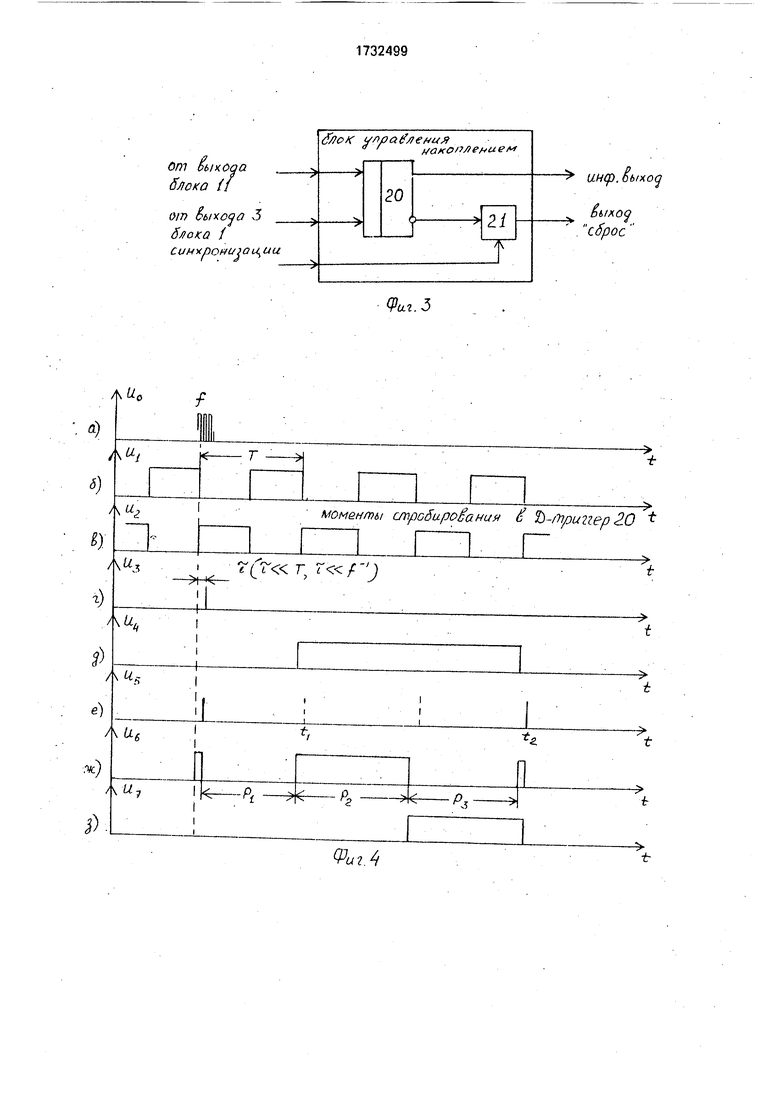

Блок 9 управления накоплением (фиг. 3) содержит D-триггер 20 и элемент И 21.

Предлагаемый цифровой приемник работает следующим образом.

Входной сигнал, преобразованный в цифровую форму с помощью дельта-модуляции с инерционным компандированием, поступает на объединенные вторые входы элементов 4-1 и 4-2 ИСКЛЮЧАЮЩЕЕ ИЛИ инверсией, в,которых происходит перемножение каждого символа X (пТ) дельта-моду- лированного сигнала на одноразрядные весовые коэффициенты, соответствующие значениям знака синусоидального и косину- соидального сигналов с частотой, равной частоте обнаружения.

Значения этих весовых коэффициентов подаются с соответствующих выходов первого блока 2 памяти, адресные сигналы для которого формируются делителем 11 частоты (фиг. 2) в составе блока 1 синхронизации. Выходные сигналы элементов 4-1, 4-2 ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией управляют направлением счета тактовых импульсов реверсивными счетчиками 5-1, 5-2, при этом совпадение логических символов (1 или 0) на входе элемента 4-1 (4-2) ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, соответствующее перемножению величин 1 на 1 или -1 на -1, вызывает увеличение содержимого реверсивных счетчиков 5-1. 5-2 на единицу, а несовпадение - уменьшению на единицу, таким образом к концу цикла обработки длиной Т на выходах реверсивных счетчиков 5-1, 5-2 формируются значения А, В, соответствующие действительной и мнимой составляющим спектрального отсчета на частоте обнаружения.

Приближенное вычисление модуля F спектрального отсчета на частоте f производится в соответствии с выражением F IAI + I В I с помощью сумматора 7 и блоков 6-1, 6-2 вычисления модуля, которые могут быть построены в виде блока управляемых инверторов, к информационных входам которых подключены выходы разрядов 1г-1

соответствующего реверсивного счетчика, а объединенные упраляющие входы соединены с выходом r-го разряда, при этом в момент начальной установки (в начале цикла по сигналу со 2 выхода блока 1 синхронизации) разрядлы 1 г-1 обнуляются, а в г-й

разряд записывается 1, после чего в зависимости от значения r-го разряда к концу цикла выходной код реверсивного счетчика инвертируется (при г 0) либо проходит без инверсии (г 1) на входы сумматора 7.

Таким образом, в устройстве реализуется алгоритм оптимальной некогерентной обработки со следующими приближениями значения весовых коэффициентов квантовались на два уровня а вычисление модуля

0

по формуле F1 А 2 4- В 2 заменено приближенным вычислением по формуле F - IAK IВI, что приводит к сохранению некоторой зависимости результата фильтрациии от фазы сигнала - значение результата может колебаться в пределах, примерно, 3 дБ, что незначительно сказывается на характеристиках устройства. При обработке отсчеты входного дельта-модулированного сигнала учитываются с равным весом, что приводит к эффекту сжатия динамического диапазона на выходе сумматора 7 по сравнению с динамическим диапазоном обрабатываемого сигнала, что эквивалентно действию АРУ, поэтому при фиксированном времени интегрирования в устройстве может быть использован постоянный порог, с которым в пороговом блоке 8 сравнивается выходной сигнал сумматора 7, полоса сра- батывания при этом практически не зависит от уровня обрабатываемого сигнала в широком диапазоне уровней.

Для быстрого распознавания момента начала сигнального импульса, работа уст- 5 ройства до его срабатывания производится с короткими длительностями цикла обработки (Ti). Это обеспечивается следующим образом. Длительность Т ч короткого цикла определяется периодом сигнала на выходе

® одного из разрядов (r-го) делителя 11 частоты блока 1 синхронизации. Этот сигнал показан на фиг. 46 (сигнал Ui). Задним фронтам сигнала Ui соответствуют моменты окончания цикла. Проинвертированный ин- вертором 17 (фиг. 2) сигнал Ui подается на тактовый вход D-триггера 20 (фиг. 3) блока 9 управления накоплением. По передним фронтам этого сигнала (U, фиг. 4в) информация с выхода порогового блока 8 стробиру ется в D-триггер 20 (фиг. 3). Таким образом, при отсутствии срабатывания (при отсутствии полезного сигнала) выходной сигнал UA (фиг. 4д) D-триггера 20 равен нулю. Этот сигнал подается в прямой и инверсной фор- 5 ме на управляющие входы коммутатора 12 (фиг. 2) блока 1 синхронизации, что вызывает поступление через коммутатор 12 на вход установки нуля делителя 11 частоты (фиг. 2) коротких импульсов 11з (фиг. 4г), сформиро ванных с помощью элементов 17-19 (фиг. 2) с задержкой т (т TI) относительно задних фронтов сигнала Ui (фиг. 46), поступающего с выхода г-ro разряда делителя 11 частоты. Таким образом, в конце каждого

5 интервала Ti (фиг. 46) делитель 11 частоты устанавливается в исходное состояние. (Величина г на фиг. 4 показана в увеличенном масштабе времени). Номер разряда г соответствует количеству N тактовых интерваловТ-|, укладывающихся на цикле обработки длительностью Ti (N - 2Г). Поскольку в младший адресный разряд второго блока 3 памяти сигнал подается с (г )-го разряда делителя 11 частоты, на интервале Ti код адреса на входе этого блока памяти остается неизменным, равным нулю. При этом из второго блока 3 памяти на пороговый блок 8 считывается наименьшее из пороговых значений (Pi, фиг. 5). Выходным сигналом коммутатора 12 (фиг. 2) блока 1 синхронизации производится также и начальная установка (обнуление значащих разрядов) реверсивных счетчиков 5-1. 5-2. к началу каждого цикла обработки TI. в связи с чем обнуляется и выходной сигнал U+ (фиг. 5) сумматора 7.

При появлении сигнального импульса (Uex) на входе устройства выходной сигнал сумматора 7 (и, фиг. 5) в текущем интервале Ti превысит значение порога PL что к концу данного цикла переведет и-триггер 20 (фиг. 3) в единичное состояние (LU, фиг. 4д) и изменит сигналы на управляющих входах коммутатора 12 (фиг. 2) на противополож- ные. при этом очередной импульс (Us. фиг.

4,момент времени ti) с выхода элемента 19 задержки (фиг. 2) на вход установки нуля счетчика делителя 11 частоты (фиг. 2) не поступит и устройство перейдет в режим обра- ботки с длительным циклом Та Ti. В процессе работы делителя 11 частоты (фиг

2) в каждом интервале Ti меняется двоичный код, подаваемый на адресные входы ПЗУ 3, Примеры сигналов на двух адресных входах, снимаемых с (г. + 1) и (г + 2)-го разрядов делителя 11 частоты, показаны на фиг

Последовательная смена кода на адресных входах второго блока 3 памяти вызовет смену пороговых значений (Pi, Pa, ...), снимаемых с его выхода на пороговый блок 8. Значение порогов рассчитывается таким образом, что при нахождении частоты сигнального импульса в заданных пределах выходной сигнал сумматора 7 в каждом текущем интервале TI в пределах цикла обработки Та должен быть обязательно выше текущего значения порога Р, при этом D- триггер 20 непрерывно удерживается в еди- ничном состоянии. В конце цикла Т происходит сброс делителя 11 частоты (фиг. 2) и реверсивных счетчиков 5-1. 5-2 коротким импульсом, формируемым элементами

14-16 (фиг. 2) с задержкой относительно задних фронтов выходного сигнала К-го разряда делителя 11 частоты. (При нахождении D-триггера 20 в единичном состоянии именно этот импульс проходит через коммутатор 12 (фиг. 3). Номер К разряда соответствует количеству циклов Ti укладывающихся на длительности цикла Та. Нужно отметить, что длительность цикла Та может быть выбрана минимально допустимого значения длительности сигнального импульса с соответствующим повышением помехоустойчивости. Помимо системного сброса по заднему фронту выходного сигнала К-го разряда делителя 11 частоты сброс реверсивных счетчиков 5-1, 5-2 может произойти и при отклонении спектральной структуры сигнала от заданной (сосредоточенной в окрестности заданной сигнальной частоты) или при пропадании полезного сигнала. В этом .случае в текущем интервале Ti в пределах цикла Та выходной сигнал сумматора 7 (U+) не превысит текущего значения порога (порог Ру). в связи с чем передним фронтом сигнала U (фиг. 4е, момент ta) с выхода элемента 19 задержки (фиг. 2), устанавливающий реверсивные счетчики 5-1, 5-2 и сумматор 7 в исходное состояние. Через элемент И 21 такой же импульс пройдет на выход Сброс блока 9 и может быть использован, например, для обнуления внешнего накопителя. Во внешнем накопителе вводится временная задержка на срабатывание, повышаю щая защищенность от ложных срабатываний.

Внешний накопитель может быть выполнен, например, в виде интегратора со сбросом,

Из фиг. 4-5 видно, что длительность выходного сигнала D-триггера 20 (фиг. 3) примерно соответствует длительности огибающей сигнального импульса (точность определяется длительностью Ti наиболее короткого цикла обработки).

Формула изобретения

Цифровой приемник дельта-модул и ро- ванных сигналов, содержащий блок синхронизации, к первым адресным входам которого подключен первый блок памяти, последовательно соединенные сумматор и пороговый блок, две цепи, состоящие из последовательно включенных элемента ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией, реверсивного счетчика и блока вычисления модуля, причем первые входы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ с инверсией объединены, а вторые их входы подключены к соответствующим выходам первого блока памяти, тактовые входы и входы сброса реверсивных счетчиков попарно объединены и подключены соответственно к первому и второму выходам блока синхронизации выходы блоков вычисления модулей подключены к соответствующим входам сумматора, отличающийся тем, что, с целью повышения точности, введены второй блок памяти и блок управления накоплением, информационный вход которого подключен к выходу порогового блока входы

Cm uHQ- oovctu,ucUHO2c сыхода /2. Фиг 2

пороговых сигналов которого подключены к выходам второго блока памяти, входы которого соединены с вторыми адресными выходами блока синхронизации, третий и четвертый выходы которого соединены с синхронизирующими выходами блока управления накоплением, информационный выход которого подключен к входу блока синхронизации.

К.

/73У2

к так.тоЈъ1М входам сче/пги- «/5-/, 5-г.

бхооам

, а

начальной уста- ноёка ctemtuKoS 5-i, 5-2.

- к. перьому строб- входу $лоха 12.

k Ьгророму строй- S/toxa (2.

/7М7

..э°Ф (ЬНГ)

Ј ir)tb

66frZCiL

Риг 5

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| и др | |||

| Цифровые обнаружители гармонических составляющих для сигналов с адаптивной дельта-модуляцией | |||

| - Электросвязь | |||

| Кузнечная нефтяная печь с форсункой | 1917 |

|

SU1987A1 |

| Способ использования делительного аппарата ровничных (чесальных) машин, предназначенных для мериносовой шерсти, с целью переработки на них грубых шерстей | 1921 |

|

SU18A1 |

Авторы

Даты

1992-05-07—Публикация

1989-06-19—Подача