(Л CZ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления свертки | 1989 |

|

SU1679502A1 |

| Устройство цифровой двумерной свертки | 1988 |

|

SU1647585A1 |

| Устройство для умножения матрицы на вектор | 1990 |

|

SU1737463A1 |

| Устройство для умножения матриц | 1989 |

|

SU1619305A1 |

| Устройство для вычисления свертки | 1988 |

|

SU1587539A1 |

| Устройство для перемножения ленточных матриц | 1990 |

|

SU1774348A1 |

| Устройство для умножения матриц | 1989 |

|

SU1677709A1 |

| Устройство для умножения матриц | 1990 |

|

SU1793446A1 |

| Устройство для вычисления свертки | 1984 |

|

SU1198535A1 |

| Параллельное устройство для вычисления двухмерной свертки | 1985 |

|

SU1269237A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах обработки сигналов для вычисления двумерной свертки. Цель изобретения - повышение быстродействия устройства. Цель достигается параллельно-поточной организацией процесса вычислений в трехмерной матрице I.J.Q вычислительных модулей, где I.J - размерность матрицы-результата

P.Q - размерность "окна свертки". Время вычисления двумерной свертки составляет I+J+P+2Q - 3 тактов, а период вычислений - J+Q-1 такт. 1 з.п. ф-лы, 3 ил.

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах цифровой обработки сигналов для вычисления двумерной свертки.

Цель изобретения - повышение быстродействия.

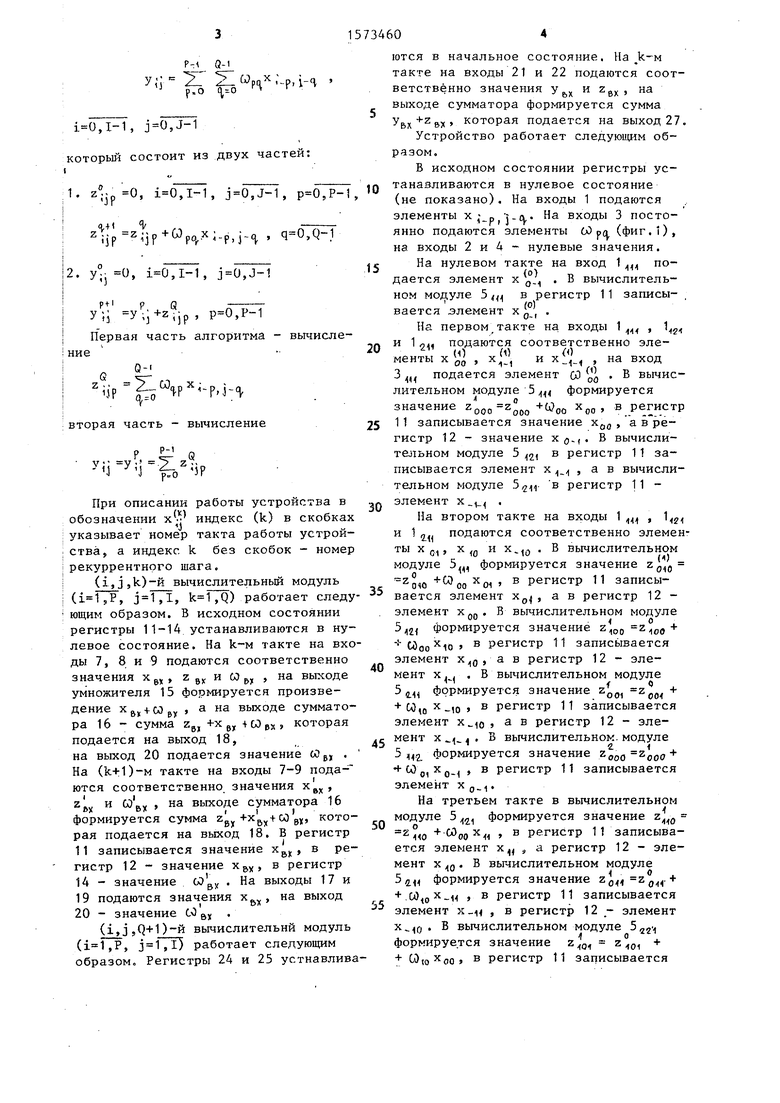

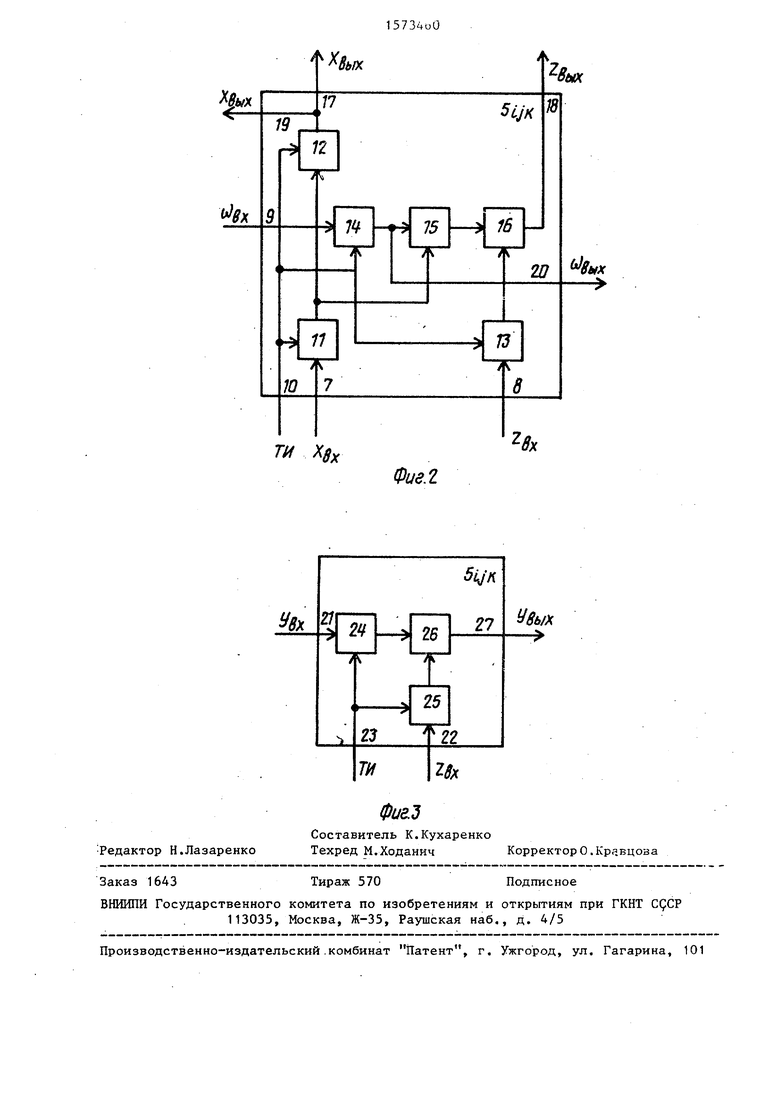

На фиг.1 представлена структурная схема устройства с-потоками входных и выходных данных для вычисления двумерной свертки для случая на фиг.2 - функциональная схема (i, j,k)-ro вычислительного модуля

(,P, j-1,1, k-1,Q)i на фиг.З функциональная схема (i, j ,Q+J)-ro

вычислительного модуля ( ,P, j 1,1) Устройство для вычисления двумерной свертки г(фиг.1) содержит с первой по четвертую группы 1-4 информационных входов, матрицу {i,j,k) (i

1,2, ,2, ,3) вычислительных модулей 5, группу выходов 6, синхро- вход (не показан).

(i,j,k)-ft вычислительнй модуль (i,j,,2) (фиг.2) содержит первый информационный вход 7, второй информационный вход 8, третий информационный вход 9, синхровход 10, регистры 11-14, умножитель 15, сумматор 16, с первого по четвертый выходы 17-20.

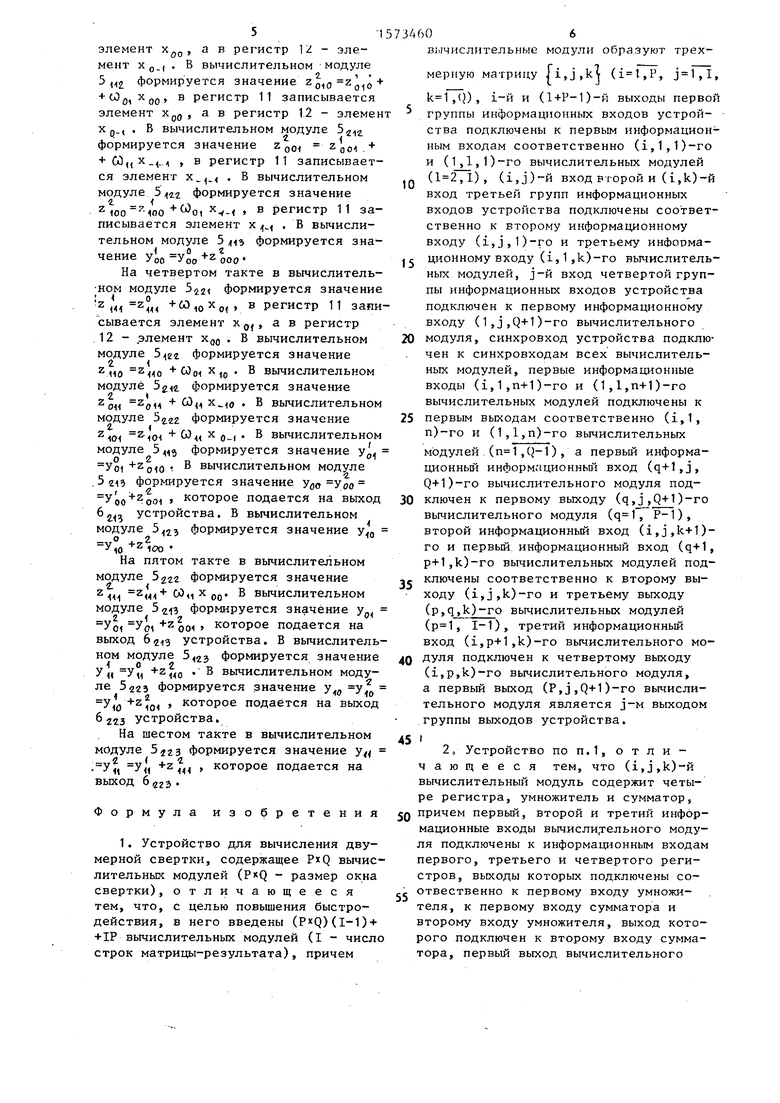

(i,j,Q+1)-ft вычислительный модуль (, , ) (фиг.З) содержит первый 21 и второй 22 информационный входы, синхровход 23, регистры 24 и 25, сумматор 26 и выход 27.

В основу работы устройства положен алгоритм вычисления двумерной свертки

ел

со

4 ОЭ

У

Р-м Q-i p.о t

,I-1, ,J-1 который состоит из двух частей:

о z

1jp 0, ,I-1, j-O.J-1, ,Р-1, О

0.+ 1 V т . .

iip zMp+G3porx-p j

pti

УМ У M+Z«JP

Первая часть алгоритма - вычисление

О .PX;- V

вторая часть - вычисление

Р t1 Q

у v 7 Z

-М УЧ fro ЗР

При описании работы устройства в обозначении х индекс (k) в скобках указывает номер такта работы устройства, а индекс k без скобок - номер рекуррентного шага.

(i,j,k)-и вычислительный модуль (, j , ) работает следующим образом. В исходном состоянии регистры 11-14 устанавливаются в нулевое состояние. На k-м такте на входы 7, 8 и 9 подаются соответственно значения хвх z В)Г и СОМ , на выходе умножителя 15 формируется произведение ХВК + СОБХ , а на выходе сумматора 16 - сумма ZB +x в„ 4 СО „х , которая подается на выход 18, на выход 20 подается значение 00ВХ . На (k+1)-M такте на входы 7-9 пода- ются соответственно значения хм, zL и СО1,,- . на выходе сумматора 16

ЬХD J (| }

формируется сумма zg)( +x5x+co вх, которая подается на выход 18. В регистр 11 записывается значение х, в регистр 12 - значение хьх, в регистр

14 - значение СО

вх

На выходы 17 и

19подаются значения хвх, на выход

20- значение СО вх .

(i,j,Q+1)-й вычислительнй модуль (, ,1) работает следующим образом. Регистры 24 и 25 устнавлива

5

0

5

гатся в начальное состояние. На k-м такте на входы 21 и 22 подаются соответственно значения у и zex, на выходе сумматора формируется сумма yBJ(+zBX которая подается на выход 27.

Устройство работает следующим образом.

В исходном состоянии регистры устанавливаются в нулевое состояние (не показано). На входы 1 подаются элементы х,- „ч.- На входы 3 постоянно подаются элементы СО рп (фиг.1), на входы 2 и 4 - нулевые значения.

На нулевом такте на вход 1 ,,„ подается элемент х ° . В вычислительном модуле 5 щ в регистр 11 записы- . ваетсл элемент х 0 .

На первом такте на входы 1 (М , и 1 2 подаются соответственно элементы х д , х и , на вход 3 м подается элемент СО . В вычислительном модуле 5 4 формируется значение г 000 z°OQ +Q00 x00 , в регистр 1 1 записывается значение хао, а гистр 12 - значение х 0.(. В вычислительном модуле 5 ,,21 в регистр 1 1 записывается элемент х , а в вычислительном модуле 5211 в регистр 11 0

5

0

5

0

5

элемент х

-м

На втором такте на входы 1 1Н1 , и 1 а. подаются соответственно элементы х С1, х (fl и х„10 . В вычислительном модуле 5 формируется значение +Q00 x0, , в регистр 11 записывается элемент х0, а в регистр 12 - элемент х 00. В вычислительном модуле 512 формируется значение z°o0 + Wooхю в РегистР 11 записывается элемент х10, а в регистр 12 - элемент х . В вычислительном модуле 5, формируется значение zj,01 + + W,0x,0, в регистр 11 записывается элемент а в регистр 12 - элемент х . В вычислительном модуле 5 )цг формируется значение zlo0 z1000 +

oix 0-1 в РегистР 11 записывается элемент х 0.,.

На третьем такте в вычислительном модуле 5121 формируется значение ZMQ - +С000х 1 , в регистр 11 записывается элемент х , а регистр 12 - элемент х но. В вычислительном модуле 5 /щ формируется значение ZQ, + + С010х м , в регистр 11 записывается элемент , в регистр 12 - элемент х.10 . В вычислительном модуле 5 формируется значение ( - , + CD,0x00, в регистр 11 записывается

элемент XOD, а в регистр 1/ - элемент х0, . В вычислительном модуле 5 HI формируется значение + + (00, х оо в РегистР 11 записывается элемент хо0, а в регистр 12 - элемен х0, . В вычислительном модуле 521г формируется значение z 00 2001 + + С0(х,, , в регистр 11 записывается элемент х. . В вычислительном модуле Ь i(i.i формируется значение

z uo 7ioo+Cl)oi хч- в Регистр 11 записывается элемент х . В вычислительном модуле 5 щъ формируется значение Уоо Уоо+2оооНа четвертом такте в вычислительном модуле 5г2, формируется значение 2 м z°u + B Регистр 11 записывается элемент х0,, а в регистр 12 - элемент х00 . В вычислительном модуле 5цгг формируется значение 2 но + Woi x,0 . В вычислительном модуле формируется значение z о 20и + В вычислительном модуле 5г22 Формируется значение

2- |

z 1CM z4CM + СО ,,4 x 0( . В вычислительном модуле формируется значение у у°, +z0,0 . В вычислительном модуле 5 формируется значение уоа -у00 уоо+2о и « кот°Р°е подается на выход 6w устройства. В вычислительном модуле 512э формируется значение У°о +z «в

На пятом такте в вычислительном модуле 5ггг формируется значение 2 щ 2ж+ W«iX00. В вычислительном модуле формируется значение ур УО Уо +zoo которое подается на выход 6gi3 устройства. В вычислительном модуле Формируется значение У | УИ +z«o вычислительном модуле 5 225 формируется значение которое подается на выход 62гз устройства.

На шестом такте в вычислительном модуле 5ггз формируется значение у +z «4 которое подается на

ВЫХОД 622Э.

Формула изобретения

0

вычислительные модули образуют трехмерную матрицу Јi,j,k (,P, ,I,

,Q) i-й и (1+Р-1)-й выходы первой группы информационных входов устройства подключены к первым информационным входам соответственно (1,1,1)-го и (1,1,1)-го вычислительных модулей (1 2,1), (i,j)-ft вход второй и (i,k)-u вход третьей групп информационных входов устройства подключены соответственно к второму информационному входу (i,j,1)-ro и третьему информас ционному входу (i, 1 ,k)-го вычислительных модулей, j-й вход четвертой группы информационных входов устройства подключен к первому информационному входу (1,j,Q+1)-ro вычислительного

0 модуля, синхровход устройства подключен к синхровходам всех вычислительных модулей, первые информационные входы (i,1,п+1)-го и (1,1,п+1)-го вычислительных модулей подключены к

5 первым выходам соответственно (1,1, п)-го и (1,1,п)-го вычислительных модулей (,Q-1), а первый информационный информационный вход (q+1,j, Q+1)-ro вычислительного модуля подключен к первому выходу (q,j ,Q+1)-ro вычислительного модуля (, P-1), второй информационный вход (i,j,k+1)- го и первый информационный вход (q+1, p+1,k)-ro вычислительных модулей подключены соответственно к второму выходу (i,j,k)-ro и третьему выходу ()ro вычислительных модулей (, 1-1), третий информационный вход (i,p+1,k)-ro вычислительного модуля подключен к четвертому выходу (i,p,k)-ro вычислительного модуля, а первый выход (P,j,Q+1)-ro вычислительного модуля является j-м выходом группы выходов устройства.

5

2, Устройство поп.1, отличающееся тем, что (i,j,k)-fi вычислительный модуль содержит четыре регистра, умножитель и сумматор, Q причем первый, второй и третий информационные входы вычислительного модуля подключены к информационным входам первого, третьего и четвертого регистров, выходы которых подключены со- отвественно к первому входу умножи0

5

0

5

теля, к первому входу сумматора и второму входу умножителя, выход которого подключен к второму входу сумматора, первый выход вычислительного

Модуля подключен к выходу второго регистра, информационный вход которого йодключен к выходу первого регистра, второй, третий и четвертый выходы вычислительного модуля подключены соответственно к выходам сумматора, второго и четвертого регистров, син- хровход вычислительного модуля подключен к синхровходам всех регистров, A (i,j,Q+1)-u вычислительный модуль Содержит два регистра и сумматор, причем первый информационный вход

5il3

вычислительного модули подключен к информационному входу первого регистра, выход которого подключен к первому входу сумматора, выход которого подключен к выходу вычислительного модуля, второй информационный вход которого подключен к информационному входу второго регистра, выход которого подключен к второму входу сумматора, синхровход вычислительного модуля подключен к синхровходам всех регистров.

, 23

Фие. 1

ти х$х

Фиг. г

| Матричное устройство для вычисления свертки | 1986 |

|

SU1401477A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Kung H.T., Ruane L.M., YenD.W.L | |||

| A two level pipelined systolik array for convolutions | |||

| Proc | |||

| Conf | |||

| on VLSI syst | |||

| and comput., oct | |||

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

| Springer - Verlag, 1981, p.255-264, fig.4. | |||

Авторы

Даты

1990-06-23—Публикация

1988-02-29—Подача