4

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах обра- ботки данных.

Целью изобретения является повышение быстродействия.

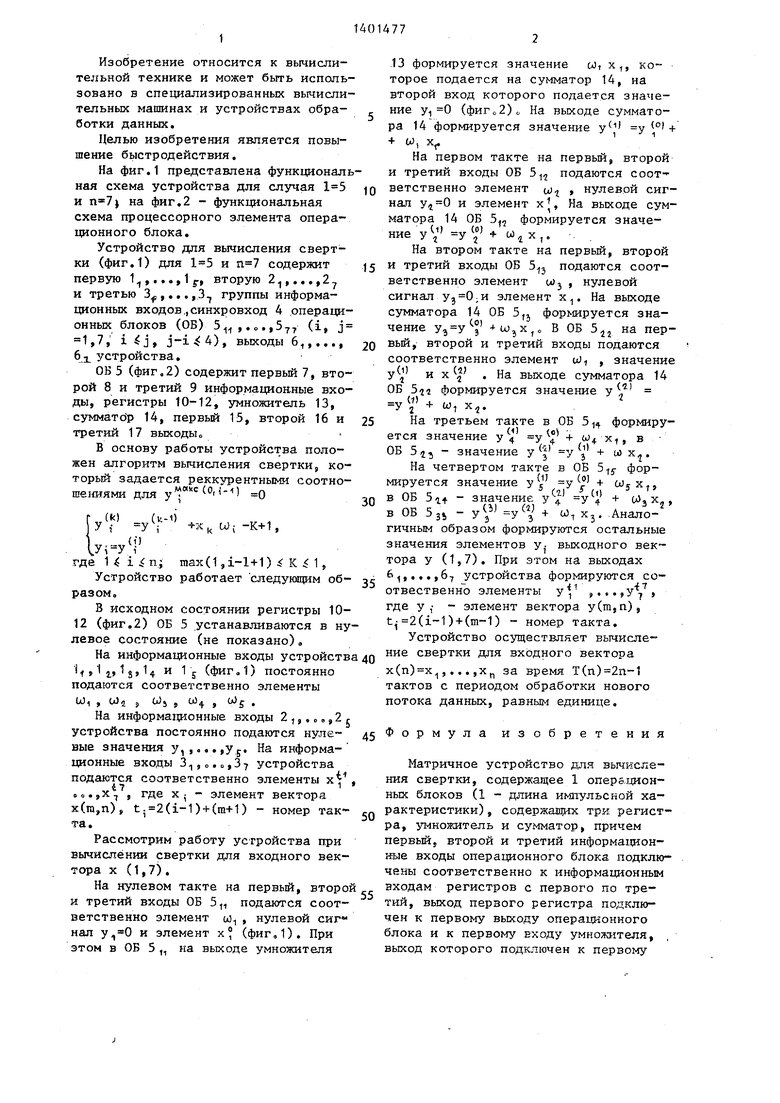

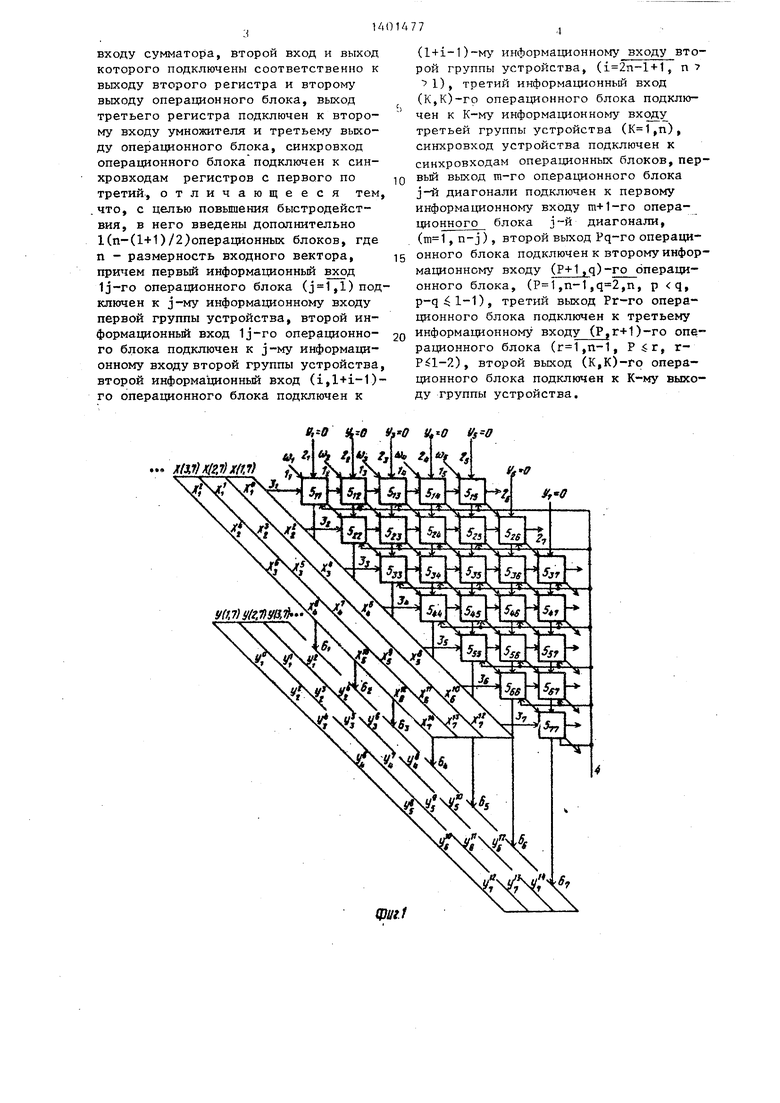

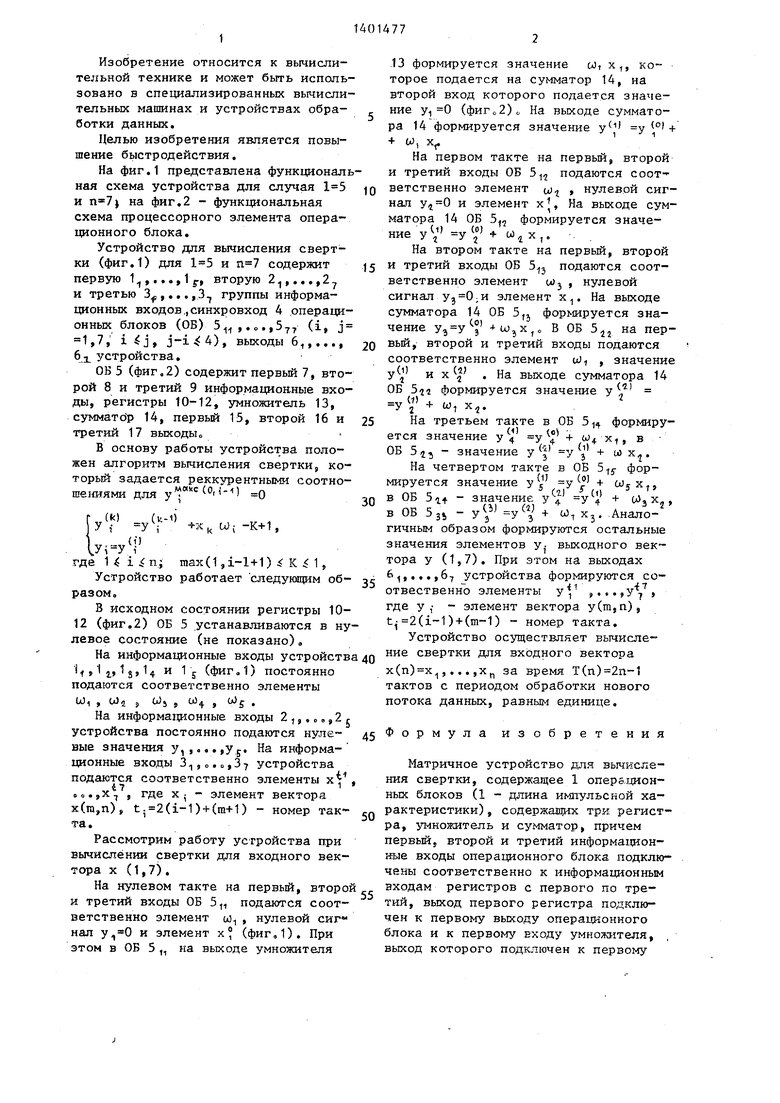

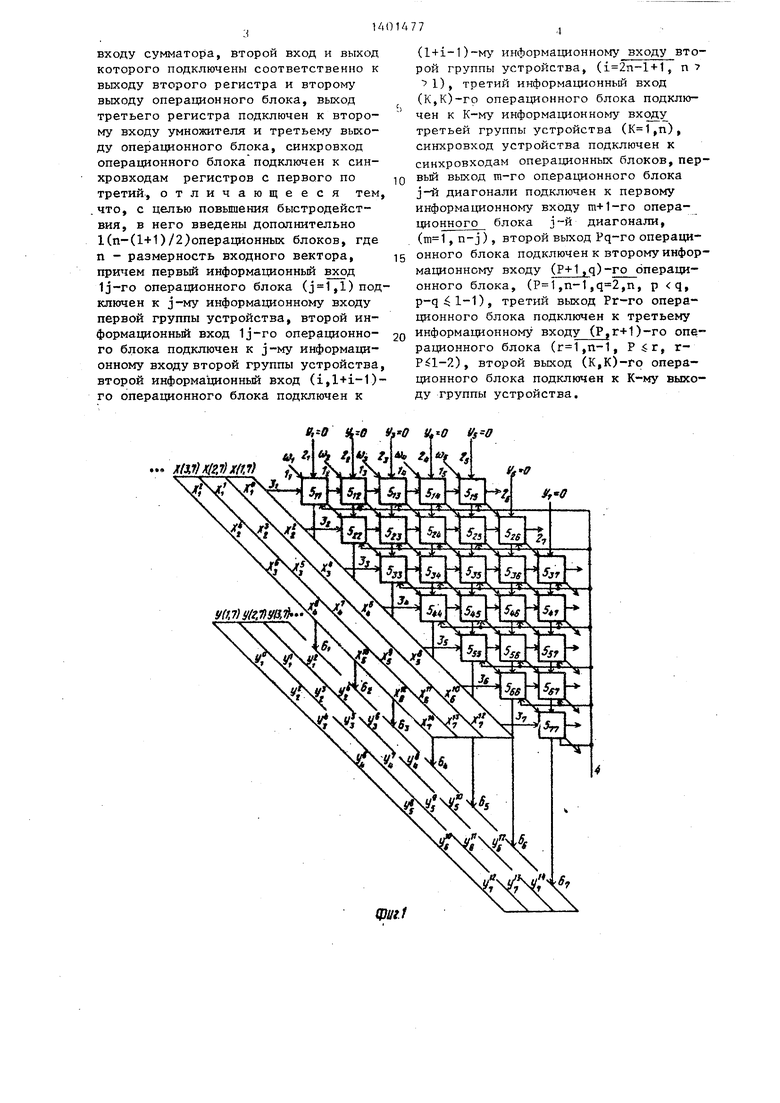

На фиг.1 представлена функциональная схема устройства для случая и на фиг.2 - функциональная схема процессорного элемента операционного блока.

Устройство для вычисления свертки {фиг.1) для и содержит

первую 1,...,1j., вторую 2,2

и третью 3,...,3 группы информационных входов .(Синхровход 4 .операционных блоков (ОБ) 5,.о.,577 (i J 1,7, i j, ), выходы 6,,..., 6-L устройства.

ОБ 5 (фиг.2) содержит первьй 7, второй 8 и третий 9 информационные входы, регистры 10-12, умножитель 13, суммато р 14, первый 15, второй 16 и третий 17 выходЫо

В основу работы устройства положен алгоритм вычисления свертки, который задается реккурентными соотношениями для (o,i-4 0

у7 -х,.1,

где inax(1 ,i-l+1) i К 1,

Устройство работает следующим об- разом.

В исходном состоянии регистры 10- 12 (фиг.2) ОБ 5 устанавливаются в нулевое состояние (не показано)

На информационные входы устройства s (фиг«1) постоянно подаются соответственно элементы

u), , oJj 5 5 5

На информа1щонные входы 2 ,,.„,,2 г устройства постоянно подаются нуле™ вые значения у,,.«.,У5. На информационные входы 3,0.0,37 устройства подаются соответственно элементы х, оо.,х , где Х( - элемент вектора x(ia,n)p (i-1) + (m+1) - номер так та.

Рассмотрим работу устройства при вычислении свертки для входного вектора X (1,7).

На нулевом такте на первьй, второй и третий входы ОБ 5,, подаются соответственно элемент ш , нулевой сиг нал У;,О и элемент х° (фиг,1). При этом в ОБ 5,, на выходе умножителя

.13 формируется значение Wt х,, которое подается на сумматор 14, на второй вход которого подается значение У1 0 (фиГо2)о На выходе сумматора 14 формируется значение у 5, + + W, х

На первом такте на первьй, второй и третий входы ОБ 5, подаются соот ветственно элемент , нулевой сигнал и элемент х. На выходе сумматора 14 ОБ 5|, формируется значение у + Uj с

На втором такте на первьй, второй и третий входы ОБ подаются соответственно элемент W} нулевой сигнал элемент х. На выходе сумматора 14 ОБ 5|j формируется значение з WjX J о В ОБ на первьй, второй и третий входы подаются соответственно элемент tJ , значение

.0)

ОБ формируется значение у

и X Ч . На выходе сумматора 14

{4}

У 1

+ Ш. Хл.

5

0

На третьем такте в ОБ 5 формируется значение у ;J у ° + w+ х, в ОБ - значение у У j + ш к.

На четвертом такте в ОБ формируется значение yv у г + Ыг х

tn I ,

,Ci) „(t)

i

s

0

5 Q

в ОБ 5 It значение у у V + j в ОБ 5 з«, - У Аналогичным образом формируются остальные значения элементов у,- выходного вектора у (1,7). При этом на выходах ,...,б7 устройства формируются со- отвественно элементы у, ...У7 где у,- - элемент вектора y(mjn), (1-1 ) + (m-1) - номер такта.

Устройство осзгществляет вычисление свертки для входного вектора

х(п) за время Т(п)2п-1

тактов с периодом обработки нового потока данных, равным единице.

Формула изобретения

Матричное устройство для вычисления свертки, содержащее 1 оперб.цион- ньк блоков (1 - длина импульсной характеристики) , содержащих три регистра, у1-1ножитель и сумматор, причем первьй, второй и третий информационные входы операционного блока подключены соответственно к информационным входам регистров с первого по третий, выход первого регистра подключен к первому выходу операционного блока и к первому входу умножителя, , выход которого подключен к первому

входу сумматора, второй вход и выход которого подключены соответственно к выходу второго регистра и второму выходу операционного блока, выход третьего регистра подключен к второму входу умножителя и третьему выходу операционного блока, синхровход операционного блока подключен к син- хровходам регистров с первого по третий, отличающееся тем, .что, с целью повышения быстродействия, в него введены дополнительно 1(п-(1+1)/2)операцнонных блоков, где п - размерность входного вектора, причем первый информационный вход 1j-ro операционного блока (j 1,l) подключен к j-му информационному входу первой группы устройства, второй ин- формационньй вход 1j-ro операционного блока подключен к j-му информационному входу второй группы устройства, второй информационньй вход (1,1+1-1)- го операционного блока подключен к

5

0

(1+1-1)му информационному входу вто- рой группы устройства, (i 2n-l- -1, п 1), третий информационньй вход (К,К)-го операционного блока подключен к К-му информационному входу третьей группы устройства (,п), синхровход устройства подключен к синхровходам операционных блоков, пер- вьм выход га-го операционного блока j-й диагонали подключен к первому инфopмaциoннo y входу m+1-ro опера- ционного блока й диагонали, (, n-j), второй выход Pq-ro операционного блока подключен к второму информационному входу (Р+1,д)-го операци- онного блока, (,п-1,,n, р q, ), третий выход Рг-го операционного блока подключен к третьему информационному входу (Р,г+1)-го операционного блока (,п-1, Р $г, г- ), второй вькод (К,К)-го операционного блока подключен к К-му выходу группы устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления деконволюции | 1987 |

|

SU1494017A1 |

| Устройство для вычисления свертки | 1989 |

|

SU1679502A1 |

| Матричное устройство для вычисления свертки | 1987 |

|

SU1494018A1 |

| Устройство для матричных операций | 1987 |

|

SU1429127A1 |

| Устройство для разложения теплицевых симметричных матриц | 1990 |

|

SU1755295A2 |

| Устройство для вычисления двумерного дискретного преобразования Фурье | 1990 |

|

SU1751778A1 |

| Устройство для умножения матрицы на вектор | 1990 |

|

SU1737463A1 |

| Устройство для вычисления двумерной свертки | 1988 |

|

SU1573460A1 |

| Устройство для вычисления свертки | 1988 |

|

SU1587539A1 |

| Устройство для операций над матрицами | 1989 |

|

SU1777153A1 |

Изобретение относится к вычислительной технике и может быть ис пользовано в специализированных вычислительных машинах и устройствах обработки данных. Целью изобретения является повьшение быстродействия. Устройство содержит матрицу операционных блоков (ОБ), каждьй из которых содержит три регистра, умножитель и сумматор. Поставленная цель достигается за счет организации рациональной структуры связей между ОБ, что позволяет осуществлять параллельную свертку входных последовательностей. 2 ил.

m7)xfz7)jfff.7)

ff,-0 Уз О /,U ф. Ф /.

фаг.1

Ч

12

1

8

5d

//

77

75

X

/5

фиг. г

| Дифференциальный манометр для измерения перепада давления, расхода и скорости газового потока | 1949 |

|

SU85520A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Kung N.T | |||

| Why systolic architectures - Computer, 1982, ff 1, p.42, fig.8. | |||

Авторы

Даты

1988-06-07—Публикация

1986-12-01—Подача