Изобретение относится к вычислительной технике и может быть использовано для обработки двумерных массивов большой размерности.

Целью изобретения является расти - рение области применения за счет возможности применения для обработки аэрокосмических изображений.

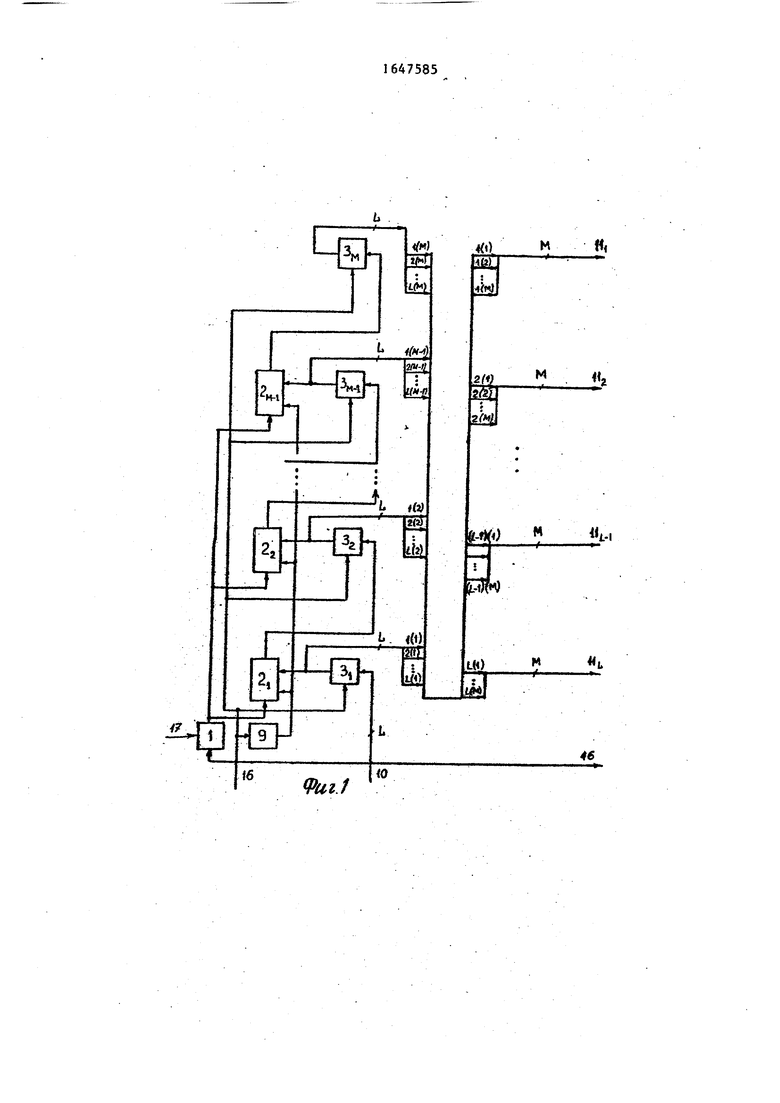

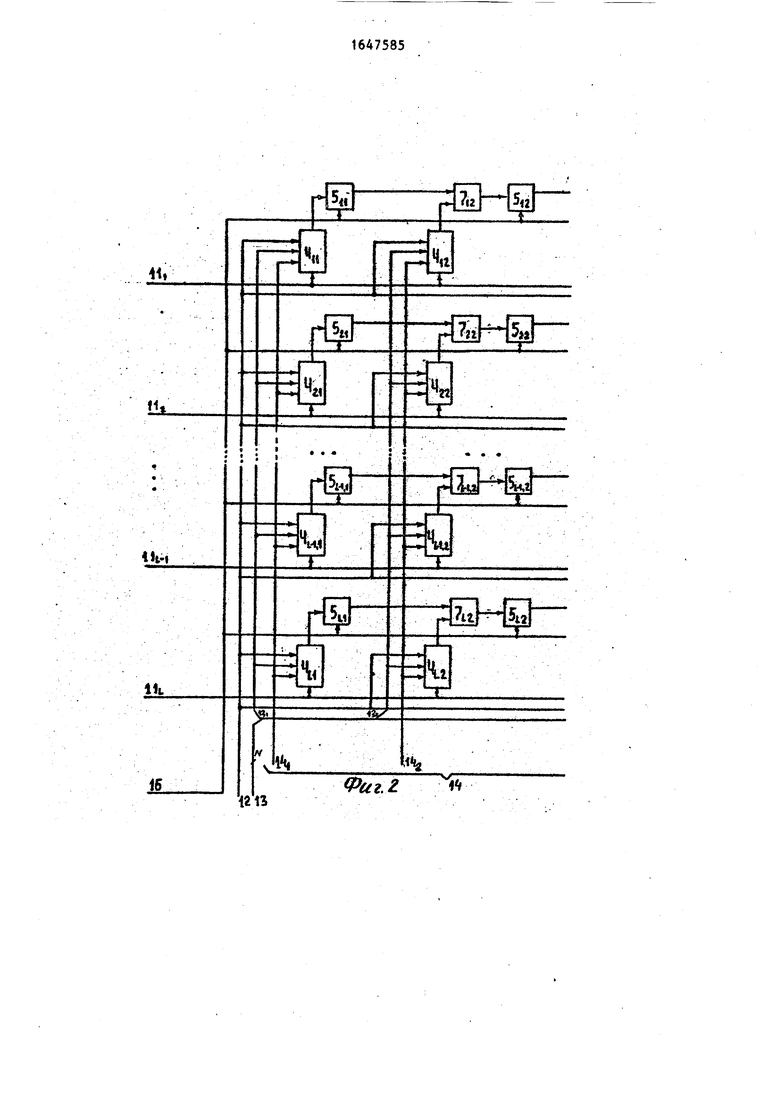

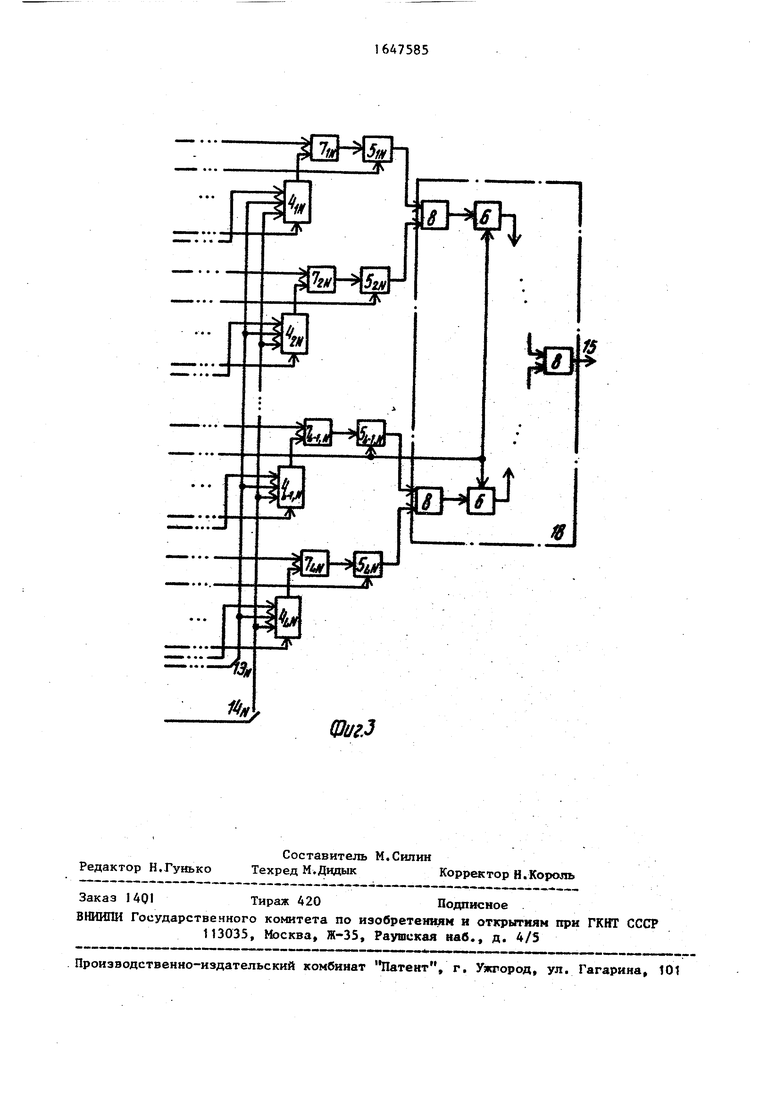

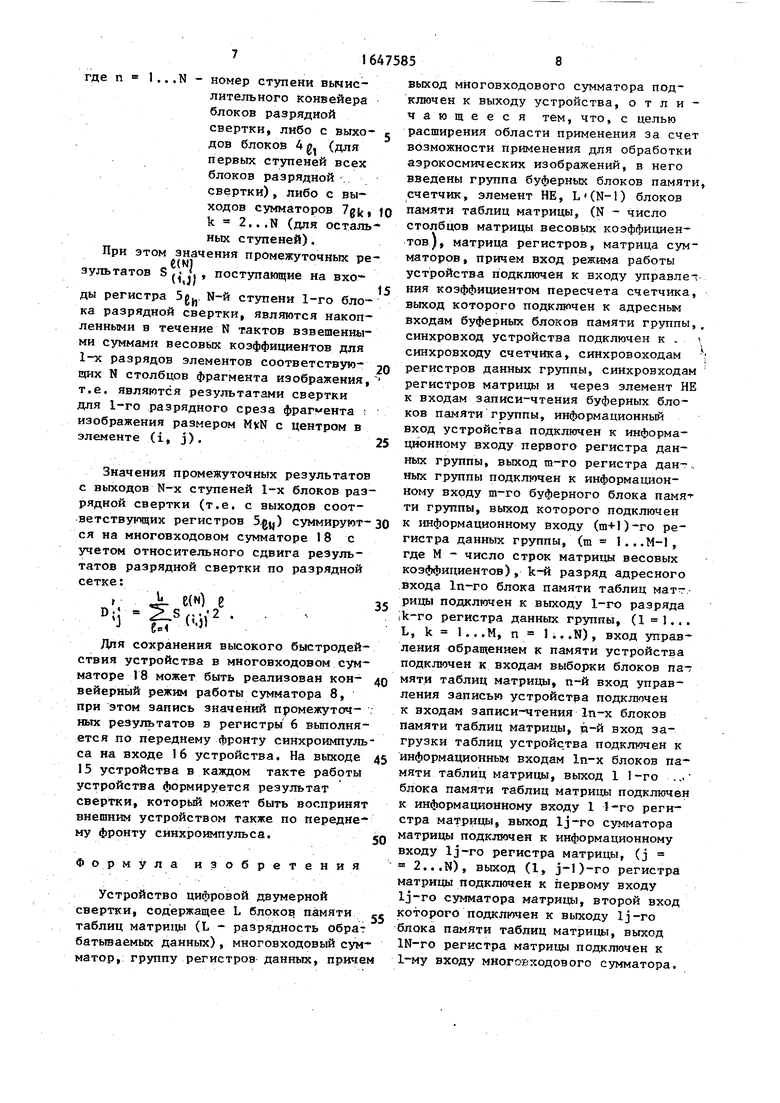

На фиг.1-3 представлена функциональная схема устройства.

Устройство содержит счетчик 1, группу буферных блоков ..памяти, группу регистров Sf-S данных, матри- .цу блоков 4gft памяти таблиц (1 1... L, n 1 .. .N) , матрицу регистров 5(1 1...L, n 1...N), регистры 6, матрицу сумматоров 7рк(1 1...L, К я 2...N), сумматоры 8, элемент НЕ 9, информационный вход 10, шины По (1

1...L) разрядных срезов, вход 12 управления обращением к памяти устройства, группу входов 13 управления записью устройства, группу входов 14 загрузки таблиц, выход 15 устройства, синхровход 16 устройства, вход 17 режима работы устройства, многовходовый сумматор 18,

Вычисление свертки в устройстве осуществляется на основе использования таблиц взвешенных сумм весовых коэффициентов, которые формируются следующим образом: М

- т-

VA

&

|

сл

00

ел

где .}.. ,ал - индекс (адрес)

элемента таблицы;

абЈО,1,Wу,- весовые коэффициенты свертки (т 1...М, п 1 ...

N);5

М - число строк; N - число столбцов матрицы весовых коэффициентов ,

Каждая из N таблиц содержит взве- ю шенные суммы коэффициентов одного из столбцов (n-го столбца) матрицы весовых коэффициентов. Каждое из табличных значений таблиц является суммой (представленной в дополнительном ко- 15 де) тех весовых коэффициентов столб- ,ца матрицы весовых коэффициентов, которые соответствуют единичным значениям двоичных цифр а индекса А табчений адресов, а блок 2 - второй разряд всех значений адресов.

Порядок изменения адресов, формируемых на шинах J1, определяется порядком чередования констант 000,..0 и I11 ... 1 . Для формирования последовательности адресов в порядке возрастания от 0 до в блок 2мнпамяти загружается массив (последовательность) констант, состоящий из 2 констант OOQ...O и следующих за ними

МИ

констант I11...1. В блок 2.

константы загружаются следующим образом: 2 констант 000...О, 2 констант П1..Л, констант 000.. .0 и, наконец, 2 гконстант 111...1, в блок 2 константы загружаются полями по две константы,начиная с констант

лицы. Для каждой таблицы индекс А 000...0. Таким образом, в блок 2- памяти (т 1...М-1).записывается массив из 2 L-разрядных констант.

ледовательно. принимает все значения от 0 до 2 . При этом в устройстве

h

состоящий из подмассивов длиной 2 констант, начиная с подмассива, состоящего из констант 000„.0.

25

одновременно используются N разных таблиц T.J., каждая из которых загружается параллельно в L блоков памяти таблиц (L - разрядность элементов изображения),

Устройство работает под управлением некоторого внешнего устройства, например управляющей мини-ЭВМ, входящей в зо состав измерительно-вычислительного комплекса.

Работа устройства осуществляется в двух режимах: режиме загрузки таблиц и режиме вычисления.

Загрузка таблиц выполняется при каждом изменении ядра свертки. Для загрузки таблиц необходимо последовательно сформировать на адресных входах блоков А рп все возможные значения . индексов (адресов) таблиц, определенным образом упорядоченные (например, по возрастанию), и для каждого эначеh

35

сос тоящий из подмассивов длиной 2 кон стант, начиная с подмассива, состоя щего из констант 000„.0.

Для записи констант в блоки 2 4.. 2 w счетчик 1 сигналом на входе 17 устройства переводится в режим счета по модулю, равному 2 . Предваритель ная установка счетчика 1 в начальное состояние не производится, так как счетчик работает в циклическом режи ме.

Константы поступают из внешнего устройства в устройство через информационный вход 10. В каждом такте очередная константа записывается в регистр 3 4 по переднему фронту синхроимпульса (СИ). Одновременно в ре гистры 3 Ј.. .3 записываются констан ты, считываемые из блоков 2...2М памяти (блоки 2.. , находятся в режиме чтения, так как на входе управления записью этих блоков сохрани

50

ния индекса (адреса) сформировать на

входах данных блоков 4gn соответству- ется сигнал 1). Затем блоки 2,...

ющие табличные значения в сопровожде- 2w.fпамяти переходят в режим записи

нии необходимых сигналов управления

записью данных.

С целью формирования заданной последовательности адресов на адресных входах блоков 4еп (т.е. на шинах tig разрядных срезов) в блоки 2 .. . загружаются из внешнего устройства специальные наборы констант 000...О и Н 1 ... 1. При этом блок 2 м, памяти содержит старший М-й разряд всех 2 значений адресов, последовательно формируемых на шинах 11. Блок 2,г памяти содержит (М-1)-и разряд всех зна,55

с задержкой, длительность которых оп ределяется временем переключения эле мента НЕ 9, относительно переднего фронта СИ - и данные из регистров 3||...3w-} записываются в блоки 2.. 2 м-1 т.е. выполняется сдвиг (переда ча) констант относительно блоков 2j.. .2/u-t.

Содержимое счетчика I изменяется по заднему фронту СИ, так как задерж ка переключения счетчика больше за держки элемента НЕ 9, блоки 2 памяти переходят в режим считывания раньше

чений адресов, а блок 2 - второй разряд всех значений адресов.

Порядок изменения адресов, формируемых на шинах J1, определяется порядком чередования констант 000,..0 и I11 ... 1 . Для формирования последовательности адресов в порядке возрастания от 0 до в блок 2мнпамяти загружается массив (последовательность) констант, состоящий из 2 констант OOQ...O и следующих за ними

МИ

констант I11...1. В блок 2.

константы загружаются следующим образом: 2 констант 000...О, 2 констант П1..Л, констант 000.. .0 и, наконец, 2 гконстант 111...1, в блок 2 константы загружаются полями по две константы,начиная с констант

000...0. Таким образом, в блок 2- памяти (т 1...М-1).записывается массив из 2 L-разрядных констант.

0 000...0. Таким образом, в блок 2- памяти (т 1...М-1).записывается массив из 2 L-разрядных констант.

5

о

.

h

35

состоящий из подмассивов длиной 2 констант, начиная с подмассива, состоящего из констант 000„.0.

Для записи констант в блоки 2 4... 2 w счетчик 1 сигналом на входе 17 устройства переводится в режим счета по модулю, равному 2 . Предварительная установка счетчика 1 в начальное состояние не производится, так как счетчик работает в циклическом режиме.

Константы поступают из внешнего устройства в устройство через информационный вход 10. В каждом такте очередная константа записывается в регистр 3 4 по переднему фронту синхроимпульса (СИ). Одновременно в регистры 3 Ј.. .3 записываются константы, считываемые из блоков 2...2М памяти (блоки 2.. , находятся в режиме чтения, так как на входе управления записью этих блоков сохрани0

2w.fпамяти переходят в режим записи

5

с задержкой, длительность которых определяется временем переключения элемента НЕ 9, относительно переднего J фронта СИ - и данные из регистров 3||...3w-} записываются в блоки 2... i 2 м-1 т.е. выполняется сдвиг (передача) констант относительно блоков 2j.. .2/u-t.

Содержимое счетчика I изменяется по заднему фронту СИ, так как задержка переключения счетчика больше задержки элемента НЕ 9, блоки 2 памяти переходят в режим считывания раньше,

чем изменится адрес на их адресных входах.

Цикл записи одного массива констант состоит из 2 тактов. В первом цикле на информационный вход I0 из внешнего устройства поступают константы, которые по окончании процесса ввода должны размещаться в блоке 2W.(. После выполнения М-1 циклов ввода (и передачи между блоками 2) констант устройство готово к формированию последовательности адресов.

Формирование адресов блоков 4 и запись в блоки 4 табличных значений выполняются во время М-го цикла работы счетчика 1. Одновременно со считыванием данных из первой по счету ячейки всех блоков 2 памяти и записью этих данных в регистры 3. ..Змв регистр 3, записывается константа 000...О, поступающая из внешнего устройства на информационный вход 10. 1-е (1 1... L) разрядные срезы констант на выходах регистров Здц. ..3,) образуют L M- разрядных адресов (М-й разряд - старший) для L блоков разрядной свертки, каждый из которых содержит N блоков 4. Так как все разряды каждой

0

реключается (сигналом на входе 17 устройства) в режим счета по модулю I (где I - длина строки обрабатываемого изображения), Затем начинается загрузка из внешнего устройства эпемен- тов изображения, формируемых с помощью построчной (телевизионной) развертки. Элементы изображения поступают на вход 10. В течение М-1 циклов по I тактов каждой в блоки 2.{ ...2,, памяти вводятся М-1 строк изображения, состоящих из I элементов.

С начала ввода элементов М-й стро5 ки в каждом такте на выходы регистров 3M...3j поступают М элементов очередного столбца локального фрагмента изображения. На шинах 11 разрядных - срезов Нормируются L-разрядных срезов этого столбца, которые поступают на адресные входы соответствующих блоков 4, т.е. 1-й разрядный срез (1 1... L) столбца элементов изображения является адресом всех блоков 4gM 1-го

5 блока разрядной свертки. Каждый блок разрядной свертки объединяет блоки 4g- памяти таблиц (п ....N), регистры Sgy, (n - 1...N) и сумматоры 7дь , k 2...N с одинаковыми индексами

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления свертки | 1985 |

|

SU1297073A1 |

| Генератор символов | 1987 |

|

SU1550572A1 |

| Устройство для реализации временных булевых функций | 1985 |

|

SU1290346A1 |

| Устройство для обмена информацией в мультипроцессорной вычислительной системе | 1988 |

|

SU1571594A1 |

| Устройство для обнаружения и исправления ошибок | 1990 |

|

SU1837293A1 |

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1992 |

|

RU2042209C1 |

| Устройство для обнаружения и исправления ошибок в кодовой последовательности | 1984 |

|

SU1238078A1 |

| Табличный процессор | 1982 |

|

SU1108446A1 |

| Устройство для обработки видеоинформации | 1990 |

|

SU1732354A1 |

Изобретение отностися к вычислительной технике и может быть использовано для обработки двумерных массивов большой размерности. Целью изобретения является расширение области применения за счет возможности применения для обработки аэрокосмических изображений. Устройство содержит счетчик, группу буферных блоков памяти, группу регистров данных, матрицу блог ков памяти таблиц, матрицу регистров, регистры, матрицу сумматоров, суммат торы, элемент НЕ, информационный вход,| шины разрядных срезов, входы и выходы устройства, многовходовый сумматор. Поставленная цель достигается введег-i нием новых элементов и связей. 3 ил. I

константы одинаковы, одновременно 1(1 1«««L) и является вычислительвсех блоков 4 формируются одинаковые адреса.

В следующем такте одновременно со

ным конвейером для вычисления свертки по одному (1-му) разрядному срезу.

М-

считыванием констант из блоков 2 2ц на вход 10 из внешнего устройства поступает константа 111 ... 1 и соответственно на шинах Н.... 11 формируются адреса 00...01. Таким образом, в цикле формирования адресов на вход 10 устройства из внешнего устройства подаются поочередно константы 000...О и 1 11 ... 1 , образующие младший разряд адресов блоков 4.

Для каждого значения адресов выполняется запись табличных значений во все блоки 4. При этом на входе 12 установлен активный уровень, а на входы 14{...I 4од загрузки таблиц поступают табличные значения. Запись каждого табличного значения выполняется одно- временно в L блоков 4р(1 1...L, k const) под управлением сигнала записи на соответствующем входе 13}(.

После загрузки табличных значений по всем адресам блоков 4 устройство переводится в режим вычисления свертки. При этом блоки 4 переводятся в режим чтения с помощью соответствующего сигнала на входах 13, а счетчик 1 пе

ным конвейером для вычисления свертки по одному (1-му) разрядному срезу.

Одновременно с разрядными срезами очередного столбца фрагмента изображения подается сигнал обращения к па- мяти на вход 12 устройства, по которому в каждой из N ступеней каждого .. из L блоков разрядной свертки выполняется считывание из блоков 4 g« соответствующей адресу (т.е. разрядному срезу столбца фрагмента изображения) суммы весовых коэффициентов

2 (...М

(фе

т

fo,i).

По переднему фронту синхроимпуль- са на входе 16 устройства в регистры 5gft записываются значения промежуточных результатов:

,efr)

(M1

л. ek

b .j-fN+o/z+k)

где п

,N - номер ступени вычислительного конвейера блоков разрядной свертки, либо с выходов блоков 4g, (для первых ступеней всех блоков разрядной свертки), либо с вывыход многовходового сумматора под ключен к выходу устройства, отл чающееся тем, что, с целью расширения области применения за с возможности применения для обработ аэрокосмических изображений, в нег введены группа буферных блоков пам счетчик, элемент НЕ, L (N-l) блоко

ходов сумматоров 7g|, JQ памяти таблиц матрицы, (N - число

k 2...N (для остальных ступеней).

При этом значения промежуточных ре- S

зультатов

поступающие на вхо

i,J)

ды регистра 5 N-й ступени 1-го блока разрядной свертки, являются накопленными в течение N тактов взвешенными суммами весовых коэффициентов для 1-х разрядов элементов соответствующих N столбцов фрагмента изображения, т.е. являются результатами свертки для 1-го разрядного среза фрагмента изображения размером MyN с центром в элементе (i, j).

15

20

25

столбцов матрицы весовых коэффицие тов), матрица регистров, матрица с маторов , причем вход режима работы устройства подключен к входу управ ния коэффициентом пересчета счетчи выход которого подключен к адресны входам буферных блоков памяти груп синхровход устройства подключен к синхровходу счетчика, синхровохода регистров данных группы, синхровхо регистров матрицы и через элемент к входам записи-чтения буферных бл ков памяти группы, информационный вход устройства подключен к информ ционному входу первого регистра да ных группы, выход m-го регистра да ных группы подключен к информацион ному входу m-го буферного блока па ти группы, выход которого подключе

Значения промежуточных результатов с выходов N-x ступеней 1-х блоков разрядной свертки (т.е. с выходов соответствующих регистров 5) суммируют-30 к информационному входу (ш+1)-го ре35

ся на многовходовом сумматоре 1 8 с учетом относительного сдвига результатов разрядной свертки по разрядной сетке:

t - е(0 е .

Для сохранения высокого быстродействия устройства в многовходовом сумматоре 18 может быть реализован кон- до вейерный режим работы сумматора 8, при этом запись значений промежуточных результатов в регистры 6 выполняется по переднему фронту синхроимпульса на входе 16 устройства. На выходе д5 15 устройства в каждом такте работы устройства формируется результат свертки, который может быть воспринят внешним устройством также по переднему фрОНТу СИНХрОИМПуЛЬСа,JQ

Формула изобретения

гистра данных группы, (m 1...M-1, где М - число строк матрицы весовых коэффициентов), k-й разряд адресного входа ln-го блока памяти таблиц матрицы подключен к выходу 1-го разряда k-ro регистра данных группы, (1 1.. L, k 1...М, п 1..,N), вход управления обращением к памяти устройства подключен к входам выборки блоков памяти таблиц матрицы, n-й вход управления записью устройства подключен к входам записи-чтения ln-х блоков памяти таблиц матрицы, ti-й вход загрузки таблиц устройства подключен к информационным входам ln-х блоков памяти таблиц матрицы, выход 1 I -го ... блока памяти таблиц матрицы подключен к информационному входу 1 1-го регистра матрицы, выход lj-го сумматора матрицы подключен к информационному входу lj-го регистра матрицы, (j 2...N), выход (1, j-l)-ro регистра матрицы подключен к первому входу lj-го сумматора матрицы, второй вход которого подключен к выходу lj-го блока памяти таблиц матрицы, выход Ш-го регистра матрицы подключен к 1-му входу многовходового сумматора.

Устройство цифровой двумерной свертки, содержащее L блоков памяти таблиц матрицы (L - разрядность обрат батываемых данных), многовходовый сумматор, группу регистров данных, причем

выход многовходового сумматора подключен к выходу устройства, отличающееся тем, что, с целью расширения области применения за счет возможности применения для обработки аэрокосмических изображений, в него введены группа буферных блоков памяти, счетчик, элемент НЕ, L (N-l) блоков

памяти таблиц матрицы, (N - число

столбцов матрицы весовых коэффициентов), матрица регистров, матрица сумматоров , причем вход режима работы устройства подключен к входу управления коэффициентом пересчета счетчика, выход которого подключен к адресным входам буферных блоков памяти группы, , синхровход устройства подключен к . синхровходу счетчика, синхровоходам регистров данных группы, синхровходам регистров матрицы и через элемент НЕ к входам записи-чтения буферных блоков памяти группы, информационный вход устройства подключен к информационному входу первого регистра данных группы, выход m-го регистра данных группы подключен к информационному входу m-го буферного блока памя ти группы, выход которого подключен

к информационному входу (ш+1)-го ре

гистра данных группы, (m 1...M-1, где М - число строк матрицы весовых коэффициентов), k-й разряд адресного входа ln-го блока памяти таблиц матрицы подключен к выходу 1-го разряда k-ro регистра данных группы, (1 1... L, k 1...М, п 1..,N), вход управления обращением к памяти устройства подключен к входам выборки блоков памяти таблиц матрицы, n-й вход управления записью устройства подключен к входам записи-чтения ln-х блоков памяти таблиц матрицы, ti-й вход загрузки таблиц устройства подключен к информационным входам ln-х блоков памяти таблиц матрицы, выход 1 I -го ... блока памяти таблиц матрицы подключен к информационному входу 1 1-го регистра матрицы, выход lj-го сумматора матрицы подключен к информационному входу lj-го регистра матрицы, (j 2...N), выход (1, j-l)-ro регистра матрицы подключен к первому входу lj-го сумматора матрицы, второй вход которого подключен к выходу lj-го блока памяти таблиц матрицы, выход Ш-го регистра матрицы подключен к 1-му входу многовходового сумматора.

V

им

7,2

| Устройство для цифровой фильтрации | 1985 |

|

SU1381541A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Mimaroglu T | |||

| A high speed two-dimensional hardware convolver for image processing | |||

| Машина для разделения сыпучих материалов и размещения их в приемники | 0 |

|

SU82A1 |

| Conf., Las Vegas, c.386-389, фиг | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1991-05-07—Публикация

1988-08-16—Подача