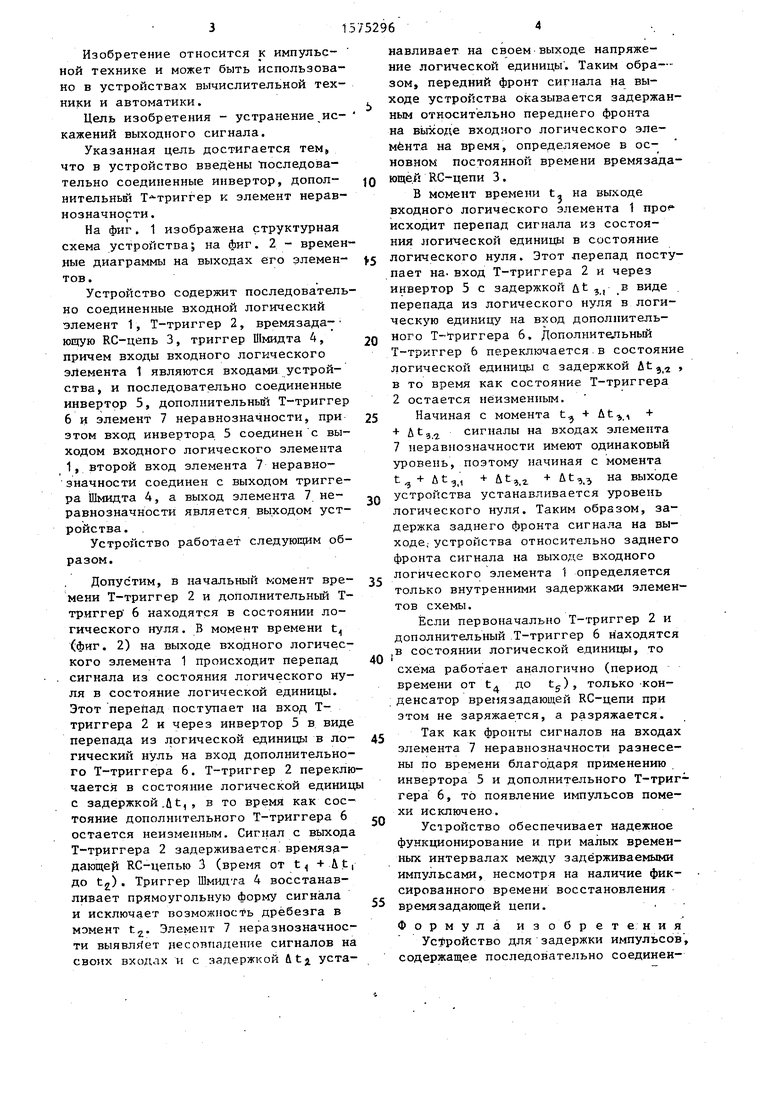

Фиг. 1

Изобретение относится к импульсной технике и может быть использовано в устройствах вычислительной техники и автоматики.

Цель изобретения - устранение ис- кажений выходного сигнала.

Указанная цель достигается тем, что в устройство введены последовательно соединенные инвертор, допол- нительный Т-триггер к элемент неравнозначности.

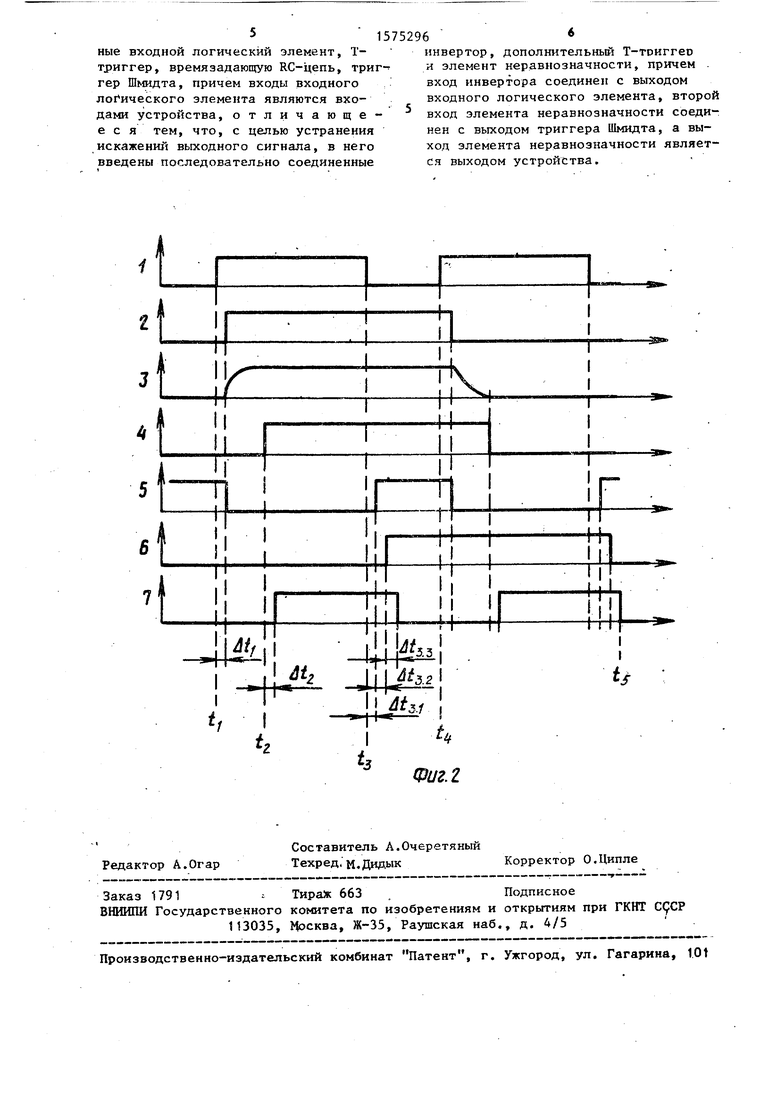

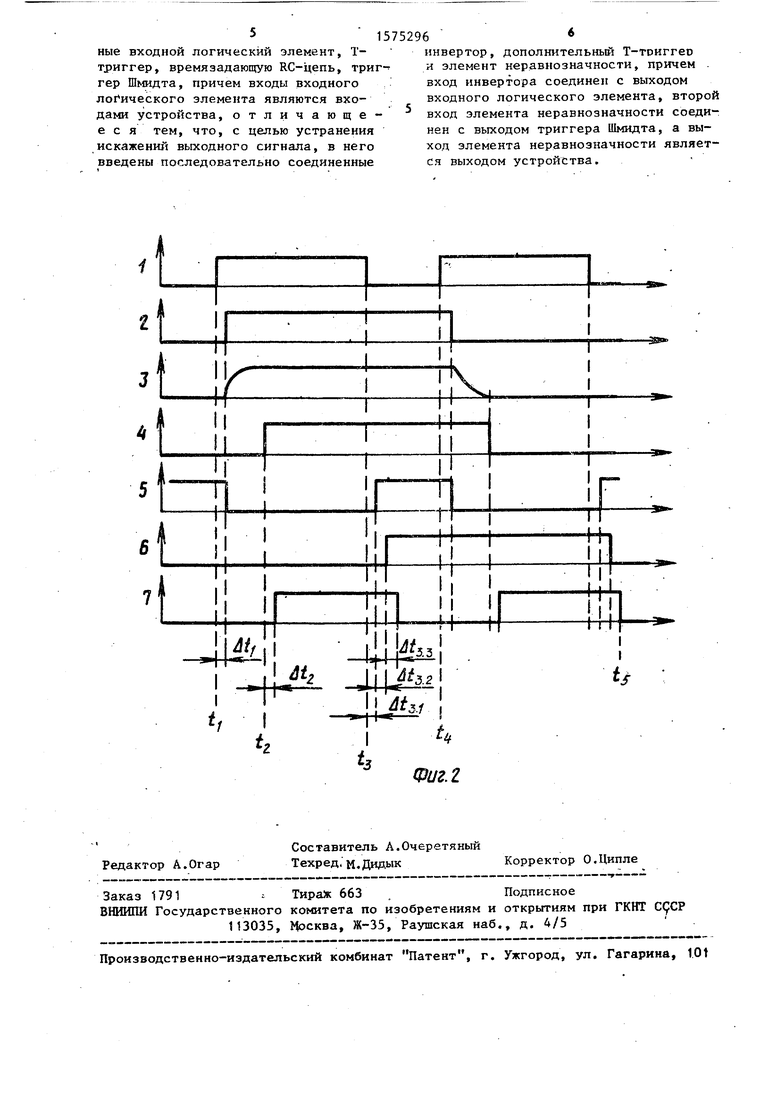

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - временные диаграммы на выходах его элемен- тов.

Устройство содержит последовательно соединенные входной логический элемент 1, Т-триггер 2, времязада- ющую RC-цепь З, триггер Шмидта 4, причем входы входного логического элемента 1 являются входами устройства , и последовательно соединенные инвертор 5, дополнительный Т-триггер 6 и элемент 7 неравнозначности, при этом вход инвертора 5 соединен с выходом входного логического элемента 1, второй вход элемента 7 неравнозначности соединен с выходом триггера Шмидта 4, а выход элемента 7 не- равнозначности является выходом устройства.

Устройство работает следующим образом.

Допустим, в начальный момент вре- мени Т-триггер 2 и дополнительный Т- триггер 6 находятся в состоянии логического нуля. В момент времени t,, (фиг. 2) на выходе входного логического элемента 1 происходит перепад сигнала из состояния логического нуля в состояние логической единицы. Этот перепад поступает на вход Т- триггера 2 и через инвертор 5 в виде перепада из логической единицы в ло- гический нуль на вход дополнительного Т-триггера 6. Т-триггер 2 переключается в состояние логической единиц с задержкой ftt,, в то время как состояние дополнительного Т-триггера 6 остается неизменным. Сигнал с выхода Т-триггера 2 задерживается времяза- дающер RC-цепью 3 (время от t + At, до tg). Триггер Шмидга 4 восстанавливает прямоугольную форму сигнала и исключает возможность дребезга в момент Г2. Элемент 7 неравнозначности выявляет несовпадение сигналов на своих входах и с задержкой ut устанавливает на своем выходе напряжение логической единицы. Таким обра- зом, передний фронт сигнала на выходе устройства оказывается задержанным относительно переднего фронта на выходе входного логического элемента на время, определяемое в основном постоянной времени времязада ющей RC-цепи З.

В момент времени t, на выходе входного логического элемента 1 исходит перепад сигнала из состояния логической единицы в состояние логического нуля. Этот -перепад поступает на- вход Т-триггера 2 и через инвертор 5 с задержкой ut в виде перепада из логического нуля в логическую единицу на вход дополнительного Т-триггера 6. Дополнительный Т-триггер 6 переключается в состояни логической единицы с задержкой At в то время как состояние Т-триггера 2 остается неизменным.

Начиная с момента t + At, + + At за сигналы на входах элемента 7 неравнозначности имеют одинаковый уровень, поэтому начиная с момента At3i, + At,i + At ,53 на выходе устройства устанавливается уровень логического нуля. Таким образом, задержка заднего фронта сигнала на выходе, устройства относительно заднего фронта сигнала на выходе входного логического элемента 1 определяется только внутренними задержками элементов схемы.

Если первоначально Т-триггер 2 и дополнительный Т-триггер 6 находятся в состоянии логической единицы, то

схема работает аналогично (период времени от t до t5), только конденсатор времязадающей RC-цепи при этом не заряжается, а разряжается.

Так как фронты сигналов на входах элемента 7 неравнозначности разнесены по времени благодаря применению инвертора 5 и дополнительного Т-триггера 6, то появление импульсов помехи исключено.

Усчройство обеспечивает надежное функционирование и при малых временных интервалах между задерживаемыми импульсами, несмотря на наличие фиксированного времени восстановления времязадающей цепи.

Формула изобретения

Устройство для задержки импульсов содержащее последовательно соединенные входной логический элемент, Т- триггер, времязадающую RC-цепь, триггер Шмидта, причем входы входного логического элемента являются входами устройства, отличающееся тем, что, с целью устранения искажений выходного сигнала, в него введены последовательно соединенные

инвертор, дополнительный Т-тоиггео и элемент неравнозначности, причем

вход инвертора соединен с выходом входного логического элемента, второй вход элемента неравнозначности соединен с выходом триггера Шмидта, а выход элемента неравнозначности является выходом устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Одновибратор | 1979 |

|

SU809502A1 |

| Устройство для задержки импульсов | 1986 |

|

SU1348988A1 |

| Устройство задержки | 1978 |

|

SU790214A1 |

| Многоканальный датчик одиночных импульсов | 1984 |

|

SU1223353A1 |

| Преобразователь отклонения частоты от номинального значения в аналоговый сигнал | 1982 |

|

SU1084694A1 |

| Ждущий мультивибратор | 1978 |

|

SU782134A1 |

| Формирователь импульсов | 1981 |

|

SU993453A1 |

| Ждущий мультивибратор | 1986 |

|

SU1432735A2 |

| Устройство определения временного положения импульсных сигналов | 1988 |

|

SU1596301A1 |

| Устройство преобразования напряжения в интервал времени | 1984 |

|

SU1228285A1 |

Изобретение может быть использовано в вычислительной технике и автоматике. Цель изобретения - устранение искажений выходного сигнала - достигается за счет введения в состав устройства инвертора 5, дополнительного T-триггера 6, элемента неравнозначности 7 и новых связей. Кроме того, в состав устройства входят входной логический элемент 1, T-триггер 2, времязадающая RC-цепь 3, триггер Шмидта 4. Введенные отличия исключают появление импульсов помех на выходе устройства, так как фронты импульсов на входах элемента неравнозначности 7 разнесены во времени. Устройство обеспечивает надежное функционирование и при малых временных интервалах между задерживаемыми импульсами - меньших, чем фиксированное время восстановления времязадающей RC-цепи 3. 2 ил.

3

Фиг. 2

| Авторское свидетельство СССР № , кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для задержки импульсов | 1986 |

|

SU1348988A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1990-06-30—Публикация

1988-08-05—Подача